Fターム[5F110HK24]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層に含まれる不純物 (1,114)

Fターム[5F110HK24]の下位に属するFターム

Fターム[5F110HK24]に分類される特許

1 - 9 / 9

半導体装置の製造方法

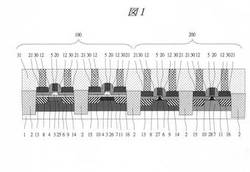

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

微結晶シリコン膜及びその作製方法、並びに半導体装置

【課題】結晶性の高い微結晶シリコン膜を作製する方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により第1の微結晶シリコン膜57をプラズマCVD法で形成し、第1の微結晶シリコン膜上に、第2の条件により第2の微結晶シリコン膜59を形成し、第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第2の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、堆積性気体の流量に対する水素の流量を100倍以上2000倍以下にして堆積性気体を希釈し、且つ処理室内の圧力を1333Pa以上13332Pa以下とする条件である。

(もっと読む)

薄膜トランジスタ及びその製法

【課題】 一対のソース・ドレイン電極上の酸化物半導体薄膜層の結晶性を良好にし、リーク電流の増大、電流駆動能力の低下、電流律速を抑制した、高いTFT特性を有する薄膜トランジスタ及びその製法を提供する。

【解決手段】 基板上に間隙を有して形成される一対のソース・ドレイン電極4と、チャネルとして形成される酸化亜鉛を主成分とする酸化物半導体薄膜層5と、該酸化物半導体薄膜層が形成される下地膜3を有する薄膜トランジスタであって、前記下地膜3が、該一対のソース・ドレイン電極上で、且つ、該一対のソース・ドレイン電極4夫々における上側表面の一部の領域を被覆しないように形成され、前記酸化物半導体薄膜層5が該下地膜3上に形成され、且つ該一対のソース・ドレイン電極4における該一部の領域4aと接していることを特徴とする薄膜トランジスタである。

(もっと読む)

半導体装置およびその作製方法

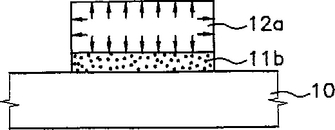

【課題】ZnO半導体膜を用い、ソース電極及びドレイン電極にn型又はp型の不純物を添加したZnO膜を用いたときでも欠陥や不良が生じない半導体装置及びその作製方法を提供する。

【解決手段】ゲート電極3上の酸化珪素膜又は酸化窒化珪素膜からなるゲート絶縁膜5と、前記ゲート絶縁膜上のAl膜又はAl合金膜11aと、前記Al膜又はAl合金膜11a上のn型又はp型の不純物が添加されたZnO膜11bと、前記n型又はp型の不純物が添加されたZnO膜11b上及び前記ゲート絶縁膜5上のZnO半導体膜13とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース、ドレインおよびチャネルが同導電型で構成されたトランジスタにおいて、ソース−ドレイン間の導通を良好に遮断する。

【解決手段】半導体装置100は、半導体基板102上にBOX層110およびSOI層106がこの順で形成されたSOI基板と、SOI層106に形成された第1導電型のドレイン領域106aおよび106bと、これらの間に設けられた第1導電型のチャネル領域106cと、チャネル領域106c上に形成されたゲート絶縁膜112およびその上に形成された第1のゲート電極114とを含む。チャネル領域106cの下方にドープトシリコンまたは金属からなる導電層108がSOI層106の膜厚よりも狭い間隔で設けられる。また、チャネル領域106cと導電層108との間にBOX層110が設けられる。

(もっと読む)

薄膜積層基板、及びその製造方法、並びに薄膜積層基板を備える液晶表示装置

【課題】平坦化膜の下層にある第1導電部と、平坦化膜の上層にある第2導電部とが電気的に接続されてショートすることを抑制する薄膜積層基板等を提供すること。

【解決手段】本発明に係る薄膜積層基板は、基板1上に凹凸パターン表面が形成された平坦化膜10を備え、その下層に複数の第1導電部(2、3等)を、その上層に第2導電部(11、12)を有する薄膜積層基板50であって、第1導電部(2、3等)の凸状部が形成されている領域で、かつその上層に第2導電部(11、12)を備える領域の内、薄膜トランジスタ形成領域A及び配線と交差する領域Bを外して、平坦化膜10表面の凹凸パターンが形成されている。

(もっと読む)

LCDのTFT基板及びその製造方法

【課題】 液晶表示装置の薄膜トランジスタ基板及びその製造方法が開示されている。

【解決手段】 シリコン元素を含む基板、前記基板上に形成された拡散防止膜、及び前記拡散防止膜上に形成され、前記拡散防止膜形成物質が0.5〜15at%範囲で含まれた銅合金層を含んで形成される。前記拡散防止膜は、Zr、Ti、Hf、V、Ta、Ni、Cr、Nb、Co、Mn、Mo、W、Rh、Pd、Pt等のような化合物を50〜5000Å範囲で蒸着して熱処理して、シリサイド化合物に変換して製造する。銅合金配線を用いてトランジスタ基板を製造するので、低い抵抗と高い伝導度を具現することができる。又、薄い厚さの拡散防止膜と同じ元素を添加した銅合金と用いて銅配線を形成したので、同時エッチングが可能であり、後続工程で基板との相互拡散を防止することができる。  (もっと読む)

(もっと読む)

集積回路およびその製造方法

【課題】 ポリマー系有機半導体材料を用いたp型FETを用いて実用的集積回路を構成できるようにすること。

【解決手段】 集積回路を構成するトランジスタとしてp型FETのみを用いたものである。基本回路の例として(a)インバーター回路、(b)AND回路、(c)OR回路を示す。同図において、1〜12はp型FETである。p型FETだけで構成し、出力部にもp型FETのみを用いたソースフォロワ回路を用いたアナログアンプも可能である。

(もっと読む)

1 - 9 / 9

[ Back to top ]