Fターム[5F110HK31]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 低抵抗層の製法 (10,751)

Fターム[5F110HK31]の下位に属するFターム

堆積 (8,750)

不純物の導入 (89)

シリサイド化 (743)

低抵抗層形成前の処理 (380)

低抵抗層形成後の処理 (709)

Fターム[5F110HK31]に分類される特許

1 - 20 / 80

集積装置

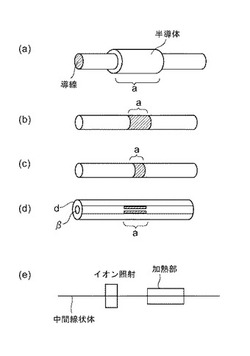

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、更にソース線を削減することにより単位面積あたりの記憶容量を増加させる。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

薄膜トランジスタアレー基板、薄膜集積回路装置及びそれらの製造方法

【課題】TFT特性が良好で表示品質や回路配線の層間絶縁性を確保できるTFTアレー基板の製造方法等を提供する。

【解決手段】基材1上への酸化物半導体膜3のパターン形成工程、酸化物半導体膜へのソース電極接続領域3s及びドレイン電極接続領域3dの形成工程、酸化物半導体膜を覆うゲート絶縁膜4の形成工程、ゲート絶縁膜にコンタクトホールを開けてソース電極6s及びドレイン電極6dをソース電極接続領域及びドレイン電極接続領域に接続するとともに酸化物半導体膜上にゲート絶縁膜を介してゲート電極7を形成し、第1回路配線群17を形成する工程、ソース電極、ドレイン電極、ゲート電極及び第1回路配線群上に層間絶縁膜18を形成する工程、層間絶縁膜上に第2回路配線群19を形成する工程を有し、ゲート絶縁膜4の厚さを100nm〜500nmの範囲とし、層間絶縁膜18の厚さを1μm以上且つゲート絶縁膜4の2倍〜10倍の厚さとする。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

半導体デバイス及びその製造方法

【課題】本発明は、良質な酸化物半導体のチャネル領域と、チャネル領域の抵抗率よりも低い抵抗率でソース・ドレイン領域にも適用可能な低抵抗領域とが形成され、オン電流、キャリア移動度及び信頼性が高く、ヒステリシス性が小さい良好な電気特性を、工程数を増やすことなく実現できる半導体デバイス及びその製造方法を提供することを目的とする。

【解決手段】酸化物半導体をチャネル材料に用いた半導体デバイスの製造方法であって、

薄膜領域21と、該薄膜領域よりも膜厚の厚い厚膜領域22、23とを有する酸化物半導体膜20を形成する工程と、

前記酸化物半導体膜にエネルギービームを照射し、前記薄膜領域と前記厚膜領域の抵抗率を膜厚に応じて変化させる工程と、

前記薄膜領域をチャネル領域21aとし、前記厚膜領域を低抵抗領域22a、23aとして前記半導体デバイスを形成する工程と、を有することを特徴とする。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

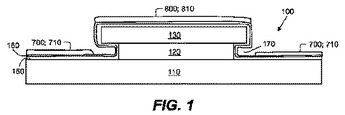

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

シリコンデバイス構造、及びその形成に用いるスパッタリングターゲット材

【課題】シリコンデバイスの飽和移動度特性を向上する。

【解決手段】シリコン半導体膜上に、Pドープn+型アモルファスシリコン膜と、該Pドープn+型アモルファスシリコン膜上に形成された配線とを有するシリコンデバイス構造において、前記配線が、前記Pドープn+型アモルファスシリコン膜の表面に形成されたシリコン酸化膜と、銅合金膜とからなり、前記銅合金膜は、1原子%以上5原子%以下のMn及び0.05原子%以上1.0原子%以下のPを含む銅合金をスパッタリングにより形成した膜である。

(もっと読む)

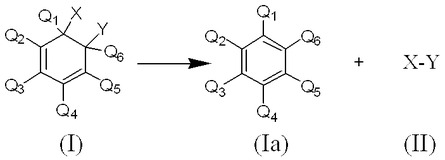

置換基脱離化合物とそれから得られる有機半導体材料、それを用いた有機電子デバイス、有機薄膜トランジスタおよびディスプレイ装置

【課題】高い有機溶媒溶解性を有し、低いエネルギー付与で有機半導体化合物に変換可能な置換基脱離化合物と、これを用いた有機電子デバイスを提供する。

【解決手段】一般式(I)で表され、エネルギー付与により一般式(Ia)で表される化合物と一般式(II)で表される化合物に変換可能なことを特徴とする置換基脱離化合物。

[式(I)、(Ia)、(II)中、XおよびYは水素原子もしくは脱離性置換基を表し、該XおよびYのうち一方は脱離性置換基であり、他方は水素原子である。Q1乃至Q6は水素原子、ハロゲン原子または、一価の有機基である。]

(もっと読む)

薄膜トランジスタおよび表示装置

【課題】層間絶縁膜に起因する不良を抑え、セルフアライン構造の薄膜トランジスタの信頼性を向上させることが可能な薄膜トランジスタおよびこれを備えた表示装置を提供する。

【解決手段】酸化物半導体膜20に接して、有機樹脂膜51を含む層間絶縁膜50を設ける。層間絶縁膜50の厚みを厚くして、ゲート絶縁膜30およびゲート電極40の段差を確実に被覆し、ソース電極60Sおよびドレイン電極60Dの断線あるいは短絡など、層間絶縁膜50に起因する不良を抑える。層間絶縁膜50は、有機樹脂膜51および第1無機絶縁膜52の積層構造を有していることが好ましい。酸素や水分などに対するバリア性の高い第1無機絶縁膜51により、酸化物半導体膜20への水分の混入や拡散を抑え、薄膜トランジスタ1の信頼性を向上させる。

(もっと読む)

電子回路付き基板及びその製造方法、並びに混合型電子回路形成キット

【課題】DNA又はDNA−脂質複合体を用いた簡易な方法により、基板上に導電性パターンを、画像流れを抑制しながら安定して形成できる電子回路付き基板の製造方法を提供する。

【解決手段】基板上に、DNA又はDNA−脂質複合体を含む溶液を描画することによって電子回路パターンを形成する工程と、前記電子回路パターンが形成された基板を多価金属イオン溶液に浸漬することによって、前記電子回路パターンにおいて、前記DNA又は前記DNA−脂質複合体と前記多価金属イオンとの錯体を形成する工程と、形成された錯体中の金属イオンを還元することによって、前記電子回路パターンを導電性パターンとする工程と、を有する電子回路付き基板の製造方法である。

(もっと読む)

薄膜トランジスタ、薄膜集積回路装置及びそれらの製造方法

【課題】低価格化の要請に応えることができ、半導体膜として用いた酸化物半導体膜にダメージを与えない手段を含む薄膜トランジスタ及びその製造方法、並びにその薄膜トランジスタを含む集積回路及びその製造方法を提供する。

【解決手段】基材1上に酸化物半導体膜3をパターン形成する工程と、活性化処理により酸化物半導体膜3にソース・ドレイン接続領域3s,3dを形成する工程と、ソース・ドレイン接続領域3s,3dが形成された酸化物半導体膜3を覆うように、塗布法、反応性スパッタリング法又はパルスプラズマCVD法でゲート絶縁膜4を形成する工程と、ゲート絶縁膜4にコンタクトホール5を開けてソース・ドレイン電極6を前記ソース・ドレイン接続領域3s,3dに接続するとともに酸化物半導体膜3上にゲート電極7を形成する工程と、を少なくとも有する製造方法により上記課題を解決する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いる薄膜トランジスタにおいて、安定した電気特性を有する信頼性のよい薄膜トランジスタを提供することを課題の一つとする。

【解決手段】酸化物半導体膜を用いる薄膜トランジスタのチャネル長が1.5μm以上100μm以下、好ましくは3μm以上10μm以下の範囲において、室温以上180℃以下の動作温度範囲、または、−25℃以上150℃以下の動作温度範囲で、しきい値電圧の変動幅を3V以下、好ましくは1.5V以下とすることで、安定した電気特性を有する半導体装置を作製することができる。特に半導体装置の一態様である表示装置において、しきい値の変動に起因する表示むらを低減することができる。

(もっと読む)

電子素子基板及びその製造方法

【課題】酸化物の一部領域又は全領域の比抵抗を低下させることにより、簡易な工程で多様な電子素子を作製できる電子素子基板の製造方法を提供する。

【解決手段】少なくとも最表層の一部が比抵抗1×109Ω・cm以下の酸化物からなる基板における前記酸化物の一部領域又は全領域に対し、前記基板の電位よりも高い電位を印加することにより、前記一部領域又は前記全領域の比抵抗を低下させる低抵抗化処理工程を有する電子素子基板の製造方法である。

(もっと読む)

電界効果トランジスタ

【課題】導体半導体接合を用いた電界効果トランジスタのオフ電流を低減せしめる構造を提供する。

【解決手段】半導体層1に、半導体層1の電子親和力と同程度かそれ以下の仕事関数の材料よりなる第1の導体電極3a、第2の導体電極3bを接して設け、さらに、半導体層1のゲートの形成された面と逆の面に接して、半導体層1の電子親和力より大きな仕事関数の材料で、半導体層を横切るようにして、第3の導体電極2を形成することにより、半導体層中にショットキーバリヤ型の接合を形成し、この部分のキャリア濃度が極めて低いことから、オフ電流を低減できる。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】Cu系合金配線膜を半導体層と直接接続しても接触抵抗率が低く、かつ密着性に優れた薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタの半導体層33と、Cu合金層28b、29bとを有する薄膜トランジスタ基板において、前記半導体層33と前記Cu合金層28b、29bとの間に、酸素含有層28a、29aを含んでおり、前記酸素含有層28a、29aを構成する酸素の一部若しくは全部は、前記薄膜トランジスタの前記半導体層33のSiと結合しており、前記Cu合金層28b、29bは、合金元素としてX(Xは、Mn、Ni、Zn、およびMgよりなる群から選ばれる少なくとも1種)を合計で2原子%以上20原子%以下含有し、前記Cu合金層28b、29bは、前記酸素含有層28a、29aを介して前記薄膜トランジスタの前記半導体層33と接続していることを特徴とする薄膜トランジスタ基板である。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接する半導体層と、半導体層の一部に接し、ソース領域及びドレイン領域を形成する不純物半導体層と、不純物半導体層に接する配線とを有し、半導体層において、ゲート絶縁層側に形成される凹凸状の微結晶半導体領域と、当該微結晶半導体領域に接する分離された非晶質半導体領域とを有し、微結晶半導体領域は、非晶質半導体領域に覆われていない第1の微結晶半導体領域と、分離された非晶質半導体領域と接する第2の微結晶半導体領域とで形成され、第1の微結晶半導体領域の厚さd1は第2の微結晶半導体領域の厚さd2より薄く、且つ第1の微結晶半導体領域の厚さd1が30nm以上である。

(もっと読む)

1 - 20 / 80

[ Back to top ]