Fターム[5F110HL04]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 金属 (8,797) | 高融点金属 (2,092)

Fターム[5F110HL04]に分類される特許

1 - 20 / 2,092

半導体装置およびその製造方法

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

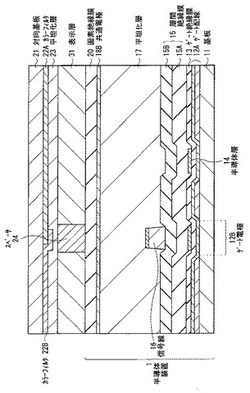

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明の液晶表示装置の製造方法によれば、高い表示品位を有する液晶表示装置を製造できる。

【解決手段】液晶表示装置の製造方法は、第2基板22の主面21a上に遮光膜BMを形成する工程と、遮光膜BMを覆うように第1絶縁膜226を形成する工程と、第1絶縁膜226上に透光性の導体層100を形成する工程と、導体層100上にレジストREを形成する工程と、第2基板22の反対主面22b側から、遮光膜BMと重ならない部分のレジストREを露光する工程と、レジストRE上にマスクPMを配置して、レジストREのうち遮光膜BMの形成領域上に位置するレジストREの一部をマスクPM側から露光する工程と、導体層100の一部を露出させる工程

と、導体層100の露出した一部をエッチングし、レジストを除去して、遮光膜BMの形成領

域上に信号電極228および共通電極227を形成する工程とを含むことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜上にチャネル保護膜として機能する絶縁層が設けられたボトムゲート構造のトランジスタを有する半導体装置において、酸化物半導体膜上に接して設けられる絶縁層、及び/または、ソース電極層及びドレイン電極層の形成後に不純物除去処理を行うことで、エッチングガスに含まれる元素が、酸化物半導体膜表面に不純物として残存することを防止する。酸化物半導体膜の表面における不純物濃度は、5×1018atoms/cm3以下、好ましくは1×1018atoms/cm3以下とする。

(もっと読む)

酸化物半導体膜の作製方法、半導体装置の作製方法及び半導体装置

【課題】絶縁表面に形成される酸化物半導体膜は、下地界面近傍に非晶質領域が残存してしまい、これがトランジスタなどの特性に影響を与える要因の一つと考えられている。

【解決手段】酸化物半導体膜に接する下地面又は酸化物半導体膜に接する膜を形成する材料の融点を、酸化物半導体を構成する材料の融点よりも高くする。これにより、酸化物半導体膜に接する下地面又は酸化物半導体膜に接する膜との界面近傍まで結晶領域が存在することを可能とする。当該材料として絶縁性の金属酸化物を用いる。金属酸化物として、酸化物半導体膜を構成する材料と同族の材料である酸化アルミニウム、酸化ガリウムなどを用いる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】Inと、M1と、M2と、Znと、を含む酸化物材料であり、M1=13族元素、代表的にはGaであり、M2の元素は、M1の元素よりも含有量が少ない材料を提供する。M2としてはTi、Zr、Hf、Ge、Snなどが挙げられる。M2を含ませることで、酸化物半導体材料における酸素欠損の発生を抑制することができる。酸素欠損がほとんど存在しないトランジスタを実現できれば、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程により、ソース電極層及びドレイン電極層を形成後、酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の不純物を除去する工程を行う。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供する。

【解決手段】ガラス基板上に設けられたボトムゲート構造のスタガ型トランジスタを有する半導体装置において、ゲート電極層上に組成を異なる第1のゲート絶縁膜及び第2のゲート絶縁膜が順に積層されたゲート絶縁膜を設ける。又は、ボトムゲート構造のスタガ型トランジスタにおいて、ガラス基板とゲート電極層との間に保護絶縁膜を設ける。第1のゲート絶縁膜と第2のゲート絶縁膜との界面、又はゲート電極層とゲート絶縁膜との界面における、ガラス基板中に含まれる金属元素の濃度を、5×1018atoms/cm3以下(好ましくは1×1018atoms/cm3以下)とする。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物を低減する。また、酸化物半導体膜の被形成面近傍の結晶性を向上させる。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】シリコンを含む下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも酸化物半導体膜と重畳する領域に設けられたゲート電極と、酸化物半導体膜に電気的に接続されたソース電極、及びドレイン電極と、を有し、酸化物半導体膜は、下地絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度で分布する領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置

【課題】有機半導体層の形成に際して、不所望の領域への有機半導体層の形成を抑制し、且つ、隣接する開口部間でのインクの混合を抑制することにより、高い品質を備える薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置を提供する。

【解決手段】隔壁1016には、3つの開口部1016a,1016b,1016cが開けられている。開口部1016b,1016cの各底部には、ソース電極1014a,1014b、ドレイン電極1014c,1014dが露出し、各々がチャネル部として機能する部分である。開口部1016bを臨む側面部のうち、側面部1016d,1016eは、側面部1016iに比べ、傾斜が相対的に急峻な斜面である。開口部1016cを臨む側面部のうち、側面部1016fは、側面部1016jに比べ、傾斜が相対的に急峻な斜面である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置

【課題】隣接する開口部の内部へ有機半導体インクを塗布した際に、互いのインクの混合を抑制し、高い品質を備える薄膜トランジスタ装置とその製造方法、有機EL表示素子、および有機EL表示装置を提供する。

【解決手段】隔壁1016における開口部1016bを臨む側面部のうち、隣接する開口部1016cの側の側面部1016eは、側面部1016dを含む他の側面部よりも傾斜が相対的に急峻な斜面となっている。隔壁1016における開口部1016cを臨む側面部のうち、隣接する開口部1016bの側の側面部1016fは、側面部1016gを含む他の側面部よりも傾斜が急峻な斜面となっている。開口部1016bと開口部1016cとの各内部に対して、有機半導体インクを塗布した場合、X軸方向に互いに離れる方向に偏った表面プロファイルを有することになる。

(もっと読む)

半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

(もっと読む)

1 - 20 / 2,092

[ Back to top ]