Fターム[5F110HM01]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461)

Fターム[5F110HM01]の下位に属するFターム

断面形状 (1,337)

平面形状 (975)

他の構成要素との相対的な大きさが規定 (146)

Fターム[5F110HM01]に分類される特許

1 - 3 / 3

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

線状素子

【課題】 柔軟性、可撓性があり任意の形状に集積回路を作成できるという特徴を持つ線状MISFETでは、ソース領域とドレイン領域を並列配置する構造が使用されていた。しかし、MISFETの電気特性を決めるチャネル長が円筒形のゲート絶縁領域に沿ったソース領域とドレイン領域の距離できまるため、チャネル長の微細化や再現性向上が困難だった。

【解決手段】 MISFETの構造を、ソース領域とドレイン領域でチャネル領域となる半導体領域を挟む構造とした。半導体領域にゲート絶縁領域を介して制御電圧を加え、ソース領域とドレイン領域間で流れる電流を制御する。チャネル長が、半導体領域の膜厚で決まるため、チャネル長の微細化や再現性向上が可能になった。

(もっと読む)

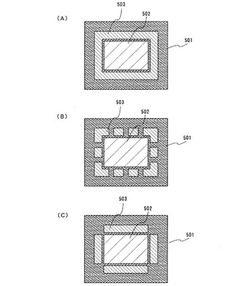

半導体装置

【課題】オン抵抗の低減や耐圧の向上が図れる半導体装置を提供する。

【解決手段】第1の絶縁層と、第1の絶縁層の上に設けられた半導体層と、半導体層に選択的に設けられた第1の半導体領域と、第1の半導体領域に対して離間して半導体層に選択的に設けられた第2の半導体領域と、第1の半導体領域に接して設けられた第1の主電極と、第2の半導体領域に接して設けられた第2の主電極と、半導体層の上に設けられた第2の絶縁層と、半導体層における第1の半導体領域と第2の半導体領域との間の部分の上方の第2の絶縁層中に設けられた第1の導電材と、第1の導電材に対向する部分の半導体層に設けられたトレンチ内に設けられ、第1の導電材に接し、かつ前記第1の絶縁層に達する第2の導電材とを備えている。

(もっと読む)

1 - 3 / 3

[ Back to top ]