Fターム[5F110HM19]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | ソース、ドレイン配線に工夫 (347)

Fターム[5F110HM19]に分類される特許

1 - 20 / 347

画像検出器

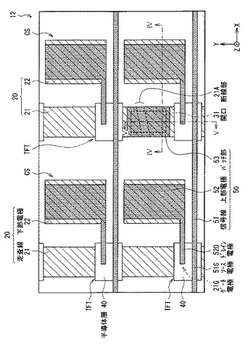

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

トランジスタ装置および電子デバイス

【課題】1本の棒状素子が破壊しても、他の棒状素子が正常に動作し、正常動作を続けるトランジスタ装置を提供する。

【解決手段】トランジスタ装置は、基板5と、この基板5上に配置された2本の棒状素子1とを有する。このため、一方の棒状素子1が破壊しても、他方の棒状素子1が正常に動作し、トランジスタ装置は、正常動作を続ける。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

トップゲート型アクティブマトリックス基板、およびその製造方法

【課題】データ配線が銀や銀合金により形成されており、またデータ配線に、ゲート絶縁層によって被覆されておらずむき出しとなっている部分があった場合でも、当該むき出しとなっている部分でマイグレーション現象が生じることがないトップゲート型アクティブマトリックスを提供する。

【解決手段】基材と、前記基材上に直接または間接的に形成された、ソース電極、ドレイン電極、半導体層、ゲート絶縁層、ゲート電極、層間絶縁層、画素電極、および前記ソース電極と接続したデータ配線と、を有するトップゲート型アクティブマトリックス基板において、前記ソース電極と前記データ配線をともに銀または銀合金で形成し、前記ゲート電極を銀または銀合金以外で形成し、前記データ配線においてむき出しとなっている部分をゲート電極と同じ材質からなる被覆層によって被覆する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

集積されたダイオードを有するSOI基板を備える複合半導体装置

【課題】高電圧が印加されても、故障しにくい複合半導体装置を提供する。

【解決手段】複合半導体装置200は、ダイオード210及び絶縁層204を含むSOI基板(semiconductor on insulator)を備える。複合半導体装置200は、ダイオード210の上に形成された遷移体220及び遷移体220の上に形成されたトランジスタ230も含む。ダイオード210は半導体貫通ビア、外部電気接続部又はその両方の組み合わせを用いてトランジスタ230の両端間に接続される。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

表示装置

【課題】動作速度を向上させる。

【解決手段】第1のソース及び第1のドレインの一方に画像信号線を介して画像信号が入力され、第1のゲートに第1の走査信号線を介して第1の走査信号が入力される第1のトランジスタ101と、2つの電極のうちの一方の電極が第1のトランジスタの第1のソース及び第1のドレインの他方に電気的に接続される容量素子102と、第2のソース及び第2のドレインの一方が第1のトランジスタ101の第1のソース及び第1のドレインの他方に電気的に接続され、第2のゲートに第2の走査信号線を介して第2の走査信号が入力される第2のトランジスタ103と、第1の電極が第2のトランジスタの第2のソース及び第2のドレインの他方に電気的に接続される液晶素子104と、を備え、画像信号線としての機能を有する導電層及び第2の走査信号が入力される走査信号線としての機能を有する導電層は、互いに離間し、且つ並置されている。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、酸化物半導体を用いた逆スタガ型薄膜トランジスタで構成する。

同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を増加させることなく電源供給配線の電気抵抗を下降させることが可能な、TFTを有する半導体装置を提供することである。

【解決手段】表面を有する絶縁膜II4と、絶縁膜II4の表面上に形成され、かつチャネル領域TP2と、チャネル領域TP2を挟む1対のソース/ドレイン領域TP1,TP4とを含む半導体層と、ソース領域TP1に電源を供給するための電源供給配線TP1とを備えている。上記絶縁膜II4の表面には凹部TRが形成されている。上記電源供給配線TP1は、半導体層と同一の層から形成された層を含み、かつ絶縁膜II4の表面上に形成された第1の部分TP1Aと、凹部内に形成された第2の部分TP1Bとを有している。上記第2の部分TP1Bの底面全体が絶縁体II4で覆われている。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

シリコン・オン・インシュレータ内に形成された金属酸化膜半導体デバイス

【課題】デバイスの破壊電圧を大きく低下させずにLDMOSデバイスのオン抵抗を減少可能にすること。

【解決手段】半導体デバイスが、第1導電型の基板、基板の少なくとも一部分上に形成された絶縁層、および絶縁層の少なくとも一部分上に形成された第2導電型のエピタキシャル層を備える。第1、第2導電型のソース/ドレイン領域が、エピタキシャル層内でその上面に近接して形成され、第1、第2ソース/ドレイン領域は互いに横に間隔を置いて設置される。ゲートは、エピタキシャル層の上でその上面に近接して、少なくとも部分的に第1および第2ソース/ドレイン領域の間に形成される。このデバイスはさらに、エピタキシャル層と、絶縁層を貫通して形成され、基板、第1ソース/ドレイン領域、およびエピタキシャル層と直接に電気的に接続するように構成された第1のソース/ドレイン接点と、エピタキシャル層を貫通して形成され、第2ソース/ドレイン領域に直接に電気的に接続できるように構成された第2ソース/ドレイン接点とを備える。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

液晶表示装置、電子機器

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、少ない工程で多層配線化を実現し、小面積で高機能な機能回路を有する配線基板及び半導体装置を提供する。またこのような高機能な機能回路を表示装置と同一基板上に一体形成した半導体装置を提供することを課題とする。

【解決手段】本発明は、絶縁表面を有する基板上に、第1の配線と、第2の配線と、第3の配線と、第1の層間絶縁膜と第2の層間絶縁膜と、第1のコンタクトホールと第2のコンタクトホールを有し、前記第2の配線の幅を前記第1の配線の幅より広いか、あるいは前記第3の配線の幅を前記第1の配線の幅もしくは前記第2の配線の幅より広く、且つ前記第2のコンタクトホールの直径を前記第1のコンタクトホールの直径より大きく形成することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

薄膜トランジスタ液晶ディスプレイのアレイ基板及びその製造方法

【課題】本発明はTFT−LCDアレイ基板及びその製造方法に関する。

【解決手段】本発明はTFT−LCDアレイ基板及びその製造方法に関し、アレイ基板はベース基板と、ベース基板上に形成され画素領域を限定するゲートライン及びデータラインを含み、前記画素領域内には画素電極、薄膜トランジスタと共通電極が形成される。また、導電性薄膜材料により製造されるブラックマトリクスを含み、前記ブラックマトリクスは前記共通電極と接続される。

(もっと読む)

1 - 20 / 347

[ Back to top ]