Fターム[5F110NN15]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 島状のチャネル保護膜 (1,301) | 保護以外の機能 (338)

Fターム[5F110NN15]の下位に属するFターム

エッチングストッパ (258)

Fターム[5F110NN15]に分類される特許

1 - 20 / 80

半導体装置

【課題】酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供する。

【解決手段】ガラス基板上に設けられたボトムゲート構造のスタガ型トランジスタを有する半導体装置において、ゲート電極層上に組成を異なる第1のゲート絶縁膜及び第2のゲート絶縁膜が順に積層されたゲート絶縁膜を設ける。又は、ボトムゲート構造のスタガ型トランジスタにおいて、ガラス基板とゲート電極層との間に保護絶縁膜を設ける。第1のゲート絶縁膜と第2のゲート絶縁膜との界面、又はゲート電極層とゲート絶縁膜との界面における、ガラス基板中に含まれる金属元素の濃度を、5×1018atoms/cm3以下(好ましくは1×1018atoms/cm3以下)とする。

(もっと読む)

薄膜半導体装置及びその製造方法

【課題】チャネル保護型の薄膜トランジスタにおいて、オフ特性及び信頼性に優れた薄膜半導体装置の製造方法を提供する。

【解決手段】基板1を準備する第1工程と、基板1上にゲート電極2を形成する第2工程と、ゲート電極2上に第1絶縁膜としてゲート絶縁膜3を形成する第3工程と、ゲート絶縁膜3上に非結晶質の半導体薄膜4aを形成する第4工程と、非結晶質の半導体薄膜4a上に第2絶縁膜としてチャネル保護膜5を形成する第5工程と、チャネル保護膜5の上方からレーザー光を照射することにより、非結晶質の半導体薄膜4aを結晶化させて結晶化領域を形成する第6工程と、結晶化領域の上方にソース電極7S及びドレイン電極7Dを形成する第7工程と、を含み、第5工程において、チャネル保護膜5は、前記レーザー光に対して透明となるように形成される。

(もっと読む)

エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法

【課題】エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法を提供する。

【解決手段】基板上のゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上のグラフェンチャネルと、グラフェンチャネル上で互いに離隔しているソース電極及びドレイン電極と、ソース電極及びドレイン電極の上面を覆い、グラフェンチャネル上でソース電極とドレイン電極との間にエアギャップを形成するカバーと、を備えるグラフェントランジスタ。前記ソース電極と前記ドレイン電極との間の前記グラフェンチャネルの長さが、10nm〜100nmである。

(もっと読む)

積層構造、有機半導体素子、配線および表示装置、並びに有機半導体素子の製造方法

【課題】バリア性の高い保護層を有する積層構造、有機半導体素子、配線および表示装置、並びに有機半導体素子の製造方法を提供する。

【解決手段】導体または半導体を含む有機層と、絶縁材料により構成され、前記有機層を覆う保護層と、外周が前記絶縁材料と親和性を有する親和層に覆われ、前記保護層に分散された複数の粒体とを備えた積層構造。

(もっと読む)

酸化物半導体電界効果型トランジスタ及びその製造方法

【課題】移動度が高く、S値の低い電界効果型トランジスタの提供を目的とする。また、低温又は短時間の熱履歴でも高い特性の得られる電界効果型トランジスタの製造方法の提供を目的とする。

【解決手段】In元素及びZn元素と、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr、Nb、Al、B、Sc、Y及びランタノイド類からなる群より選択される1以上の元素Xを、下記(1)〜(3)の原子比で含む複合酸化物からなる半導体層を有する電界効果型トランジスタ。

In/(In+Zn)=0.2〜0.8 (1)

In/(In+X)=0.29〜0.99 (2)

Zn/(X+Zn)=0.29〜0.99 (3)

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置、薄膜トランジスタ基板および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置を提供する。

【解決手段】基板上に、金属酸化物を用いた絶縁膜と半導体薄膜とが積層形成された半導体装置であって、絶縁膜はゲート絶縁膜として用いられ、ゲート絶縁膜に接する側にゲート電極が積層形成され、絶縁膜および半導体薄膜は結晶化され、かつ、ゲート電極と重なる部分の結晶性が他の部分の結晶性よりも高いものである。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、第3族元素、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体層を用いる。第3族元素は安定剤として機能する。

(もっと読む)

薄膜デバイス及びその製造方法

【課題】酸化物半導体膜を用いたTFTでは、ソース・ドレイン電極のプラズマエッチング後に酸化物半導体膜の表面領域に酸素欠損が生成されオフ電流が高くなってしまうという課題があった。

【解決手段】TFT101は、絶縁性基板10上のゲート電極11、ゲート電極11上のゲート絶縁膜12、ゲート絶縁膜12上のインジウムを含む酸化物半導体膜13、及び、酸化物半導体膜13上のソース・ドレイン電極14を有する。そして、酸化物半導体膜13のソース・ドレイン電極14が重ならない部分の表面層15におけるXPSスペクトルのインジウム3d軌道起因のピーク位置が、表面層15の下部に存在する酸化物半導体領域におけるXPSスペクトルのインジウム3d軌道起因のピーク位置よりも、高エネルギ側にシフトしている。

(もっと読む)

薄膜デバイス

【課題】 酸化物半導体膜を用いたTFTでは、ソース・ドレイン電極のプラズマエッチング後に酸化物半導体膜の表面領域に酸素欠損が生成されオフ電流が高くなってしまうという課題があった。

【解決手段】TFT101は、基板としての絶縁性基板10上のゲート電極11、ゲート電極11上のゲート絶縁膜12、ゲート絶縁膜12上の酸化物半導体膜13、及び、酸化物半導体膜13上のソース・ドレイン電極14を有する。そして、TFT101の特徴は、酸化物半導体膜13のソース・ドレイン電極14が重ならない部分に、フッ素及び塩素の少なくとも一方を含む表面層15が存在することである。

(もっと読む)

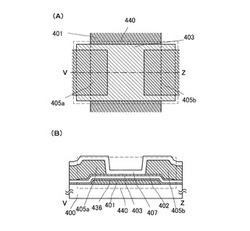

半導体装置の作製方法

【課題】薄膜トランジスタのしきい値電圧を制御するため、薄膜トランジスタのチャネル形成領域の上下にゲート絶縁膜を介してゲート電極を設けた際に、プロセス数の増加を招くことなく、電気特性の優れた薄膜トランジスタを備えた半導体装置を得る。

【解決手段】酸化物半導体層131の上方に設ける第2のゲート電極133を形成するとき、酸化物半導体層131のパターニングと同時に形成することで、第2のゲート電極133の作製に要するプロセス数の増加を削減する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを

目的の一つとする。

【解決手段】酸化物半導体層に対して、窒素、または希ガス(アルゴン、ヘリウムなど)

の不活性気体雰囲気下、或いは減圧下で脱水化、又は脱水素化処理のための加熱処理を行

い、酸素、酸素及び窒素、又は大気(好ましくは露点−40℃以下、より好ましくは−5

0℃以下)雰囲気下で加酸化処理のための冷却工程を行うことで高純度化及びI型化した

酸化物半導体層を形成する。該酸化物半導体層を含む薄膜トランジスタを有する半導体装

置を作製する。

(もっと読む)

半導体素子およびその製造方法、表示装置ならびに電子機器

【課題】信頼性を向上させることが可能な半導体素子およびその製造方法等を提供する。

【解決手段】半導体素子は、有機半導体層と、この有機半導体層と接するように配設された電極と、この電極とは別体として形成され、かつ電極と電気的に接続された配線層とを備えている。半導体素子の製造方法は、基板上に、有機半導体層およびこの有機半導体層と接する電極を形成する工程と、この電極と電気的に接続された配線層を形成する工程とを含んでいる。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】新規な非シリコン系半導体薄膜を用いた薄膜トランジスタを提供する。

【解決手段】ガリウムが酸化インジウムに固溶していて、原子比Ga/(Ga+In)が0.001〜0.12であり、全金属原子に対するインジウムとガリウムの含有率が80原子%以上であり、In2O3のビックスバイト構造を有する酸化物薄膜を用いることを特徴とする薄膜トランジスタ。

(もっと読む)

有機半導体素子およびその製造方法

【課題】本発明は、製造時におけるソース電極およびドレイン電極の劣化を好適に防止することができ、優れたスイッチング機能を有する有機半導体素子およびその製造方法を提供することを主目的とする。

【解決手段】基材と、上記基材上に形成されたゲート電極と、上記ゲート電極を覆うように形成されたゲート絶縁層と、上記ゲート絶縁層上に形成され、銀を主成分とする金属材料を含むソース電極およびドレイン電極と、上記ソース電極および上記ドレイン電極上に形成され、酸素に対する遮蔽性を有する電極保護層と、少なくとも上記ソース電極および上記ドレイン電極の間のチャネル領域に形成可能なパターン形状を有し、有機半導体材料を含む有機半導体層と、上記有機半導体層上のみに形成され、真空紫外光に対する遮光性を有する遮光材料を含むVUV遮蔽層とを有することを特徴とする有機半導体素子を提供することにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】支持基板上に絶縁層を形成し、当該絶縁層上に高純度化された酸化物半導体と、SOI(Silicon On Insulator)基板である単結晶シリコンを用いて半導体装置を構成する。高純度化された酸化物半導体を用いて構成したトランジスタは、リーク電流が極めて小さいため、長期間にわたって情報を保持することが可能である。また、SOI基板を用いることにより、絶縁層上に形成された薄い単結晶シリコンの特長を生かすことで、トランジスタを完全空乏型とすることができるため、高集積、高速駆動、低消費電力など付加価値の高い半導体集積回路が実現できる。

(もっと読む)

1 - 20 / 80

[ Back to top ]