Fターム[5F110NN26]の内容

薄膜トランジスタ (412,022) | その他の構成要素 (47,691) | 保護膜(パッシベーション膜) (34,477) | 材料 (15,721) | BSG (113)

Fターム[5F110NN26]に分類される特許

1 - 20 / 113

半導体装置及びその作製方法

半導体装置の作製方法

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

コンタクトホールの形成方法および電気光学装置の製造方法

【課題】シュリンク技術を利用して、コンタクトホールとして利用できる複数の凹部を1回のレジストマスク工程で異なる深さ寸法に形成することのできるコンタクトホールの形成方法、および電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置の素子基板10上にコンタクトホールを形成するにあたって、まず、第1開口部17aおよび第2開口部17bを備えたレジストマスク17を層間絶縁膜42の表面に形成した後、第1開口部17aおよび第2開口部17bから層間絶縁膜42および絶縁膜49をエッチングする。その後、シュリンク工程において、レジストマスク17を変形させて第2開口部17bを塞ぐ一方、第1開口部17aの開口面積を狭める。次に、第1開口部17aから層間絶縁膜41およびゲート絶縁層2をエッチングする。

(もっと読む)

半導体素子の作製方法

【課題】閾値電圧が制御され、動作速度が速く、製造工程が比較的簡単であり、十分な信頼性を有する、酸化物半導体を用いた薄膜トランジスタ、及び薄膜トランジスタの作製方法を提供することを課題の一つとする。

【解決手段】酸化物半導体層に含まれるキャリア濃度に影響する不純物、例えば、水素原子や、H2Oなど水素原子を含む化合物を排除すればよい。酸化物半導体層に接して未結合手に代表される欠陥を多く含む酸化物絶縁層を形成し、当該酸化物絶縁層に不純物を拡散させ、上記酸化物半導体層中の不純物濃度を低減すればよい。また、酸化物半導体層、又は酸化物半導体層に接する酸化物絶縁層を、クライオポンプを用いて排気して不純物濃度が低減された成膜室内で成膜すればよい。

(もっと読む)

半導体装置

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の

影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置

を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電

極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トラン

ジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を

用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

部材の作製方法

【課題】トランジスタなどの半導体素子を有する半導体装置を安価に得ることのできる生

産性の高い作製工程を提供することを課題の一とする。

【解決手段】下地部材上に、酸化物部材を形成し、加熱処理を行って表面から内部に向か

って結晶成長する第1の酸化物結晶部材を形成し、第1の酸化物結晶部材上に第2の酸化

物結晶部材を積層して設ける積層酸化物材料の作製方法である。特に第1の酸化物結晶部

材と第2の酸化物結晶部材がc軸を共通している。ホモ結晶成長またはヘテロ結晶成長の

同軸(アキシャル)成長をさせていることである。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

半導体装置

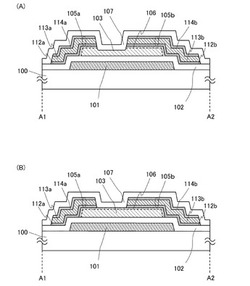

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層113と、平坦化層113の上面もしくは下面に設けられると共に平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層112を備えた半導体装置であって、これら平坦化層113及びバリア層112の位置関係を工夫することにより平坦化層113に及ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極158の構造として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

電気光学装置の製造方法

【課題】素子基板に絶縁膜を成膜した際にフッ素が混入しても、電界効果型トランジスターに特性異常が発生することを防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】素子基板10にシリコン酸化膜からなる絶縁膜12を成膜する第1絶縁膜成膜工程の後、画素トランジスター30(電界効果型トランジスター)の半導体層1aを形成する半導体層形成工程を行う前に、絶縁膜12に水素を導入する第1絶縁膜水素導入工程を行う。また、シリコン酸化膜からなる層間絶縁膜41を形成する第2絶縁膜成膜工程の後、層間絶縁膜41に対して水素の導入を行う第2絶縁膜水素導入工程を行う。このため、絶縁膜12や層間絶縁膜41にフッ素が混入していた場合でも、かかるフッ素は、水素と結合してフッ化水素として放出される。

(もっと読む)

電気光学装置の製造方法

【課題】テトラエトキシシラン等のシラン系有機材料を用いたプラズマCVD法によりシリケートガラスを形成した場合でも、シリケートガラスから半導体層へのフッ素の侵入を防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造方法において、ゲート電極3cの形成工程、低濃度不純物導入工程、および高濃度不純物導入工程を行った後、シランガス等のシラン系無機原料を用いたCVD法により第1絶縁膜411を形成する。次に、第1アニール工程において第1絶縁膜411をアニールした後、テトラエトキシシラン等のシラン系有機原料を用いたプラズマCVD法によりシリケートガラスからなる第2絶縁膜412を形成する。

(もっと読む)

シリコン酸化膜の形成方法、半導体装置及びその製造方法

【課題】基板表面に、均一な高品質シリコン酸化膜を、基板温度200−500度の低温で形成すること、および、シリコン酸化膜を用いた半導体装置を提供し、素子分離領域凹部分の側壁部のシリコン表面においてシリコン酸化膜の厚さ30%以内に抑え、デバイスの信頼性を向上する。

【解決手段】シリコン酸化膜中にKrを含有することを特徴とする。シリコン酸化膜中にKrを含有させることにより、シリコン酸化膜中および、シリコン/シリコン酸化膜界面でのストレスを緩和することにより、低温で形成したにも係わらず高品質なシリコン酸化膜を形成し、素子分離領域凹部分の側壁部のシリコン表面においてシリコン酸化膜の厚さの均一性を30%以内にする。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、積層構造の単純化を図り、しかも高品質な表示を可能とする。

【解決手段】電気光学装置は、基板(10)上に、互いに交差するデータ線(6)及び複数の走査線(11)と、データ線に電気的に接続された第1ソースドレイン領域、及び第2ソースドレイン領域を含んでなる半導体層(30a)と、複数の走査線のうち一の走査線に電気的に接続されたゲート電極とを有するトランジスター(30a)と、半導体層と基板との間に配置され、第2ソースドレイン領域に電気的に接続された第1容量電極(71)と、第1容量電極に対向するように設けられるとともに一の走査線に隣り合う走査線に電気的に接続された第2容量電極(73)とを有する蓄積容量(70)と、を備え、蓄積容量は、基板上に設けられた溝の内部の少なくとも一部に設けられている。

(もっと読む)

半導体装置

【課題】光感度を向上させた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、柔軟性を有し、可視光に対して透明な透明基板12と、透明基板上に設けられる透明電極14と、透明電極の透明基板と接している面の反対側の一部に設けられる有機半導体層16と、有機半導体層の透明電極と接している面の反対側の表面の上方に設けられる反射層71とを備える。

(もっと読む)

埋め込みゲートを有する半導体装置及びその製造方法

【課題】埋め込みゲートトランジスタのSCEに対する免疫性を向上させると同時に、分岐点での重なりを増加させる方法及び構造の提供。

【解決手段】基板102は第1活性領域104と第2活性領域106とを有し、浅溝分離(STI)領域108によって分離される。バッファ層112は応力緩和層として機能しハードマスク層114が形成される。基板102の表面に分離領域108を部分的に網羅するように凹部118を設ける。ゲート誘電体120が凹部118に形成された後第一ドーパントインプラント122により、ドープ済みチャンネル領域124が形成される。インプラントはハードマスク114を貫通しないので、凹部118の下に形成されたドープ済みチャンネル領域124中のドーパント濃度は最も高くなる。ドープ済みチャンネル領域124はトランジスタのオン・オフを切り替える閾値電圧を変調する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

光電変換装置

【課題】電圧降下が小さい整流素子を得ること、及び、コンバータ回路の作製コストを抑制することを課題とする。

【解決手段】光電変換素子と、当該光電変換素子の出力を昇圧又は降圧し、スイッチング素子及び整流素子を有するコンバータ回路と、を有する光電変換装置において、当該スイッチング素子として、ノーマリオフの第1の酸化物半導体トランジスタと、当該整流素子として、ダイオード接続されたノーマリオンの第2の酸化物半導体トランジスタとを有する光電変換装置に関する。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

1 - 20 / 113

[ Back to top ]