Fターム[5F110NN61]の内容

Fターム[5F110NN61]の下位に属するFターム

Fターム[5F110NN61]に分類される特許

1 - 17 / 17

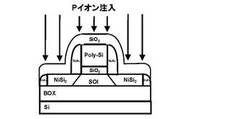

MOSトランジスタの製造方法

【課題】メタルソース/ドレインを有する極薄SOIMOSトランジスタにおいて、ゲート電極/ゲート絶縁膜の側壁につけた保護膜エッジからゲートエッジまでソース/ドレインの位置の制御とショットキーバリアハイトの制御の両者が実現できるMOSトランジスタの製造方法を提供する。

【解決手段】SOI層上にゲート電極を形成する工程と、該ゲート電極の側面にスペーサーを形成する工程と、該ゲート電極及び該保護膜をマスクにSOI層上に窒素添加Ni膜を成膜する工程と該Ni膜上にTiN膜を形成する工程と、窒素中でアニールしSOI層中にソース及びドレインとなるエピタキシャルNiSi2層を形成する工程と、TiNと残ったNi膜を除去する工程と、該ゲート電極及び該保護膜をマスクに該エピタキシャルNiSi2層中にPイオンを注入する工程と、該Pイオンを活性化する工程とを含むMOSトランジスタの製造方法。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】IGBTのESD耐性を高くしつつ、IGBTのバイポーラトランジスタを確実に動作させる。

【解決手段】シンカー層115は第1導電型ウェル102に接しており、かつ第1導電型コレクタ層108及び第2導電型ドリフト層104から離れている。シンカー層115の表層には、第2導電型拡散層(第2の第2導電型高濃度拡散層)116が形成されている。第2導電型拡散層116はシンカー層115より不純物濃度が高い。第2導電型拡散層116と第1導電型コレクタ層108は、素子分離絶縁膜16を介して互いに分離している。

(もっと読む)

半導体装置

【目的】高耐圧NMOSFETなどのレベルシフト素子から素子分離溝越しに隣接した高電位浮遊領域への高電位配線を、高耐圧NMOSFETの耐圧低下や層間絶縁膜の破壊および素子分離溝の分離耐圧劣化を招くことなく、形成できる半導体装置を提供する。

【解決手段】高電位配線9の直下にnドレインバッファ層10と接してp-拡散層11とこれに接するp+拡散層12を形成することで、高電位配線9が横切る絶縁膜44aの電界強度を低下できる。絶縁膜44aの電界強度を低下させることで、高耐圧NMOSFET20の耐圧低下や層間絶縁膜5の破壊および素子分離溝(トレンチ4a)の分離耐圧劣化を防止できる。

(もっと読む)

半導体装置の製造方法

【課題】表面状態および膜質の均一性を保って有機半導体層をパターニングすることが可能な半導体装置の製造方法を提供する。

【解決手段】先ず第1の工程では、基板1上に有機半導体膜9を成膜する。次の第2工程では、有機半導体膜9上に保護パターン11を形成する。その後第3工程では、保護パターン11をマスクにして、有機半導体層9を有機溶媒に溶解させるかまたは昇華させることにより、パターニング表面を変質させることなく有機半導体層9をパターニングする。

(もっと読む)

半導体装置

【課題】ゲート・オール・アラウンドトランジスタの複数のチャネルそれぞれに流れる電流を均一にし、ゲート・オール・アラウンドトランジスタの信頼性を向上させる。

【解決手段】半導体基板と、半導体基板上に一定の間隔をおいて形成された第1の半導体層上に第2の半導体層を形成した積層構造が複数積み重なったソース・ドレイン領域と、第2の半導体層の同一レイヤ間をそれぞれ接続するようにワイア状に形成された複数のチャネル領域と、前記複数のチャネル領域をそれぞれ包み込むようにゲート絶縁膜を介して形成されたゲート電極とを具備し、チャネル領域のチャネル幅は、半導体基板から離れるほど狭く形成され、第2の半導体層及びチャネル領域の膜厚は、半導体基板から離れるほど広く形成される。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いたノーマリオフ型のトランジスタを備えた半導体装置において、駆動時のゲート電流を低減しつつ、トランジスタの過渡応答特性を安定させる。

【解決手段】半導体装置は、基板101と、基板101の上に積層された複数の窒化物半導体層からなり、且つチャネル領域を含む第1の窒化物半導体層104Sと、第1の窒化物半導体層104Sの上に形成され、且つチャネル領域と逆導電型の第2の半導体層105と、第2の半導体層105に接するように形成され、金属層107からなる導電層と、導電層の上に形成された絶縁体層110と、絶縁体層110の上に形成されたゲート電極111と、第2の半導体層105の両側方に形成されたソース電極108及びドレイン電極109とを備えている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】膜の剥がれの度合いを低減することで、半導体装置の防水性を向上させ且つ信頼性を高めることを課題とする。

【解決手段】基板上に、第1の無機絶縁層、半導体素子層、第2の無機絶縁層、有機絶縁層、及び第3の無機絶縁層が順次積層して設け、第2の無機絶縁層は、半導体素子層に設けられた開口部で第1の無機絶縁層と接して設け、第3の無機絶縁層は、有機絶縁層に設けられた開口部で第2の無機絶縁層と接して設け、第2の無機絶縁層及び第3の無機絶縁層が接する面において、第2の無機絶縁層に、複数の凹凸または開口部を設ける。また、第2の無機絶縁層に設けられた複数の凹凸または開口部と重畳する領域の第3の無機絶縁層の表面に複数の凹凸を設ける。

(もっと読む)

半導体装置の作製方法

【課題】フォトリソグラフィ工程の回数を削減し、製造工程を簡略化し、低いコストで歩留まり良く製造すること可能となる半導体装置の作製方法を提供する。

【解決手段】半導体膜を成膜し、レーザビームを遮蔽する遮蔽物を有するフォトマスクを通してレーザビームを照射し、半導体膜中の、フォトマスク中の遮蔽物が形成されない領域を介してレーザビームが照射された領域は昇華し、フォトマスク中の遮蔽物が形成された領域によりレーザビームが照射されなかった領域は昇華せずに島状半導体膜が形成され、ソース電極またはドレイン電極の一方である第1の電極と、ソース電極またはドレイン電極の他方である第2の電極が形成され、ゲート絶縁膜が形成され、ゲート絶縁膜上にゲート電極が形成される半導体装置の作製方法に関する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】絶縁層の被覆不良によるゲート電極層と半導体層とのショート及びリーク電流などの不良が防止された信頼性の高い半導体装置、及びそのような半導体装置の作製方法を提供することを目的とする。

【解決手段】絶縁表面上に複数の半導体素子を形成するために、連続した一つの半導体層中に半導体素子として機能する素子領域と、PN接合の繰り返しにより素子領域間を電気的に分離する機能を有する素子分離領域を形成する。素子分離領域は、連続した一つの半導体層において、素子間を電気的に分離するために、選択的に酸素、窒素、及び炭素のうち少なくとも一種以上の不純物元素及び接する素子領域と逆導電型を付与する不純物元素を添加して形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】素子を過大電圧から保護するツェナーダイオードによって、余分な面積を必要としない半導体装置を実現する。

【解決手段】p型基層102と埋め込み絶縁層104と活性層106が積層されているSOI基板100の活性層106の一部に素子領域122が形成されており、素子領域を一巡する素子領域分離用絶縁壁124が形成されている。素子領域分離用絶縁壁124は、活性層106の表面から埋め込み絶縁層104を貫通してp型基層102に至っている。素子領域分離用絶縁壁124の壁厚の内側に導体132が形成されており、導体132はn型領域130とp型基層102で形成されるツェナーダイオード131を介して接地される。

(もっと読む)

SOI構造を有する半導体装置

【課題】ソース/ドレイン領域からの不純物の拡散を抑制することができるSOI構造を有する半導体装置を提供する。

【解決手段】主表面を有する単結晶シリコン層は、埋込酸化膜2上に形成されている。第1導電型の1対のソース/ドレイン領域14は、単結晶シリコン層の主表面にチャネル領域を規定するように形成されている。ゲート電極12は単結晶シリコン層の主表面上にゲート絶縁膜11を介して形成されている。フィールド酸化膜13は単結晶シリコン層の主表面に形成され、単結晶シリコン層を複数の単結晶シリコン層3に分離している。単結晶シリコン層3とフィールド酸化膜13との境界近傍の単結晶シリコン層3に窒素が導入されている。窒素の濃度プロファイルは、フィールド酸化膜13に接する単結晶シリコン層3表面に窒素パイル・アップ領域8を有している。

(もっと読む)

半導体装置の形成方法

【目的】SOS基板上への集積回路の製造プロセスにおいて、基板加熱中に発生する基板の反りを抑制する、あるいは反ってしまった基板をいち早く修復する。

【解決手段】SOS基板14、ポリシリコン膜15及びシリコン窒化膜17からなる構造体18の、上側表面の外周から、直径方向に距離を空けた位置に最外側の素子分離領域19aを形成することで、放熱領域21と素子領域23とを区画する。更に、放熱領域上に良熱伝導性を有するゲートポリシリコン膜25及び、タングステンシリサイド膜27を順次形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体膜のチャネル領域の端部におけるゲート絶縁膜の段切れや薄膜化により生じる半導体膜とゲート電極とのショートやリーク電流を抑制する半導体装置および当該半導体装置の作製方法の提供を課題とする。

【解決手段】基板上に連続して設けられた半導体膜と、半導体膜の上方にゲート絶縁膜を介して設けられた導電膜と、導電膜と重ならない半導体膜に形成されたソース領域及びドレイン領域と、導電膜の下方に位置する半導体膜であってソース領域とドレイン領域の間に形成されたチャネル領域とを有する複数の薄膜トランジスタと、導電膜と重ならない半導体膜であってソース領域及びドレイン領域と隣接して設けられた不純物領域とを有し、導電膜をチャネル領域及びチャネル領域に隣接する半導体膜上に設ける構成とする。

(もっと読む)

有機薄膜トランジスタ及びその製造方法、並びにこの有機薄膜トランジスタを備える平板表示装置

【課題】有機半導体層の表面損傷を防止し、オフ電流を減少させうる有機薄膜トランジスタを提供する。

【解決手段】基板110と、基板110上に形成されたソース/ドレイン電極12/125と、基板110上に形成され、ソース/ドレイン電極12/125及びそれらの間にかけて形成されるチャンネル層135を含む半導体層130と、半導体層130上に形成されるゲート絶縁膜140と、半導体層130とゲート絶縁膜140とにかけて形成されて、チャンネル層135を分離させるための分離パターン145と、チャンネル層135の上部のゲート絶縁膜140上に形成されるゲート電極155とを含むOTFT。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 絶縁体上に形成される半導体層の配置位置に制約を伴うことなく、信頼性の高い半導体層を絶縁体上に安価に形成する。

【解決手段】 第1半導体層2上に第2半導体層3を形成し、開口部8を介してエッチングガスまたはエッチング液を第1半導体層2に接触させることにより、第1半導体層2の一部をエッチング除去し、半導体基板1と第2半導体層3との間に空洞部9を形成した後、空洞部9内の半導体基板1および第2半導体層3の表層に熱酸化膜10を形成し、CVD法により開口部8を介して空洞部9内に埋め込み絶縁膜11を埋め込む。

(もっと読む)

1 - 17 / 17

[ Back to top ]