Fターム[5F110NN71]の内容

Fターム[5F110NN71]の下位に属するFターム

Fターム[5F110NN71]に分類される特許

81 - 100 / 2,024

薄膜トランジスタ及びそれを用いた電子デバイス

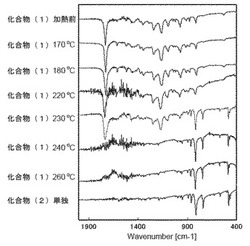

【課題】特定構造のπ電子共役化合物前駆体を含む薄膜中の該前駆体のπ電子共役化合物への変換が、基板の耐熱温度に制限されることなく、且つ大気下で進行する、有機膜の製造方法。

【解決手段】π電子共役化合物前駆体A−(B)mを含む薄膜中の該前駆体A−(B)mが、活性エネルギー線の照射により、π電子共役系化合物A−(C)mと脱離性化合物X−Yに変換される。A−(B)m→A−(C)m+X−Y

(Aはπ電子共役系置換基、Bは溶媒可溶性置換基、mは自然数である。)

(もっと読む)

表示装置

【課題】ゲート絶縁層として要求される耐圧や容量を確保しつつ、外光反射率によるコントラストの劣化を抑えやすくした表示装置を提供する。

【解決手段】透明基板GAと、透明基板GAの上側に形成されるゲート電極GTと、ゲート電極GTの上側に形成される微結晶半導体層MSと、ゲート電極GTと微結晶半導体層MSの間に形成されて、微結晶半導体層MSの外方に延在するゲート絶縁層GIと、ゲート絶縁層GIの微結晶半導体層MSの外方に延在する部分の上面に接して、窒化ケイ素で形成される第2の窒化ケイ素層NI2と、を有し、ゲート絶縁層GIは、第1の窒化ケイ素層NI1と、第1の窒化ケイ素層NI1の上側に形成されて微結晶半導体層MSに接する酸化ケイ素層OIと、を含み、ゲート絶縁層GIは、微結晶半導体層MSの下側の部分よりも第2の窒化ケイ素層NI2の下面に接する部分で薄く形成される、ことを特徴とする表示装置。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、酸化物半導体を用いたデバイスにおいて高い移動度を達成し

、信頼性の高い表示装置を提供する。

【解決手段】表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層を形

成し、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加熱処理を行うことによ

り、酸化物半導体層に酸素を供給し、酸化物絶縁層上に、水素を含む窒化物絶縁層を形成

し、第4の加熱処理を行うことにより、少なくとも酸化物半導体層と酸化物絶縁層の界面

に水素を供給する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と該酸化物半導体膜と接する下地となる膜との界面の電子状態が良好なトランジスタ。

【解決手段】下地となる膜は酸化物半導体膜と同様の原子配列を有し、下地となる膜と酸化物半導体膜とが接している面において、面内の下地膜の最隣接原子間距離と酸化物半導体の格子定数の差を、下地となる膜の同面内における最隣接原子間距離で除した値は0.15以下、好ましくは0.12以下、さらに好ましくは0.10以下、さらに好ましくは0.08以下とする。例えば、立方晶系の結晶構造を有し(111)面に配向する安定化ジルコニアを含む下地となる膜上に酸化物半導体膜を成膜することで、下地となる膜の直上においても結晶化度の高い結晶領域を有する酸化物半導体膜が得られる。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】酸化物半導体をチャネル形成領域に用いたトランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現するトランジスタ構造を提供する。

【解決手段】異なるエネルギーギャップを有する、少なくとも第1の酸化物半導体層及び第2の酸化物半導体層を積層させた酸化物半導体積層であって、化学量論的組成比よりも過剰に酸素を含む領域を有する酸化物半導体積層を用いてトランジスタを形成する。

(もっと読む)

表示装置

【課題】半導体素子の電気的な特性のバラツキを低減し、鮮明な多階調カラー表示を可能

にすることを目的とする。

【解決手段】半導体素子に用いられる半導体層の一部を抵抗体として利用する。具体的に

は、半導体素子と、前記半導体素子の有する半導体層と電気的に接続された発光素子と、

を有する表示装置であり、前記半導体層には、前記半導体素子と前記発光素子との間に設

けられた抵抗体とみなせる領域が含まれる。抵抗体とみなせる領域が存在することによっ

て半導体素子の電気的な特性のバラツキの影響を低減することができる。

(もっと読む)

半導体装置

【課題】高い開口率を有し、安定した電気特性を有する薄膜トランジスタを有する、信頼

性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動

回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物

半導体によって構成された駆動回路用薄膜トランジスタと、金属によって構成された駆動

回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体に

よって構成され且つ半導体層が酸化物半導体によって構成された画素用薄膜トランジスタ

と、酸化物導電体によって構成された表示部用配線とを有する。

(もっと読む)

放射線撮像装置、放射線撮像表示システムおよびトランジスタ

【課題】放射線に起因する特性劣化を抑制して信頼性を向上させることが可能なトランジスタを提供する。

【解決手段】放射線撮像装置は、フォトダイオードとトランジスタとを含む画素回路を有する。トランジスタは、基板上の選択的な領域に配設されたゲート電極と、ゲート電極上に第2ゲート絶縁膜を介して設けられた半導体層と、半導体層上に第1ゲート絶縁膜を介して設けられると共にゲート電極に対向するゲート電極と、ゲート電極上に設けられた第1層間絶縁膜と、半導体層に電気的に接続されて設けられたソース電極およびドレイン電極と、一部がゲート電極の端部に対向して設けられたシールド電極層とを備える。第2ゲート絶縁膜、第1ゲート絶縁膜および第1層間絶縁膜のうちの少なくとも1つはシリコン酸化膜を含む。シールド電極層により、放射線の入射によって生じる正電荷の影響による閾値電圧のシフトが抑制される。

(もっと読む)

半導体装置及びその製造方法、並びに、画像表示装置の製造方法

【課題】本開示の目的は、ソース/ドレイン電極の段切れ、ソース/ドレイン電極の損傷といった問題の発生を確実に回避することができ、しかも、島状の平面形状を有するチャネル形成領域を確実に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基材11上にゲート電極12を形成した後、(b)基材11及びゲート電極12上に、チャネル形成領域14を形成すべき領域に凹部20が設けられたゲート絶縁層13を形成し、その後、(c)塗布法に基づき凹部20内に有機半導体材料から成るチャネル形成領域14を形成した後、(d)ゲート絶縁層13の上からチャネル形成領域14の一部の上に亙りソース/ドレイン電極15を形成する各工程から成る。

(もっと読む)

半導体装置

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提

供を目的の一つとする。

【解決手段】記憶素子として機能するトランジスタに蓄積された電荷を保持するためのス

イッチング素子として、酸化物半導体膜を活性層として用いたトランジスタを、記憶装置

の各メモリセルに設ける。また、記憶素子として用いるトランジスタは、第1のゲート電

極と、第2のゲート電極と、第1のゲート電極と第2のゲート電極の間に位置する半導体

膜と、第1のゲート電極と半導体膜の間に位置する第1の絶縁膜と、第2のゲート電極と

半導体膜の間に位置する第2の絶縁膜と、半導体膜に接するソース電極及びドレイン電極

と、を有する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた整流特性の良い非線形素子(例えば、ダイオード)を提供

する。

【解決手段】水素濃度が5×1019/cm3以下である酸化物半導体を有する薄膜トラ

ンジスタにおいて、酸化物半導体に接するソース電極の仕事関数φmsと、酸化物半導体

に接するドレイン電極の仕事関数φmdと、酸化物半導体の電子親和力χが、φms≦χ

<φmdの関係になるように構成する。また、薄膜トランジスタのゲート電極とドレイン

電極を電気的に接続することで、さらに整流特性の良い非線形素子を実現することができ

る。

(もっと読む)

半導体装置及びその製造方法、画像表示装置、並びに、画像表示装置を構成する基板

【課題】バンク層の形成のために専用のマスクを用いたリソグラフィー工程が不要であり、製造工程を簡素化することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上にゲート電極12を形成した後、基体11及びゲート電極12上に絶縁層13を形成し、次いで、絶縁層13上に感光性絶縁材料から成るバンク層20を形成し、その後、基体側から、ゲート電極12を露光用マスクとして用いてバンク層20を露光し、ゲート電極12の上方のバンク層20を除去して、バンク層20に、ゲート電極の上方に位置する開口領域21を形成した後、塗布法に基づき、開口領域21内に半導体材料から成るチャネル形成領域14を形成し、その後、バンク層20上に一対のソース/ドレイン電極15を形成する各工程を備えている。

(もっと読む)

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、酸化物半導体を用いた逆スタガ型薄膜トランジスタで構成する。

同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼

性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジ

カルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中

の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の

変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

イメージセンサ及び電子機器

【課題】後の工程で形成される光電変換層を広く形成することができ、センサの受光面積(開口率)を上げることができる、インテリジェント化された新規な半導体装置を用いた表示装置を提供する。

【解決手段】イメージセンサは、チャネル領域、ソース領域及びドレイン領域を有するトランジスタを有し、トランジスタの上方に絶縁膜を有し、絶縁膜の上方にフォトダイオードを有する。トランジスタはフォトダイオードと重なる位置に設けられている。

(もっと読む)

半導体装置、表示装置

【課題】グローバルシャッタ方式で電荷の蓄積を行うイメージセンサにおいて、蓄積期間

終了時から最後の行を読み出すまでの期間、蓄積電荷保持部からの電荷の流出を極力抑制

することのできる半導体装置の提供を目的とする。

【解決手段】画素がマトリクス状に複数配置されたCMOSセンサ型のイメージセンサに

おいて、画素部の電荷蓄積制御トランジスタ及びリセットトランジスタにチャネル形成領

域が酸化物半導体で形成されたトランジスタを使用し、マトリクス状に配置された全ての

画素で信号電荷蓄積部のリセット動作を行った後、全ての画素でフォトダイオードによる

電荷の蓄積動作を行い、行毎に画素から信号の読み出し動作を行うことで歪みの無い撮像

を可能とする。

(もっと読む)

81 - 100 / 2,024

[ Back to top ]