Fターム[5F110NN74]の内容

Fターム[5F110NN74]の下位に属するFターム

ゲート電極を共有しているもの (6)

Fターム[5F110NN74]に分類される特許

1 - 20 / 349

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物を低減する。また、酸化物半導体膜の被形成面近傍の結晶性を向上させる。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】シリコンを含む下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも酸化物半導体膜と重畳する領域に設けられたゲート電極と、酸化物半導体膜に電気的に接続されたソース電極、及びドレイン電極と、を有し、酸化物半導体膜は、下地絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度で分布する領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、シリコンを含む絶縁膜と、絶縁膜上の酸化物半導体膜と、酸化物半導体膜上のシリコンを含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有する構造とし、少なくともゲート電極と重畳する酸化物半導体膜は、絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%より低い領域を有し、当該領域以外の酸化物半導体膜のシリコン濃度は、当該領域より小さくなる構造とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

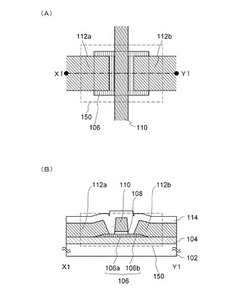

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

半導体装置、及びその作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置を提供する。また、微細化された半導体装置を歩留まりよく提供する。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体膜と、酸化物半導体膜の側面に接して設けられ、かつ酸化物半導体膜よりも膜厚が大きいソース電極層及びドレイン電極層と、酸化物半導体膜、ソース電極層、及びドレイン電極層上に設けられたゲート絶縁膜と、酸化物半導体膜の上面と、ソース電極層及びドレイン電極層の上面との間に生じた段差により生じた凹部に設けられたゲート電極層と、を有する構造である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】ソース電極層及びドレイン電極層上を覆うように酸化物半導体層を成膜した後、ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を研磨により除去する。ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜近傍の酸化物半導体膜に含まれる不純物元素濃度を低減する。また、ゲート絶縁膜近傍の酸化物半導体膜の結晶性を向上させる。また、当該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極、及びドレイン電極と、酸化物半導体膜、ソース電極、及びドレイン電極上に形成されたシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記酸化物半導体膜と重畳する領域に設けられたゲート電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度である領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気的特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】チャネル形成領域、及びチャネル形成領域を挟む低抵抗領域を含む酸化物半導体膜、ゲート絶縁膜、及び上面及び側面を覆う酸化アルミニウム膜を含む絶縁膜が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び酸化アルミニウム膜を含む絶縁膜の上面及び側面の一部に接して設けられる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法

【課題】エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法を提供する。

【解決手段】基板上のゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上のグラフェンチャネルと、グラフェンチャネル上で互いに離隔しているソース電極及びドレイン電極と、ソース電極及びドレイン電極の上面を覆い、グラフェンチャネル上でソース電極とドレイン電極との間にエアギャップを形成するカバーと、を備えるグラフェントランジスタ。前記ソース電極と前記ドレイン電極との間の前記グラフェンチャネルの長さが、10nm〜100nmである。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】チャネル長方向の一方の側面においてソース電極層と接し、チャネル長方向の他方の側面においてドレイン電極層と接する酸化物半導体層を含むトランジスタとすることでソース電極層とドレイン電極層の間の電界を緩和して、短チャネル効果を抑制する。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

記憶素子および信号処理回路

【課題】消費電力を抑えることができる記憶素子、当該記憶素子を用いた信号処理回路を提供する。

【解決手段】一対のインバータ(クロックドインバータを含む)を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を一対のインバータのいずれかの入力あるいは出力である第1のノードに接続し、他方の電極をスイッチング素子の一方の電極に接続する。スイッチング素子の他方の電極は前記インバータの出力あるいは入力である第2のノードに接続する。ここで、第1のノードの電位と第2のノードの電位は互いに逆の位相である。このような接続により、データ回復時における第1のノードと第2のノードの電位差の絶対値を十分に大きくすることができ、データ回復時のエラーを減らせる。

(もっと読む)

1 - 20 / 349

[ Back to top ]