Fターム[5F110PP03]の内容

Fターム[5F110PP03]の下位に属するFターム

Fターム[5F110PP03]に分類される特許

1 - 20 / 2,255

半導体積層体及びその製造方法

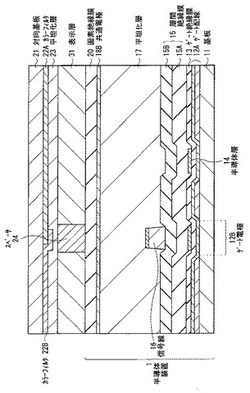

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

薄膜トランジスタ回路基板、及びその製造方法

【課題】厚いゲート絶縁層を有する薄膜トランジスタと、薄いゲート絶縁層を有する薄膜トランジスタとを備えた回路基板を提供する。

【解決手段】ポリシリコン半導体層の上下に、ボトムゲート型薄膜トランジスタのゲート絶縁層とトップゲート型薄膜トランジスタのゲート絶縁膜とを各々設け、トップゲート型薄膜トランジスタのゲート絶縁膜の厚さをボトムゲート型薄膜トランジスタのゲート絶縁層の厚さと異ならせる。

(もっと読む)

酸化物半導体膜の作製方法、半導体装置の作製方法及び半導体装置

【課題】絶縁表面に形成される酸化物半導体膜は、下地界面近傍に非晶質領域が残存してしまい、これがトランジスタなどの特性に影響を与える要因の一つと考えられている。

【解決手段】酸化物半導体膜に接する下地面又は酸化物半導体膜に接する膜を形成する材料の融点を、酸化物半導体を構成する材料の融点よりも高くする。これにより、酸化物半導体膜に接する下地面又は酸化物半導体膜に接する膜との界面近傍まで結晶領域が存在することを可能とする。当該材料として絶縁性の金属酸化物を用いる。金属酸化物として、酸化物半導体膜を構成する材料と同族の材料である酸化アルミニウム、酸化ガリウムなどを用いる。

(もっと読む)

半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

(もっと読む)

薄膜トランジスタ

【課題】バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供する。

【解決手段】表示装置用のボトムゲート型の薄膜トランジスタであって、基板1と、ゲート電極配線2と、ゲート絶縁膜3と、チャネルとなる第1の半導体層4と、第1及び第2のコンタクト層5a、5bとなる第2の半導体層と、ソース又はドレイン電極配線7a、7bとを有し、ソース又はドレイン電極配線7a、7bに対して露出する第2の半導体層の露出部に、絶縁性半導体層6a、6bが形成されている。

(もっと読む)

半導体積層体、半導体デバイス、及びそれらの製造方法

【課題】本発明では、高価かつエネルギー多消費型の大掛かりな装置を必要とせずに、連続性が高い半導体シリコン膜を有する半導体積層体を製造する方法を提供する。また、本発明では、連続性が高い半導体シリコン膜を有する半導体積層体を提供する。

【解決手段】半導体積層体を製造する本発明の方法は、基材の表面上にシリコン粒子分散体膜を形成する工程、シリコン粒子分散体膜を乾燥して、未焼結シリコン膜120を形成する工程、及び未焼結シリコン膜に光200を照射して、半導体シリコン膜130aを形成する工程を含み、かつ基材の表面100aに対する溶融シリコンの接触角が70度以下である。本発明の半導体積層体は、この半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、かつ基材の表面に対する溶融シリコンの接触角が70度以下である。

(もっと読む)

薄膜形成基板、薄膜形成方法、及び表示装置の製造方法

【課題】基板に生じるクラックの発生を防止した薄膜形成方法を提供する。

【解決手段】薄膜形成方法は、基板を準備する基板準備工程と、基板上に第1薄膜を形成する第1薄膜形成工程と、第1薄膜に対して光線を相対走査して照射することにより、第1薄膜を結晶化する結晶化工程と、結晶化工程において第1薄膜に生じる熱の基板への伝導量を低下させる緩和層を、結晶化工程の前に、基板の端部領域及び基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

(もっと読む)

液晶表示装置、表示モジュール及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

薄膜トランジスタ、その製造方法、及び表示装置

【課題】酸化物薄膜の結晶配置の方向を制御し、良質な酸化物薄膜を提供する。

【解決手段】薄膜トランジスタのチャネル層となる酸化物層と絶縁層からなる積層構造であって、

前記酸化物層において、25×25μm2における表面電位の最大値と最小値の電位差が60mV以下であることを特徴とする積層構造。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極や走査線(ゲート線)及びデータ線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供する。

【解決手段】半導体膜107と基板との間に第1の絶縁膜を介して設けられた第1の配線102を、半導体膜107と重ねて設け、遮光膜として用いる。さらに半導体膜上にゲート絶縁膜として用いる第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極と第2の配線134を形成する。第1及び第2の配線は、第1及び第2の絶縁膜を介して交差する。第2の配線134の上層には、層間絶縁膜として第3の絶縁膜を形成し、その上に画素電極147を形成する。画素電極147は、第1の配線及び第2の配線とオーバーラップさせて形成することが可能であり、反射型の表示装置において画素電極147の面積を大型化できる。

(もっと読む)

薄膜半導体装置及びその製造方法

【課題】チャネル保護型の薄膜トランジスタにおいて、オフ特性及び信頼性に優れた薄膜半導体装置の製造方法を提供する。

【解決手段】基板1を準備する第1工程と、基板1上にゲート電極2を形成する第2工程と、ゲート電極2上に第1絶縁膜としてゲート絶縁膜3を形成する第3工程と、ゲート絶縁膜3上に非結晶質の半導体薄膜4aを形成する第4工程と、非結晶質の半導体薄膜4a上に第2絶縁膜としてチャネル保護膜5を形成する第5工程と、チャネル保護膜5の上方からレーザー光を照射することにより、非結晶質の半導体薄膜4aを結晶化させて結晶化領域を形成する第6工程と、結晶化領域の上方にソース電極7S及びドレイン電極7Dを形成する第7工程と、を含み、第5工程において、チャネル保護膜5は、前記レーザー光に対して透明となるように形成される。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 光リーク電流を抑制した高い耐光性を有するTFTを、製造工程を簡素化することにより低コストで実現する。

【解決手段】 TFT100は、絶縁基板107としてのガラス基板上に形成された遮光膜113と、遮光膜113上に形成された絶縁膜112と、絶縁膜112上に形成された半導体膜111と、半導体膜111上に形成されたゲート絶縁膜104とを基本的に有する。遮光膜113、絶縁膜112及び半導体膜111の三層から成る積層体100aは、各層が同時にパターニングされている。そして、積層体100aの各層がシリコン又はシリコンを含む材料から成る。

(もっと読む)

半導体装置

【課題】無線通信により交信可能な半導体装置において、個体識別子を容易に付けることができるようにする。

【解決手段】薄膜トランジスタ119と、薄膜トランジスタ上に第1の層間絶縁膜156と、第1の層間絶縁膜上の、ソース領域またはドレイン領域の一方に電気的に接続される第1の電極114と、ソース領域またはドレイン領域の他方に電気的に接続される第2の電極110と、第1の層間絶縁膜、第1の電極、及び第2の電極上に形成された第2の層間絶縁膜135と、第2の層間絶縁膜上の、第1の電極または第2の電極の一方に電気的に接続される第1の配線177と、第2の層間絶縁膜上の、第1の電極または第2の電極の他方に電気的に接続されない第2の配線178とを有し、第2の配線と前記第1の電極または第2の電極の他方は、第2の層間絶縁膜中の分断領域169によって、電気的に接続されない半導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

装置の作製方法

【課題】剥離前の形状及び特性を保った良好な状態で転置工程を行えるような、剥離工程

を用いて半導体装置及び表示装置を作製できる技術を提供する。よって、より高信頼性の

半導体装置及び表示装置を装置や工程を複雑化することなく、歩留まりよく作製できる技

術を提供することも目的とする。

【解決手段】透光性を有する第1の基板上に光触媒物質を有する有機化合物層を形成し、

光触媒物質を有する有機化合物層上に素子層を形成し、光を第1の基板を通過させて、光

触媒物質を有する有機化合物層に照射し、素子層を前記第1の基板より剥離する。

(もっと読む)

半導体装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

1 - 20 / 2,255

[ Back to top ]