Fターム[5F110QQ08]の内容

Fターム[5F110QQ08]に分類される特許

1 - 20 / 698

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程により、ソース電極層及びドレイン電極層を形成後、酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の不純物を除去する工程を行う。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

液晶表示装置、表示モジュール及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

薄膜形成基板、薄膜形成方法、及び表示装置の製造方法

【課題】基板に生じるクラックの発生を防止した薄膜形成方法を提供する。

【解決手段】薄膜形成方法は、基板を準備する基板準備工程と、基板上に第1薄膜を形成する第1薄膜形成工程と、第1薄膜に対して光線を相対走査して照射することにより、第1薄膜を結晶化する結晶化工程と、結晶化工程において第1薄膜に生じる熱の基板への伝導量を低下させる緩和層を、結晶化工程の前に、基板の端部領域及び基板を切断する際に切断線が通る領域の少なくとも一方を含む領域に形成する緩和層形成工程とを含む。

(もっと読む)

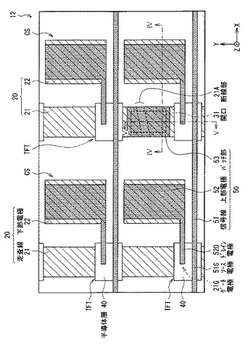

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供することを課題の一とする。また、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。また、暗所でも長時間の利用が可能な、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。

【解決手段】高純度化された酸化物半導体を用いた薄膜トランジスタで回路を構成し、画素が一定の状態(映像信号が書き込まれた状態)を保持することを可能とする。その結果、静止画を表示する場合にも安定した動作が容易になる。また、駆動回路の動作間隔を長くできるため、表示装置の消費電力を低減できる。また、自発光型の表示装置の画素部に蓄光材料を適用し、発光素子の光を蓄えれば、暗所でも長時間の利用が可能になる。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

半導体装置

【課題】インバータ回路を構成する直列接続された素子を備えた半導体装置において、その直列接続の高電位配線の影響による耐圧低下が生じるのを防止する半導体装置の提供。

【解決手段】第1および第2の素子は、各々、電流のスイッチングを行うトランジスタと、還流を行うダイオードとを含み、かつ、トランジスタの第1主電極とダイオードの第1主電極が電気的に接続され、トランジスタの第2主電極とダイオードの第2主電極が電気的に接続され、第1の素子および第2の素子は、第1の素子におけるトランジスタの第1主電極と、第2の素子におけるトランジスタの第2主電極が電気的に接続され、かつ、半導体基板を平面視したときに、第1の素子におけるトランジスタの第1主電極とドリフト領域の間の導電性半導体領域と、第2の素子におけるトランジスタの第2主電極とドリフト領域の間の導電性半導体領域とが対向するように、配置されていることを特徴とする。

(もっと読む)

駆動用回路基板およびその製造方法並びに表示装置および電子機器

【課題】工程数が少なく、且つ、材料の利用効率が向上した駆動用回路基板およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本開示の表示装置は、一対のソース・ドレイン電極と、チャネル領域を形成すると共に、ソース・ドレイン電極に接して設けられた有機半導体層と、ソース・ドレイン電極まで貫通する貫通孔を有すると共に、有機半導体層およびソース・ドレイン電極上に設けられた少なくとも1層からなる絶縁層と、チャネル領域に対応する位置に設けられたゲート電極と、貫通孔を介して前記ソース・ドレイン電極に電気的に接続されると共に、ゲート電極と同一材料、且つ、同一膜厚で絶縁層上に設けられた画素用電極とを備える。

(もっと読む)

トップゲート型アクティブマトリックス基板、およびその製造方法

【課題】データ配線が銀や銀合金により形成されており、またデータ配線に、ゲート絶縁層によって被覆されておらずむき出しとなっている部分があった場合でも、当該むき出しとなっている部分でマイグレーション現象が生じることがないトップゲート型アクティブマトリックスを提供する。

【解決手段】基材と、前記基材上に直接または間接的に形成された、ソース電極、ドレイン電極、半導体層、ゲート絶縁層、ゲート電極、層間絶縁層、画素電極、および前記ソース電極と接続したデータ配線と、を有するトップゲート型アクティブマトリックス基板において、前記ソース電極と前記データ配線をともに銀または銀合金で形成し、前記ゲート電極を銀または銀合金以外で形成し、前記データ配線においてむき出しとなっている部分をゲート電極と同じ材質からなる被覆層によって被覆する。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

【解決手段】SOI基板を用いた半導体装置の製造方法において、活性層基板を酸化して埋め込み酸化膜4bを生成する工程と、支持基板3表面に、MOSトランジスタ1の閾値電圧を決定するためのチャネルドープ10を行う工程と、支持基板3と活性層基板5とを前記埋め込み酸化膜を介して貼り合せる工程と、活性層基板を部分的に除去し埋め込み酸化膜4aを露出させる工程と、埋め込み酸化膜4a上にゲート電極6aを形成する工程と、を含む半導体装置の製造方法とする。

(もっと読む)

液晶表示装置

【課題】製造コストを削減するとともに歩留まりを向上し、かつプロセス設計が容易である液晶表示装置を提供すること。

【解決手段】液晶表示装置1において、半導体層ASIと半導体層ASIの液晶材側の面に形成された金属層Mとの積層部分であり、かつ画素電極MITの液晶材側の面に重なる部分である重なり部50を含むソース電極SD2を有し、第2の絶縁層PAS2は、ソース電極SD2の液晶材側の面から重なり部の50端部、及び画素電極MITの一部を開口するように形成されており、ソース電極SD2の液晶材側の面から重なり部50の端部上、及び画素電極MIT上に、ソース電極SD2の液晶材側の面から重なり部50の端部、及び画素電極MITを導通させる導体膜70が形成されている。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

半導体装置

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

薄膜トランジスタ、画像表示装置

【課題】酸化物半導体層のバックチャネル部を半導体層成膜後の薄膜トランジスタ作製工程によるダメージから保護し、良好なトランジスタ特性を得ると共に、薄膜トランジスタ作製の工程数を削減することである。

【解決手段】基板1と、基板1上に設けられたゲート電極2と、基板1上に設けられ、ゲート電極2を覆うゲート絶縁膜3と、ゲート絶縁膜3上に設けられ、アモルファス酸化物からなる半導体層4と、半導体層4上に設けられた保護膜5と、ゲート絶縁膜3上に設けられたソース電極6、及びドレイン電極7と、を備え、保護膜5を、金属材料の化成処理、又は陽極酸化によって形成する。

(もっと読む)

1 - 20 / 698

[ Back to top ]