Fターム[5F110QQ12]の内容

Fターム[5F110QQ12]に分類される特許

1 - 20 / 257

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

液晶表示装置の製造方法

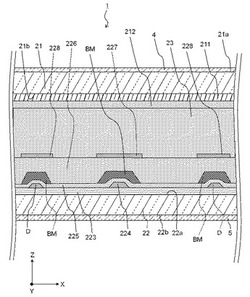

【課題】本発明の液晶表示装置の製造方法によれば、高い表示品位を有する液晶表示装置を製造できる。

【解決手段】液晶表示装置の製造方法は、第2基板22の主面21a上に遮光膜BMを形成する工程と、遮光膜BMを覆うように第1絶縁膜226を形成する工程と、第1絶縁膜226上に透光性の導体層100を形成する工程と、導体層100上にレジストREを形成する工程と、第2基板22の反対主面22b側から、遮光膜BMと重ならない部分のレジストREを露光する工程と、レジストRE上にマスクPMを配置して、レジストREのうち遮光膜BMの形成領域上に位置するレジストREの一部をマスクPM側から露光する工程と、導体層100の一部を露出させる工程

と、導体層100の露出した一部をエッチングし、レジストを除去して、遮光膜BMの形成領

域上に信号電極228および共通電極227を形成する工程とを含むことを特徴とする。

(もっと読む)

薄膜トランジスタ、その製造方法、および表示装置

【課題】酸化物半導体を用いた低温プロセスで形成する信頼性の高い薄膜トランジスタ、その製造方法、および表示装置を提供する。

【解決手段】薄膜トランジスタ1は、基板100と、前記基板上の一部に設けられたゲート電極110と、前記ゲート電極を覆う第1の絶縁膜120と、前記第1の絶縁膜を介して前記ゲート電極上に設けられた酸化物半導体膜130と、前記酸化物半導体膜上の一部に設けられた第2の絶縁膜150と、前記酸化物半導体膜から露出する酸化物半導体膜の一部と接続されたソース電極140Sおよびドレイン電極140Dと、を備え、前記酸化物半導体膜はInと、Gaと、Znのうち少なくとも一つの元素を含む酸化物半導体を有し、前記第1の絶縁膜中に含有される水素濃度が5×1020atm/cm−3以上であり、かつ、前記第2の絶縁膜中に含有される水素濃度が1019atm/cm−3以下である。

(もっと読む)

半導体装置、薄膜トランジスタ基板および表示装置

【課題】金属酸化物を用いた絶縁膜を低温プロセスで結晶化することが可能で、これによりガラス基板やプラスチック基板上に特性の向上が図られた素子を設けることが可能な半導体装置を提供する。

【解決手段】基板上に、金属酸化物を用いた絶縁膜と半導体薄膜とが積層形成された半導体装置であって、絶縁膜はゲート絶縁膜として用いられ、ゲート絶縁膜に接する側にゲート電極が積層形成され、絶縁膜および半導体薄膜は結晶化され、かつ、ゲート電極と重なる部分の結晶性が他の部分の結晶性よりも高いものである。

(もっと読む)

表示装置

【課題】熱処理による特性変動を抑制した酸化物半導体を用いた表示装置を提供する。

【解決手段】実施形態によれば、絶縁層と、絶縁層上のゲート電極と、ゲート電極上にゲート絶縁膜を介して設けられ酸化物層より形成された半導体層と、半導体層の上において、ゲート電極を挟むように離間して設けられたソース電極及びドレイン電極と、を含む薄膜トランジスタと、ソース電極及びドレイン電極のいずれかに接続され、前記酸化物層より形成され前記半導体層よりも電気抵抗が低い画素電極と、画素電極に与えられる電気信号によって光学特性の変化と発光との少なくともいずれかを生ずる光学素子と、画素電極の下に設けられゲート絶縁膜と同じ材料で形成された膜と、を備え、ゲート電極の上のゲート絶縁膜の半導体層の側の表面は、画素電極の下に設けられた膜の画素電極の側の表面よりも平滑性が高い表示装置が提供される。

(もっと読む)

電子デバイスの製造方法

【課題】転写歩留まりを向上することが可能な電子デバイスの製造方法を提供することを目的とする。

【解決手段】薄膜トランジスタ(TFT)19の製造方法において、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aにガスバリア層7が形成されている。そのため、ガスバリア層7側からスタンプ5を空気で加圧する際に、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aから、半導体膜8および絶縁膜9が形成される面に、加圧した空気が抜けにくくなる。これにより、スタンプ5を基板1に押し付けることを持続することができるので、スタンプ5に形成された半導体膜8および絶縁膜9と基板1との密着性を増すことができる。したがって、基板1に転写されない半導体膜8および絶縁膜9が減少し、薄膜転写の歩留まりを向上させることができる。

(もっと読む)

半導体装置及びその製造方法、画像表示装置、並びに、画像表示装置を構成する基板

【課題】バンク層の形成のために専用のマスクを用いたリソグラフィー工程が不要であり、製造工程を簡素化することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基体11上にゲート電極12を形成した後、基体11及びゲート電極12上に絶縁層13を形成し、次いで、絶縁層13上に感光性絶縁材料から成るバンク層20を形成し、その後、基体側から、ゲート電極12を露光用マスクとして用いてバンク層20を露光し、ゲート電極12の上方のバンク層20を除去して、バンク層20に、ゲート電極の上方に位置する開口領域21を形成した後、塗布法に基づき、開口領域21内に半導体材料から成るチャネル形成領域14を形成し、その後、バンク層20上に一対のソース/ドレイン電極15を形成する各工程を備えている。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】本発明は、低温かつ簡便で安価な製造工程により作製可能であり、トランジスタ特性に優れる、ダブルゲート構造を有する薄膜トランジスタおよびその製造方法を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成された第1ゲート電極と、上記第1ゲート電極を覆うように形成された第1ゲート絶縁層と、上記第1ゲート絶縁層上に形成され、低抵抗領域であるソースコンタクト領域およびドレインコンタクト領域ならびに高抵抗領域であるチャネル領域を有する酸化物半導体層と、上記ソースコンタクト領域に接して形成されたソース電極と、上記ドレインコンタクト領域に接して形成されたドレイン電極と、上記酸化物半導体層上に形成され、絶縁性有機材料を含む第2ゲート絶縁層と、上記第2ゲート絶縁層上に形成された第2ゲート電極とを有することを特徴とする薄膜トランジスタを提供する。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体装置の作製方法、および半導体装置

【課題】低温プロセスを実現する半導体装置の作製方法、及び半導体装置を提供する。

【解決手段】結晶構造を有する半導体層の一部にp型を付与する不純物元素及び水素を同時に添加することによって、一部の上層部分を非晶質化するとともに、一部の下層部分に結晶質を残存させ、加熱処理を行うことによって、一部の中の水素を拡散させる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置

【課題】薄膜トランジスタの寄生容量を低減することが可能な半導体装置を提供する。

【解決手段】 絶縁基板と、前記絶縁基板上に形成されたゲート電極と、前記ゲート電極を覆う第1絶縁膜と、前記第1絶縁膜上に形成され、前記ゲート電極の直上に位置する第1領域と、前記第1領域を挟んだ両側に位置する第2領域及び第3領域と、前記第2領域に積層されるとともに前記第2領域よりも低抵抗な第4領域と、前記第3領域に積層されるとともに前記第3領域よりも低抵抗な第5領域と、を有する酸化物半導体層と、前記酸化物半導体層の前記第1領域を覆うとともに、前記第4領域の一部及び前記第5領域の一部をそれぞれ露出する第2絶縁膜と、前記第2絶縁膜から露出した前記第4領域に電気的に接続されたソース電極と、前記第2絶縁膜から露出した前記第5領域に電気的に接続されたドレイン電極と、を備えたことを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いて、トランジスタのしきい値電圧を変化させる。

【解決手段】第1のチャネル形成領域を有する第1の半導体層と、第2のチャネル形成領域を有する第2の半導体層に対して、それらの上に形成された薄膜の応力を用いて、トランジスタのしきい値電圧を異ならせることができる。これらを電気的に接続することで、E/D MOS回路を提供できる。

(もっと読む)

半導体装置及び電子機器

【課題】薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】第1の半導体層に設けられた第1のゲート電極と、第2の半導体層に設けられた第2のゲート電極と、第1の半導体層と第2の半導体層に接して設けられた第1の絶縁層と、第1の絶縁層が設けられた第1の半導体層の一方の面の反対側に設けられた第2の絶縁層と、第1の絶縁層が設けられた第2の半導体層の一方の面の反対側に設けられた第2の絶縁層及び第3の絶縁層と、を有し、第1の半導体層には第2の絶縁層により応力が加わり、第2の半導体層には第2の絶縁層と第3の絶縁層により応力が加わることで、第1の半導体層及び第2の半導体層に加わる応力が異なる。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

転写印刷用スタンプ製造方法および電子デバイス

【課題】気泡の除去を容易にするとともに変形を抑えた転写印刷用スタンプの製造方法および電子デバイスを提供する。

【解決手段】転写印刷用スタンプ5は、通気性シート3に樹脂を含浸させて通気性シート3を第1樹脂層100中に含まれるように構成させている。これにより、第1樹脂層100中に含まれる気泡を通気性シート3の隙間を通して容易に脱気させることができる。そのため、気泡によるパターン欠損などの問題を解消することができる。また、通気性シート3は、第1樹脂層100中で骨格として機能するので、転写印刷用スタンプ5の強度を高めることができ、変形を抑えることができる。そのため、転写の寸法精度を高めることができ、大面積化させることができる。

(もっと読む)

薄膜トランジスタ、表示装置用電極基板およびそれらの製造方法

【課題】ボトムコンタクト構造で、かつセルフアラインのTAOS TFT、このTAOS TFTを用いた表示装置用電極基板およびそれらの製造方法を得る。

【解決手段】ガラス基板11上に形成されたゲート電極12と、ゲート電極12上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に、ゲート電極12と重ならないように形成されたソース電極14およびドレイン電極15と、ゲート電極12、ソース電極14およびドレイン電極15上に、ゲート電極12を跨いでソース電極14とドレイン電極15とを繋ぐように形成された第1、第2TAOS層16、17と、第1、第2TAOS層16、17上に、ゲート電極12をマスクとしたガラス基板11側からの露光により形成された島状絶縁膜18とを備え、第1、第2TAOS層16、17の島状絶縁膜18と重ならない領域の抵抗値は、島状絶縁膜18と重なる領域の抵抗値よりも低くなっている。

(もっと読む)

薄膜トランジスタおよび表示装置用電極基板の製造方法

【課題】ボトムコンタクト構造で、かつセルフアラインのTAOS TFTを、大掛かりな設備投資や成膜装置の設置場所の確保を要することなく量産することができる製造方法、およびこのTAOS TFTを用いた表示装置用電極基板の製造方法を得る。

【解決手段】ゲート電極12、ソース電極14およびドレイン電極15上に形成された第1、第2TAOS層16、17に窒素プラズマを照射するステップと、第1、第2TAOS層16、17を窒素雰囲気中でアニールするステップと、第1、第2TAOS層16、17上に、ゲート電極12をマスクとしたガラス基板11側からの露光により樹脂絶縁膜である島状絶縁膜18を形成するステップと、ガラス基板11の全面に、島状絶縁膜18をマスクとして、島状絶縁膜18側からプラズマを照射するステップとを備える。

(もっと読む)

薄膜トランジスタおよび表示装置用電極基板の製造方法

【課題】ボトムコンタクト構造で、かつセルフアラインのTAOS TFTにおいて、TAOS層のソース領域およびドレイン領域に相当する領域を十分に低抵抗化できる製造方法、およびこのTAOS TFTを用いた表示装置用電極基板の製造方法を得る。

【解決手段】ゲート電極12、ソース電極14およびドレイン電極15上に、ゲート電極12を跨いでソース電極14とドレイン電極15とを繋ぐように第1、第2TAOS層16、17を形成するステップと、第1、第2TAOS層16、17上に、ゲート電極12をマスクとしたガラス基板11側からの露光により島状絶縁膜18を形成するステップと、ガラス基板11の全面に、島状絶縁膜18をマスクとして、島状絶縁膜18側からプラズマを照射するステップと、島状絶縁膜18の周囲に露出した第1、第2TAOS層16、17をアルカリ溶液に浸すステップとを備える。

(もっと読む)

1 - 20 / 257

[ Back to top ]