Fターム[5F110QQ17]の内容

Fターム[5F110QQ17]に分類される特許

1 - 20 / 694

半導体装置およびその製造方法

半導体装置およびその製造方法

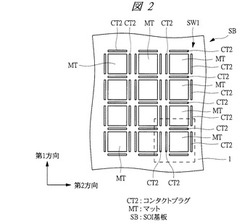

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

化合物半導体

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。Si基板上のシリコン酸化膜の上に単結晶のSiC膜を形成し、トレンチによる絶縁物分離構造とし、その中に結晶欠陥が多くてもその影響を避ける新構造の素子の発明である。

【解決手段】SiC膜に形成したMOSFETなどの半導体素子を構成しているPN接合面において基板面と並行となる面にあるPN接合に印加される電界が、SiC膜が形成されているシリコン酸化膜や基板となるSi層により緩和されて、さらには基板電位をドレイン電圧とは逆方向の電位とすることにより大きく電界緩和されて、SiC膜に発生している基板と垂直方向の結晶欠陥の結晶欠陥降伏電圧以下とすることを特徴とする素子構造を持った半導体装置。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

SOI基板の作製方法および作製装置

【課題】単結晶半導体基板とベース基板の界面に空気層が残ることに起因した、ベース基板から単結晶半導体基板を引き剥がした際に生じる転載不良領域の発生が抑制された、高品位なSOI基板の作製方法および作製に用いる貼り合わせ装置を提供することを課題とする。

【解決手段】ボンド基板を、ベース基板の設置面に対して傾斜角を持たせた状態で貼り合わせる。これにより、貼り合わせ開始箇所を限定できる。また、ボンド基板の一部が支持台からはみ出し、且つ、支持台からはみ出した部分がベース基板に最も近くなる状態にボンド基板を設置した。これにより、ボンド基板とベース基板の接触箇所下部には支持台がなく、ボンド基板の一部は支持台の端部を支点として支持台から浮かんだ状態となり、ベース基板に近づいた部分から順次貼り合わせが進むため、ボンド基板とベース基板の界面に空気層残りが生じることなく安定した貼り合わせを行うことができる。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

【解決手段】SOI基板を用いた半導体装置の製造方法において、活性層基板を酸化して埋め込み酸化膜4bを生成する工程と、支持基板3表面に、MOSトランジスタ1の閾値電圧を決定するためのチャネルドープ10を行う工程と、支持基板3と活性層基板5とを前記埋め込み酸化膜を介して貼り合せる工程と、活性層基板を部分的に除去し埋め込み酸化膜4aを露出させる工程と、埋め込み酸化膜4a上にゲート電極6aを形成する工程と、を含む半導体装置の製造方法とする。

(もっと読む)

固体素子を有するデバイスの製造方法

【課題】固体素子を損傷させにくい、固体素子を有するデバイスの製造方法を提供する。

【解決手段】可撓性基板1及び剛性基板2を準備する基板準備工程と、可撓性基板の片側に紫外線3を部分的に照射して紫外線照射領域4と紫外線非照射領域を形成する第1の紫外線照射工程と、剛性基板の片側に紫外線を照射して紫外線照射領域5を形成する第2の紫外線照射工程と、可撓性基板の紫外線照射領域9及び剛性基板の紫外線照射領域11を片側同士が対向するように接触させて、可撓性基板及び剛性基板が直に固着している複合体6を形成する複合体形成工程と、複合体の可撓性基板の紫外線非照射領域10に固体素子7を形成する固体素子形成工程と、複合体の可撓性基板の紫外線非照射領域で可撓性基板を切断する可撓性基板切断工程と、複合体から剛性基板を分離する剛性基板分離工程と、を有する製造方法。

(もっと読む)

電磁波剥離性フレキシブルデバイス用基板およびそれを用いた電子素子の製造方法

【課題】本発明は、安定的に電子素子部を形成可能な電磁波剥離性フレキシブルデバイス用基板を提供することを主目的とする。

【解決手段】本発明は、可撓性を有する金属基材と、上記金属基材の少なくとも一方の表面上に形成された絶縁層と、上記金属基材の他方の表面上に形成され、電磁波剥離性を有する電磁波剥離性粘着樹脂を含む電磁波剥離性粘着層と、を有することを特徴とする電磁波剥離性フレキシブルデバイス用基板を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置およびその製造方法

【課題】フォトダイオードとトランジスタとが絶縁膜を介して同一の半導体基板に形成された半導体装置の、フォトダイオードを形成する半導体層と絶縁膜との界面のリーク電流を小さくする。

【解決手段】一導電型の半導体層11と、半導体層の主面151に設けられた反対導電型の半導体領域182と、半導体層11の主面151に半導体領域182と離間して設けられた一導電型で半導体層11より高不純物濃度の半導体領域191、192と、少なくとも半導体領域182と半導体領域と191、192の間の半導体層11の主面151に設けられた一導電型で半導体層11より高不純物濃度で半導体領域191、192よりも低不純物濃度の半導体領域99と、を備えるフォトダイオード30と、半導体層11の主面151上に設けられた絶縁層10と、絶縁層10上に設けられ、トランジスタ素子40が形成された半導体層9と、を備える。

(もっと読む)

TFT基板の製造方法およびレーザーアニール装置

【課題】ダミー基板および金属膜から、TFT基板を金属膜から容易に剥離するとともに、TFT基板とその支持基板とを分離することを可能とする、TFT基板の製造方法を提供する。

【解決手段】第一基板101と第二基板102との間に、機能素子を含む構造体103を挟んでなるTFT基板100の製造方法であって、ダミー基板104の上に、柱状の結晶粒子からなる金属膜105と、第一基板101と、構造体103と、第二基板102とを順に形成した後に、金属膜105に、レーザー光Lの焦点Laを集光させて、ダミー基板104と金属膜105とを、第一基板101と構造体103と第二基板102から分離する工程を、少なくとも有する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】チャネル領域にシリコンを含まない材料を用いる半導体装置であって、微細化に伴いゲート絶縁層が薄膜化されても、ゲートリーク電流が抑制された半導体装置を提供する。

【解決手段】ゲート絶縁層として熱酸化シリコン層を用いる。熱酸化シリコン層を用いることで、CVD法やスパッタリング法で形成された酸化シリコン層を用いる場合よりゲートリーク電流を抑制することができる。ゲート絶縁層に熱酸化シリコン層を用いるために、チャネル領域を含む半導体層を形成する基板とは別にシリコン基板を用意し、シリコン基板上に熱酸化シリコン層を形成する。そして熱酸化シリコン層を、チャネル領域を含む半導体層に貼り合わる。このようにして、半導体層の上に熱酸化シリコン層を形成し、熱酸化シリコン層をゲート絶縁層として用いたトランジスタを形成する。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

装置の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する表示装置を作製する

ための技術を提供する。

【解決手段】固定基板上に、剥離層となる非晶質シリコン膜を介して樹脂基板を形成する

工程と、前記樹脂基板上に少なくともTFT素子を形成する工程と、前記非晶質シリコン

膜にレーザー光を照射することにより、前記非晶質シリコン膜において前記固定基板から

前記樹脂基板を剥離する工程とを行い、前記樹脂基板を用いた柔軟性を有する表示装置を

作製する。

(もっと読む)

化合物半導体の形成方法

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。

Si基板上のシリコン酸化膜の上に単結晶のSiC膜やGaN膜に形成したMOSFETなどの素子をアニールする手法を開示する。

【解決手段】光学ランプからの光をレンズで集光する手段、或いはレーザ光など高温度を発生させる手段によりSiCなど化合物半導体の表層部はSi基板の融点を越えるような高温度として、Si基板部はその融点よりも十分低い温度となるような冷却部を設けてSi基板を保持するステージを設けたことを特徴とするアニーリング装置。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

発光装置

【課題】開口率の向上された発光装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線とを、プラスチック基板上に有する発光装置であって、配線は、容量の上に設けられ、容量は、配線の少なくとも一部と重なる領域を有する。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

EL表示装置

【課題】開口率を向上することができるEL表示装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線と有するEL表示装置である。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

1 - 20 / 694

[ Back to top ]