Fターム[5F140AA02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 低電力化 (156)

Fターム[5F140AA02]に分類される特許

1 - 20 / 156

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置

【課題】アバランシェ降伏電流が流れている状態において寄生トランジスタのターンオンを抑制することにより、十分なアバランシェ耐量を確保することのできる半導体装置を提供する。

【解決手段】基板の表面ではn型領域とベース領域とが隣接している。エミッタ/ソース領域はベース領域内でn型領域から離れている。ゲート絶縁膜はn型領域とエミッタ/ソース領域との間でベース領域を覆い、その上にゲート電極が形成されている。ドレイン領域とコレクタ領域とはn型領域内でベース領域から離れている。コレクタ接続領域はn型領域内で、ベース領域、ドレイン領域、及びコレクタ領域のいずれからも離れている。ドレイン電極はドレイン領域に接続されている。コレクタ電極はコレクタ領域とコレクタ接続領域とに接続されている。ゲートターンオフ状態でドレイン電極にアバランシェ降伏電流が流れるとき、コレクタ電極の電位がドレイン電極の電位よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFET特性を改善することができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置は、基板と、基板の上方に形成されたゲート電極と、ゲート電極の下に形成されたゲート絶縁膜と、ゲート絶縁膜の下に、シリコン基板の材料に比して広いバンドギャップを持つチャネル層材料により形成されたチャネル層と、チャネル方向に沿ってチャネル層を挟むように基板に形成されたソース領域とドレイン領域と、チャネル層とソース領域との間のシリコン基板に、チャネル層のソース側端部とオーバーラップするように形成され、且つ、チャネル層とともにキャリアがトンネルするヘテロ界面を成すソースエクステンション層とを有する。

(もっと読む)

半導体装置

【課題】短チャネルでもオフ特性の優れたトランジスタ等の半導体装置を提供する。

【解決手段】ソース102aの周囲をエクステンション領域103aおよびハロー領域105a、ドレイン102bの周囲をエクステンション領域103bおよびハロー領域105bで取り囲むように配置し、また、不純物濃度の低い基板101がソース102a、ドレイン102bと接しない構造とする。さらに、ゲート絶縁物109を介して高仕事関数電極104を設け、基板101の表面近傍にエクステンション領域103aおよびエクステンション領域103bより侵入する電子を排除する。このような構造とすることにより、短チャネルでもチャネル領域の不純物濃度を低下させることができ、良好なトランジスタ特性を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートメタル電極とHigh−k膜とを用いた半導体装置において、低抵抗なゲートメタル電極により仕事関数を調整できるようにする。

【解決手段】半導体装置は、Nウェル102の上に形成された第1のゲート絶縁膜109と、該第1のゲート絶縁膜109の上に形成された第1のゲート電極とを備えている。第1のゲート絶縁膜109は、第1の高誘電体膜109bを含み、第1のゲート電極は、第1の高誘電体膜109bの上に形成され、TiN層110aとAlN層110bとが交互に積層された第1の実効仕事関数調整層110を含む。TiN層110aはAlN層110bよりも抵抗が小さく、且つ、AlN層110bはTiN層110aよりも実効仕事関数の調整量が大きい。

(もっと読む)

半導体デバイス及びその駆動方法

【課題】半導体デバイスの小面積化を実現する。

【解決手段】電極と、第1絶縁体と、バンドギャップが2eV以上の第1半導体と、第2絶縁体と、第2半導体とが積層されており、第1半導体に接する1つ以上の電極と、第2半導体に接する2つ以上の電極とを少なくとも備えることを特徴とする半導体デバイス。

(もっと読む)

窒化物半導体装置

【課題】窒化物半導体装置において、高温且つ高電圧下のスイッチング時においても電流コラプスによるオン抵抗の増大が生じないようにする。

【解決手段】基板1上には、バッファ層2、GaNからなるチャネル層3及びアンドープAlGaNからなるバリア層4が順次形成されている。チャネル層3は、該チャネル層3の下部にp型不純物層3aを有し、その上にアンドープ層3bを有している。バリア層4及びチャネル層3の端部が除去されており、露出したバリア層4及びチャネル層3の側面と接するように、それぞれソース電極5及びドレイン電極6が設けられている。バリア層4上におけるソース電極5とドレイン電極6との間の領域にはゲート電極7が設けられている。

(もっと読む)

半導体装置および電力変換器

【課題】部品点数を増やすことなく、SiC半導体装置の結晶劣化の進行を抑制することが可能な半導体素子を提供する。

【解決手段】p型コレクタ域91およびn型コレクタ領域92を含むコレクタ層93と、n型半導体層20と、p型ボディ領域30と、n型エミッタ領域40と、ボディ領域30に接して形成されたチャネルエピ層50と、エミッタ電極45と、ゲート絶縁膜60と、ゲート電極65と、コレクタ電極70とを備える構造とする。双方向導通IGBT100のゲート電極65に印加する電圧が閾値電圧よりも小さい場合、エミッタ電極45からチャネルエピ層50を介してコレクタ電極70へ電流を流すダイオードとして機能させる。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】金属電極と該金属電極の上に形成されたシリコン電極とを有するゲート電極を備えた電界効果型トランジスタを実現する際に、金属電極とシリコン電極との界面に生じる界面抵抗を低減できるようにする。

【解決手段】半導体装置は、半導体基板100における第1の活性領域103aに形成されたP型の電界効果型トランジスタを備えている。第1の電界効果型トランジスタは、第1の活性領域103aの上に形成された第1のゲート絶縁膜106aと、第1のゲート絶縁膜106aの上に形成された第1のゲート電極115aとを有している。第1のゲート電極115aは、第1のゲート絶縁膜106aの上に形成された第1の金属電極107aと、該第1の金属電極107aの上に形成された第1の界面層110aと、該第1の界面層110aの上に形成された第1のシリコン電極111aとを有している。

(もっと読む)

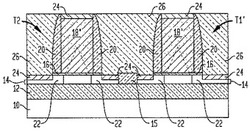

半導体装置及びその製造方法

【課題】LDMOSトランジスタに係る半導体装置の高速動作を可能とする。

【解決手段】P型ウエル層3の表面に形成された複数の素子分離膜4の中央部に開口溝5を形成する。開口溝5の側壁から開口溝5の内側に向かってゲート絶縁膜6を介して延在するゲート電極7を形成する。ゲート電極7をマスクにしてセルフアラインでボロンの斜めイオン注入により開口溝5内のP型ウエル層3にP型ボディ層8を形成する。

ゲート電極7をマスクに砒素のイオン注入によりP型ボディ層8にN+型ソース層9を、同時に2つの素子分離膜4間のP型ウエル層3にN+型ドレイン層10を形成する。素子分離膜4の下方のP型ウエル層3にP型ボディ層8の端部からN+型ドレイン層10に延在するN−型ドリフト層を形成する。この際、P型ボディ層8の端部から開口溝5の側壁下部までの領域AのN−型ドレイン層11の幅をできるだけ小さくなるよう制御する。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、かつ、コンタクト抵抗の増加およびオン電流の減少を防止できる半導体装置の提供。

【解決手段】ピラートランジスタTr1と、前記ピラートランジスタTr1の下部拡散層7aへ信号または電源を供給するとともに、ポリシリコン層10aからの固相拡散し、下部拡散層7aを形成することにより、前記ピラートランジスタTr1のチャネル長d1を厚みにより制御する前記ポリシリコン層10aと、を具備してなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール形成時の重ね合わせずれに起因したリークの増大やコンタクト抵抗の上昇が抑制された半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100と、半導体基板100上にゲート絶縁膜101を介して形成されたゲート電極102と、ゲート電極102の側壁上に形成されたサイドウォールスペーサ150と、半導体基板100のうち、ゲート電極102及びサイドウォールスペーサ150を間に挟んで両側に形成されたソースドレイン領域106と、ゲート電極102、サイドウォールスペーサ150、及び半導体基板100の上面を覆う応力絶縁膜110とを備えている。サイドウォールスペーサ150は、少なくとも中央部のゲート長方向膜厚よりも上部のゲート長方向膜厚の方が大きくなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧性の維持と低オン抵抗化との両立が可能なLDMOSトランジスタを提供する。

【解決手段】半導体装置は、第1導電型のドリフト拡散領域10と、第2導電型のボディ拡散領域2と、第1導電型のソース拡散領域6と、ドリフト拡散領域10の上部に形成されたトレンチ内に埋め込まれ、ボディ拡散領域2とは離間した位置に形成された絶縁膜14と、ドリフト拡散領域10の上部に形成され、絶縁膜14から見てソース拡散領域6と逆の方向に隣接する第1導電型のドレイン拡散領域7と、ボディ拡散領域2上からドリフト拡散領域10上を越えて絶縁膜14上にまで形成されたゲート電極5とを備えている。また、ドリフト拡散領域10は、基板内部領域11と、基板内部領域11よりも高濃度の第1導電型不純物を含む表面領域12とを有している。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

1 - 20 / 156

[ Back to top ]