Fターム[5F140AA06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | しきい値電圧の安定化 (713)

Fターム[5F140AA06]に分類される特許

1 - 20 / 713

半導体装置の製造方法

電界効果トランジスタ

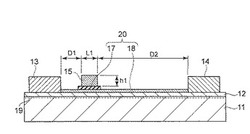

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法

【課題】しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの特性のばらつきを低減するために有利な技術を提供する。

【解決手段】MOSトランジスタを含む半導体装置の製造方法は、半導体基板の上に形成された第1絶縁膜の上にゲート電極材料層を形成する工程と、前記ゲート電極材料層の上にエッチングマスクを形成する工程と、前記ゲート電極材料層をパターニングすることによりゲート電極を形成する工程と、前記ゲート電極が形成された前記半導体基板の上に第2絶縁膜を形成する工程とを含み、前記ゲート電極を形成する工程では、前記ゲート電極材料層がパターニングされるとともに、少なくとも、前記ゲート電極の側面の下部と、前記第1絶縁膜のうち前記側面に隣接する部分とを保護する保護膜が形成され、前記第2絶縁膜を形成する工程では、前記保護膜を覆うように前記第2絶縁膜が形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

半導体装置及びその製造方法、電源装置、高周波増幅器

【課題】放置時間が長くても、化合物半導体積層構造の表面のダングリングボンドがフッ素で終端された状態が維持されるようにし、閾値電圧の変動を抑制して、信頼性を向上させる。

【解決手段】半導体装置は、化合物半導体積層構造6と、化合物半導体積層構造6の表面を覆うフッ素含有バリア膜9と、化合物半導体積層構造6の上方にフッ素含有バリア膜9を挟んで設けられたゲート電極8とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】 チャンネルドーピングあるいは複雑なゲート電極パターン化の必要性なしに、複数のトランジスタが多閾値電圧を有する半導体装置を提供する。

【解決手段】 半導体装置及びその製造方法において、第1トランジスタは、第1材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第2トランジスタは、第3材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第3トランジスタは、第1材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第4トランジスタは、第3材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第1材料乃至前記第4材料の仕事関数は互いに異なる。第1トランジスタ乃至第4トランジスタは、互いに異なる閾値電圧を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】バッファ層を有する半導体素子において、チャネルの基準電位を固定する半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板上に設けられ、エネルギーギャップの異なる複数種類の窒化物半導体が積層された積層体を少なくとも1層有するバッファ層20と、バッファ層上に設けられた窒化物半導体のチャネル層30と、バッファ層の側面に電気的に接続された側面電極60と、チャネル層の上方に形成され、チャネル層と電気的に接続されたチャネル電極52,56とを備える半導体素子。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

半導体装置

【課題】特性の優れた半導体装置を提供する。

【解決手段】本発明の一態様にかかる半導体装置は、半導体基板1に設けられた第1導電型のN−型オフセット層8と、トレンチ12を有し、N−型オフセット層8の間に設けられた第2の導電型のチャネル領域13と、チャネル領域13の上に形成され、トレンチ12に埋設されたトレンチゲート10を有するゲート電極4と、を備えたトランジスタを含み、ゲート幅方向におけるトレンチゲート10の幅がゲート長方向の位置に応じて変化しているものである。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域のゲート絶縁膜への酸化剤の進入を防止しつつ、第2の領域の複数の第1の配線間に設けられた酸化アルミニウム膜を選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

(もっと読む)

1 - 20 / 713

[ Back to top ]