Fターム[5F140AA25]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 高耐圧化 (661)

Fターム[5F140AA25]に分類される特許

1 - 20 / 661

パワートランジスタ装置のための多層構造を作製する方法、ヘテロ接合電界効果トランジスタ装置のための多層構造を作製する方法、および窒化物系ヘテロ接合電界効果トランジスタ装置

半導体装置

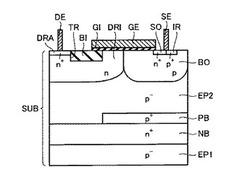

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

半導体装置とその製造方法

【課題】特性ばらつきの少ない絶縁ゲートを備えた窒化物半導体の半導体装置を提供すること。

【解決手段】 半導体装置が備える絶縁ゲートは、窒化物半導体層1上に設けられているアモルファスの酸化シリコン膜2と、酸化シリコン膜2上に設けられているゲート電極8を有している。ゲート電極8に対向する窒化物半導体層1が酸化されている。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

半導体装置

【課題】ノーマリオフで動作するとともに、高い耐圧と低いオン抵抗を具備した半導体装置を提供すること。

【解決手段】 半導体装置1では、ドレイン電極21が第1ヘテロ接合面32に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ソース電極29が第1ヘテロ接合面32に形成される2次元電子ガス層から電気的に絶縁可能に構成されているとともに第2ヘテロ接合面34に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ゲート部28が第2ヘテロ接合面34に対向しており、導通電極25が第1ヘテロ接合面32及び第2ヘテロ接合面34に形成される2次元電子ガス層の双方に対して電気的に接続可能に構成されている。第1ヘテロ接合面32に形成される2次元電子ガス層の電子濃度は、第2ヘテロ接合面34に形成される2次元電子ガス層の電子濃度よりも濃い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】結晶欠陥の発生を抑え、デバイスのリーク電流の発生、耐圧低下、しきい値電圧の継時変化、およびショートチャネル効果を抑制することが可能な半導体装置を提供すること。

【解決手段】単結晶AlNからなる基板を準備するステップと、前記単結晶AlNからなる基板の表面を酸素プラズマによって酸化し、単結晶AlNからなる基板上に酸化アルミニウムまたはアルミニウムオキシナイトライドからなる絶縁膜を形成するステップとを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

半導体装置およびその製造方法

【課題】スイッチング素子として利用される高耐圧かつ低オン抵抗な半導体装置を安価に提供する。

【解決手段】第1導電型の不純物を含有し、互いに対向する第1の主面と第2の主面とを有する半導体基板と、第2導電型の不純物を第1の濃度で含有し、前記半導体基板の前記第1の主面に露出するように形成された第1の拡散領域と、前記第2導電型の不純物を前記第1の濃度よりも高い第2の濃度で含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の側方に形成された第2の拡散領域と、前記第1導電型の不純物を含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の上方に形成された第3の拡散領域と、前記第2の拡散領域と絶縁膜を介して対向する制御電極と、を備え、前記第1の拡散領域と前記第2の拡散領域とは、前記制御電極に印加される電圧に応じて制御される電流の主経路を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

窒化物半導体装置

【課題】内蔵する環流ダイオードの順方向電圧が低く、高耐圧で、低オン抵抗の、ノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】窒化物半導体装置は、基板1、第1の窒化物半導体層3、第2の窒化物半導体層4、及び第2の窒化物半導体層上4に設けられた、ソース電極5、ドレイン電極6、第1のゲート電極9、ショットキー電極10、第2のゲート電極12、を備える。第2の窒化物半導体層4と第1の窒化物半導体層3との界面には、2次元電子ガスが形成される。第1のゲート電極9はノーマリオフ型FET20のゲート電極であり、ソース電極5とドレイン電極6との間に設けられる。ショットキー電極10は、第1のゲート電極9とドレイン電極6との間に設けられる。第2のゲート電極12はノーマリオン型FET21のゲート電極であり、ショットキー電極10とドレイン電極6との間に設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MOSFETの耐圧を向上させる。

【解決手段】MOSFETのドレイン領域を構成するLDD層6内に、LDD層6よりも不純物濃度層が低いN−−層11を形成して、チャネル領域側のドレイン領域端部の不純物濃度を低下させる。また、ソース領域側のLDD層7をLDD層6よりも浅い接合深さで、且つLDD層6よりも低い不純物濃度で形成する。これにより、オン状態およびオフ状態のいずれの状態においてもドレイン領域の電界を緩和し、インパクトイオンおよびパンチスルーの発生を防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

半導体装置

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

1 - 20 / 661

[ Back to top ]