Fターム[5F140AB00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149)

Fターム[5F140AB00]の下位に属するFターム

MOSIC、MISIC (2,326)

並列動作 (194)

三次元素子(SOIトランジスタとの組み合せ) (20)

ダイオード (159)

バイポーラトランジスタ (89)

J・FET (41)

C(容量) (167)

R(抵抗) (139)

Fターム[5F140AB00]に分類される特許

1 - 14 / 14

半導体装置及びその製造方法

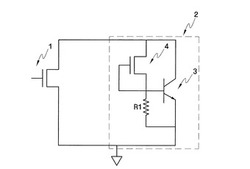

【課題】 出力ポートの絶縁破壊電圧より低い絶縁破壊電圧を有することが可能な静電放電保護素子を備える半導体装置を提供する。

【解決手段】 半導体装置は、第1LDMOS素子1を含む出力ポートと、出力ポートを静電放電から保護し、第2LDMOS素子4及びバイポーラトランジスタ3から構成される静電放電保護素子2と、を備える。第1LDMOS素子1および第2LDMOS素子4は、それぞれゲート、第1導電型のドレイン領域、第2導電型のボディ領域、及び第1導電型のドレイン領域と第2導電型のボディ領域との間に形成された素子分離領域を備える。このとき、第2LDMOS素子4の絶縁破壊電圧は、第1LDMOS素子1の絶縁破壊電圧より低い。これにより、第1LDMOS素子1の静電破壊を防止することができる。

(もっと読む)

可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置

【課題】可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置を提供する。

【解決手段】熱によるFETのソース及びドレイン間の電流減少の問題を効果的に解決し、またFETの温度を低めることができる可変ゲートFET及びこのFETを備える電気電子装置を提供し、可変ゲートFETは、FETと、FETの表面または発熱部分に取り付けられ、回路的には、FETのゲート端子に連結されておりゲート端子の電圧を変化させるゲート制御素子と、を備え、FETの温度が所定温度以上に上昇しているときに、ゲート制御素子が、ゲート端子の電圧を変化させて、FETのソース及びドレイン間のチャンネル電流を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】入力電圧ライン11と誘導性負荷Lとの間に接続される第1のスイッチング素子M1を有するハイサイドスイッチング素子と、誘導性負荷Lと基準電圧ラインとの間に並列接続される第2のスイッチング素子M2と第3のスイッチング素子M3とを有するローサイドスイッチング素子と、を備え、ローサイドスイッチング素子における誘導性負荷Lに接続される端子にサージが印加されたとき、サージ電流は第3のスイッチング素子M3を介して基準電圧ラインへと放電される。

(もっと読む)

半導体装置およびその製造方法

【目的】ジャンクションブロックを不要とし、またワイヤーハーネスの占有スペースを縮小化し、過電流となった主電流を確実に遮断できて、電気経路を確実に開放できるヒューズ素子を半導体基板内に形成した半導体装置およびその製造方法を提供する。

【解決手段】p半導体基板1に形成したトレンチ18の内壁にシリコン酸化膜21を介してヒューズ素子22を形成し、トレンチ18の開口部を塞ぐようにポリイミド膜23を被覆することで、溶断したヒューズ素子22が再度固化したときに、固化したヒューズ材で第1表面端子aと第2表面端子bの間を短絡しないようにする。半導体装置内にヒューズ素子22を有することで、ジャンクションブロックを不要とし、またワイヤーハーネスの占有スペースを縮小化できる。

(もっと読む)

トンネル電界効果トランジスタを用いたメモリ

【課題】抵抗メモリの一種として挙げられ、抵抗記憶素子に相変化材料を用いた相変化メモリを提供する。

【解決手段】メモリは、第1ドレイン124と第1ソース122aとを含む第1トンネル電界効果トランジスタ108aを含んでいる。上記第1ドレインは、第1抵抗記憶素子106aに結合されている。上記メモリは、第2トンネル電界効果トランジスタ108bを含んでいる。上記第2トンネル電界効果トランジスタは、第2ドレインを含み、上記第1ソース122aを共有している。上記第2ドレインは、第2抵抗記憶素子に結合されている。上記メモリは、ソースノードを設けるために、上記第1ソースに結合されている第1領域114を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】TLPMと保護素子を集積すること。TLPMとともに保護素子を作製すること。

【解決手段】複数のトレンチ5により、p型半導体基板1上のn型ウェル領域2aの表面層を、第1メサ領域33、第2メサ領域34および第3メサ領域35に分割する。第1メサ領域33、第2メサ領域34および第3メサ領域35に、それぞれn型ソース領域7、n型ドレイン領域6およびp型コレクタ領域4bを設ける。n型ウェル領域2a内で、トレンチ5の底面にn型拡張ドレイン領域3a,3bを設ける。n型ソース領域7とn型拡張ドレイン領域3bの間にp型チャネル領域4aを設ける。このような構造により、コレクタ電極9bとソース電極10の間に、p型コレクタ領域4bと、n型ウェル領域2aおよびn型拡張ドレイン領域3bと、p型チャネル領域4aと、n型ソース領域7からなるPNPNサイリスタ構造の保護素子を設ける。

(もっと読む)

半導体素子、半導体素子の製造方法

【課題】製造プロセスにおけるゲート電極への帯電に起因するチャージアップを防ぐことが可能な半導体素子を提供する。

【解決手段】半導体基板内に形成されたn型の不純物からなるソース領域4と、半導体基板内に形成されたn型の不純物からなるドレイン領域5と、ソース領域4及びドレイン領域5間の半導体基板上にゲート絶縁膜3を介して形成されたゲート電極6とを含むMOSトランジスタを有する半導体素子であって、半導体基板内に形成されたn型の不純物領域7と、半導体基板内に形成されたp型の不純物領域10と、n型の不純物領域7及びp型の不純物領域11の各々とゲート電極6とを接続するために設けられた配線H1及びH2とを備える。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

半導体装置

【課題】半導体装置の微細化の進展に拘わらず、ESD耐量を高く保つことができる半導体装置を提供する。

【解決手段】n型ドレイン層15に隣接し且つドレイン電極20によりドレイン層15と電気的に短絡されるように形成され静電放電時にESD保護素子の一部として機能するp型の半導体層17が形成される。p型半導体層17とドレイン層15とは、動作電流の方向とは交差する方向に並ぶように配列される。

(もっと読む)

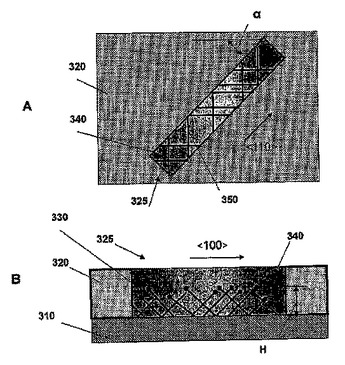

転位欠陥密度の低い格子不整合半導体構造およびこれに関連するデバイス製造方法

貫通転位が実質的にない上部分を有する制限されたエリア領域を備えている、モノリシック格子不整合半導体ヘテロ構造の製造、ならびにこのような格子不整合ヘテロ構造をベースとした半導体デバイスの製造。  (もっと読む)

(もっと読む)

二重拡散型MOSFETおよびこれを用いた半導体装置

【課題】L−DMOSFET本来の特性を損なうことなく、また素子面積の増大を招くことなく、高い静電破壊耐量を得ることができるL−DMOSFETを提供する。

【解決手段】半導体基板11上に形成されたN型半導体層からなるドレイン領域13と、ドレイン領域13内に形成されたP型半導体領域からなるボディ領域15と、ボディ領域15内に形成されたN型ソース領域16と、ボディ領域15表面に形成されたゲート電極21とを含み、前記ドレイン領域13内に、ドレイン領域表面に形成されたN+型ドレインコンタクト領域18を形成すると共に、前記N+型ドレインコンタクト領域18に囲まれた領域に形成され、前記N+型ドレインコンタクト領域18と同電位となるように電気的に接続されたP型領域19を具備してなることを特徴とする。

(もっと読む)

半導体装置

【課題】 IGBTの動作と逆導通機能の両方の特性を同時に改善できる半導体装置を提供する。

【解決手段】 この半導体装置1Aは、N−エピ層5の表面層に各P拡散領域9,11から離間されて形成されたP拡散領域23と、P拡散領域23の表面層にP拡散領域23に取り囲まれて形成されたN+拡散領域25と、N+拡散領域25に設けられると共に第1コレクタ電極19aと接続された第2コレクタ電極19bと、P拡散領域23およびN−エピ層5に跨設されて、N−エピ層5からP拡散領域23への通電経路を構成する電極27とを備える。

(もっと読む)

半導体装置

【課題】オン抵抗の低減とESD耐量などのサージ耐量の向上を図ることができる半導体装置を提供する。

【解決手段】p型半導体基板1の表面層にストライプ状のnウェル領域2を形成し、このnウェル領域2の表面層にストライプ状のpウェル領域3を形成し、このpウェル領域3の表面層にストライプ状のnソース領域4とストライプ状のpコンタクト領域5を形成し、このnソース領域4上とpコンタクト領域5上にストライプ状のソース電極11を形成し、nウェル領域2の表面層にpウェル領域3と離してストライプ状のnドレイン領域8を形成し、このnドレイン領域8に囲まれるように四角形のpアノード領域15を複数個形成し、nドレイン領域8上とpアノード領域15上にドレイン電極10を形成する。pウェル領域3(nソース領域4)と対向する四角形のpアノード領域15の辺とはドレイン電極10は接しないようにする。

(もっと読む)

1 - 14 / 14

[ Back to top ]