Fターム[5F140AC00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642)

Fターム[5F140AC00]の下位に属するFターム

Pchトランジスタ (555)

空乏層制御型(ディプレッション型) (42)

SIT (3)

電磁波(光) (5)

常温以外での動作 (6)

電圧印加 (40)

量子効果素子 (56)

その他の特殊動作(パンチスルーTr、磁気) (47)

デュアルゲートMOS、四極MOS (8)

BOMOS(埋込み酸化膜MOS) (24)

単一電子素子 (10)

横型DMOS、DSA(二重拡散Tr) (541)

横型IGBT (117)

縦型トランジスタ(縦型DMOSなど) (291)

表面に連続した凹凸を形成するもの (27)

歪みを利用したもの (848)

素子配置 (40)

用途 (713)

薄膜トランジスタ、TFT、SOI、SOS (1,150)

イオン感応電界効果Tr、イオンセンサ (24)

CCD (7)

MOSダイオード、MOSキャパシタ (58)

MOSサイリスタ (7)

Fターム[5F140AC00]に分類される特許

1 - 20 / 23

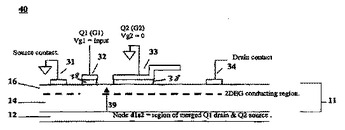

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】 ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタの下面または上面にボディ電極8を設ける。下面にボディ電極8を設ける場合、p型Si基板2上にAlN層31およびGaN層32の繰り返しによるバッファ層3を介してp−GaN層4を設け、バッファ層3の最上層のAlN層31を薄くし、p型Si基板の下面にボディ電極8を形成する。上面にボディ電極8を設ける場合、サファイア基板21上にp−GaN層4を設け、ソース電極5およびドレイン電極6下の部分にAlGaN層13を設け、AlGaN層13上にボディ電極8を設ける。アバランシェにより生じる正孔20をボディ電極8より引き抜く。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上10−1に、チャネル長方向が<−110>方向に沿って配置される絶縁ゲート型電界効果トランジスタpMOSと、前記半導体基板における素子分離領域の溝内に埋め込まれ、正の膨張係数を有し、前記絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加える第1素子分離絶縁膜11−1とを具備する。

(もっと読む)

可動ゲート型電界効果トランジスタの製造方法

【課題】ダメージを生じさせることなく、安価かつ短時間に犠牲層を除去する犠牲層プロセスを採用し、量産性を向上させる可動ゲート型電界効果トランジスタの製造方法を提供する。

【解決手段】第1犠牲層15と、第2犠牲層16と、を有する複合犠牲層の上に可動ゲートが形成される可動ゲート形成工程と、第2犠牲層16がエッチング除去される第2犠牲層除去工程と、第1犠牲層15がエッチング除去される第1犠牲層除去工程と、を備える可動ゲート型電界効果トランジスタの製造方法とした。

(もっと読む)

半導体装置及びその製造方法

【課題】MIS−HEMTにおいて、閾値電圧の低下を抑制する。

【解決手段】半導体装置は、基板19と、この基板上に形成されており、電子走行層13及び電子供給層15が順次積層されて形成された積層構造体17とを含む下地11を具えている。この下地の下地面には、互いに離間し、かつ対向して第1及び第2主電極が形成されている。そして、下地面11aの、これら第1主電極41a及び第2主電極41b間に挟まれた領域内に、ゲート形成用凹部27が形成されている。更に、半導体装置はゲート絶縁膜29を具えている。そして、このゲート絶縁膜は、最小でも2.9g/cm3の結晶密度で形成されている。また、半導体装置は、ゲート絶縁膜が形成された前記ゲート形成用凹部を埋め込むゲート電極43を具えている。

(もっと読む)

半導体装置

【課題】 高融点金属を含む多層配線を使用してトランジスタに導入される配線がトランジスタのチャネル幅方向と垂直の方向から導入される場合においても、ESD保護用のN型MOSトランジスタの全体で均一に動作させることのできる半導体装置を得る。

【解決手段】 複数のドレイン領域と複数のソース領域が交互に配置され、前記ドレイン領域と前記ソース領域の間にゲート電極が配置された、複数のトランジスタが一体化した構造を有するESD保護用のN型MOSトランジスタにおいて、ドレイン領域に接続される第1のメタル配線とソース領域に接続される第1のメタル配線の片方あるいは両方が、第1のメタル配線以外の複数層のメタル配線と接続されており、第1のメタル配線と第1のメタル配線以外の複数層のメタル配線とを電気的に接続するためのビアホールの数を、ESD保護用のN型MOSトランジスタへ外部から配線される配線の距離に応じて、遠くなるほど数多く形成した。

(もっと読む)

半導体装置

【課題】 工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を得る。

【解決手段】 素子分離にシャロートレンチ構造を有するESD保護用のN型MOSトランジスタにおいて、ESD保護用のN型MOSトランジスタのドレイン領域は少なくとも前記ESD保護用のN型MOSトランジスタのゲート電極に近接する領域において、シャロートレンチ分離領域から離れて配置した。

(もっと読む)

高周波電力増幅器および携帯型無線端末

【課題】動作時の出力低下が少なく、熱雑音の影響が少なく、高周波動作が安定で、かつ信頼性に優れた高周波電力増幅器および携帯型無線端末を提供することを可能にする。

【解決手段】半導体基板上に並列に配置され、それぞれがソース電極、ゲート電極、およびドレイン電極を有する複数のMOSトランジスタと、前記複数のMOSトランジスタのうち隣接するMOSトランジスタ間に設けられた短絡した導体からなる閉ループと、を備え、前記複数のMOSトランジスタのソース電極、ゲート電極、およびドレイン電極はそれぞれ並列に接続されている。

(もっと読む)

半導体装置

【課題】厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供する。

【解決手段】ドレイン領域はN−ドレイン領域3dとN+ドレイン領域11dからなる二重拡散構造を備えている。ゲート電極は、ゲート絶縁膜7上に形成された第1ゲート電極9と、第1ゲート電極上9にゲート電極間絶縁膜11を介して形成された第2ゲート電極13とからなる。第2ゲート電極13にゲート配線13gが接続され、第1ゲート電極9にはゲート配線13gは接続されていない。ゲート絶縁膜7とN+ソース領域11sの間の半導体基板1表面にフィールド絶縁膜15配置されている。第1ゲート電極9のドレイン領域側の端部はフィールド絶縁膜15上に配置されている。第2ゲート電極13に印加されるゲート電圧はゲート絶縁膜7とゲート電極間絶縁膜11で分割される。

(もっと読む)

半導体装置

【課題】厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供する。

【解決手段】ドレイン領域はN−ドレイン領域3dとN+ドレイン領域11dからなる二重拡散構造を備えている。ゲート電極は、ゲート絶縁膜7上に形成された第1ゲート電極9と、第1ゲート電極上9にゲート電極間絶縁膜11を介して形成された第2ゲート電極13とからなる。第2ゲート電極13にゲート配線13gが接続され、第1ゲート電極9にはゲート配線13gは接続されていない。ゲート絶縁膜7とN+ソース領域11sの間の半導体基板1表面にフィールド絶縁膜15配置されている。第1ゲート電極9のドレイン領域側の端部はフィールド絶縁膜15上に配置されている。第2ゲート電極13に印加されるゲート電圧はゲート絶縁膜7とゲート電極間絶縁膜11で分割される。

(もっと読む)

半導体素子の製造方法、半導体素子、及び遅延装置

【課題】トランジスタのゲート領域にWSi2が積層されたノンドープのポリシリコンを用い、WSi2をゲート電極とし、ノンドープのポリシリコンを高抵抗体として扱い、実効的なゲート絶縁部の膜厚を制御しローパスフィルターを形成する技術がある。この技術をサリサイド工程に展開する場合に、例えばLDD形成に伴い寄生的に当該ポリシリコンの一部に不純物が添加されると、サリサイド化に伴う高速の拡散により広がり、当該ポリシリコンの比抵抗が低下しフィルター特性が劣化するという課題がある。

【解決手段】トランジスタのゲート領域形成前にLDD部を形成する。LDD部を先に形成することで、ゲート領域とLDD部とのオーバーラップがある状態で、かつゲート領域への不純物導入を防止することが可能となる。LDD部の形成に伴う不純物がゲート領域に侵入しないため、高速の拡散が生じてもゲート領域内への不純物拡散が防止できる。

(もっと読む)

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

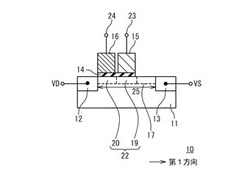

併合ゲートカスコードトランジスタ

この発明の実施例に従う併合ゲートトランジスタは、半導体要素と、半導体要素の上面に電気的に接続された供給電極と、半導体要素の上面に電気的に接続され、かつ、供給電極から横方向に間隔をあけたドレイン電極と、供給電極およびドレイン電極の間に位置決めされ、かつ、半導体要素に容量結合されて、トランジスタの第1の部分を形成する第1のゲートと、第1のゲートに隣接して供給電極およびドレイン電極の間に位置決めされて、トランジスタの第2の部分を形成する第2のゲートとを含み、第2のゲートも半導体要素に容量結合される。第1のゲートは、第1の部分の導通が入力電圧信号の値に基づくように入力電圧信号に接続され、第2のゲートは、所定の定電圧とソース電極における電圧との間の電圧差が所定のレベルに達するまでトランジスタの第2の部分が導通するように所定の定電圧に接続される。  (もっと読む)

(もっと読む)

スピンFET及びスピンメモリ

【課題】スピンFET/スピンメモリの低消費電力と高信頼性を実現する。

【解決手段】本発明の例に関わるスピンFETは、磁化方向が固定される磁気固着層12と、磁化方向が変化する磁気フリー層13と、磁気固着層12と磁気フリー層13との間のチャネルと、チャネル上にゲート絶縁層18を介して配置されるゲート電極19と、磁気フリー層13上に配置され、電場により磁化方向が変化する磁性層15とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧且つ低オン抵抗なノーマリーオフ型の半導体装置及びその製造方法を提供すること。

【解決手段】p型半導体領域と、n型半導体領域と、これらp型半導体領域とn型半導体領域との間に介在して設けられp型及びn型半導体よりも高抵抗な高抵抗領域と、を有する第1の層と、第1の窒化物半導体からなり第1の層の上に積層された第2の層と、第1の窒化物半導体よりもバンドギャップが大なる第2の窒化物半導体からなり第2の層の上に積層された第3の層と、第3の層の上に設けられたソース電極と、ドレイン電極と、p型半導体領域に対向して第3の層の上に設けられたゲート電極と、を備え、p型半導体領域はソース電極とゲート電極のいずれか一方と接続され、第1の層において、ゲート電極とドレイン電極間に対応する部分に高抵抗領域が設けられている。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】 窒化物半導体電界効果トランジスタに関し、ゲートリーク電流を低減するとともに、優れた高出力特性を実現する。

【解決手段】 窒化物半導体電界効果型トランジスタのゲート絶縁膜2をハロゲン化物で構成する。

(もっと読む)

MOSトランジスタ

【課題】 メタル配線の抵抗成分をさらに低減し、システム電源デバイスの高出力・高効率化を実現できるとともにさらなる素子面積の縮小を図ることができるMOSトランジスタを提供する。

【解決手段】 ソース領域とドレイン領域とが格子状に形成されたゲートを挟んで互いに隣接するように形成されたMOSトランジスタにおいて、MOSトランジスタを半導体チップ上の角部に配置し、半導体チップ上の1つの角部の第1のチップエッジに隣接する領域に、ソース領域に接続されたソース側メタル配線が接続される第1のソースボンディングパッドとドレイン領域に接続されたドレイン側メタル配線が接続される第1のドレインボンディングパッドとを設け、角部の第2のチップエッジに隣接する領域に、ソース側メタル配線が接続される第2のソースボンディングパッドとドレイン側メタル配線が接続される第2のドレインボンディングパッドとを設ける。

(もっと読む)

双方向型電界効果トランジスタおよびマトリクスコンバータ

【課題】単一のデバイスで双方向に流れる電流を制御できる双方向型電界効果トランジスタおよびこれを用いたマトリクスコンバータを提供する。

【解決手段】双方向型電界効果トランジスタは、半導体基板1と、半導体基板1上に設けられ、該基板1の主面に平行なチャネルと該チャネルのコンダクタンスを制御するためのゲート電極13aとを含むゲート領域と、チャネルの第1端側に設けられた第1領域と、チャネルの第2端側に設けられた第2領域とを備え、第1領域の第1電極11aからチャネルを介して第2領域の第2電極12aへ流れる順方向電流および第2電極12aからチャネルを介して第1電極11aへ流れる逆方向電流が、ゲート電極13aに印加されるゲート電圧によって制御される。

(もっと読む)

半導体装置およびその製造方法

【課題】高周波電力増幅用電界効果型半導体装置において、耐圧を確保しながらの小型化と高効率化の両立が困難になる。

【解決手段】高周波電力増幅用出力段LDMOSに、歪Siチャネルを用いることで更なる効率向上を実現する。更に、チャネル領域を有する歪Si層の膜厚、欠陥の不活性化、或いはフィールドプレート構造の最適化などによってリーク電流を低減しつつ最大限に効率を高める。

(もっと読む)

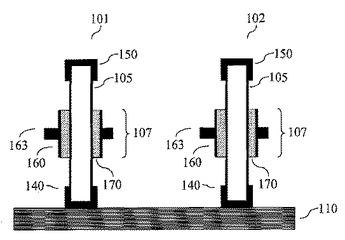

共振トランジスタ及び通信装置

【課題】 本発明は、微小共振器を用いて、高周波化で、高SN比化、高いパワー化を可能にした共振トランジスタ、より具体的にはビーム型共振バルクトランジスタ及びビーム型共振薄膜トランジスタを提供するものである。

【解決手段】 本発明の共振トランジスタ1は、ドレイン領域4とソース領域2とチャネル領域3を有すると共に、前記チャネル領域3上に空間16を介して対向するゲート振動子5を有し、前記ゲート振動子5の共振によって前記ドレイン領域4に流れるドレイン電流が交流変化することを特徴とする。

(もっと読む)

1 - 20 / 23

[ Back to top ]