Fターム[5F140AC01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | Pchトランジスタ (555)

Fターム[5F140AC01]に分類される特許

1 - 20 / 555

半導体装置の製造方法

半導体装置およびその製造方法

半導体装置及びその製造方法

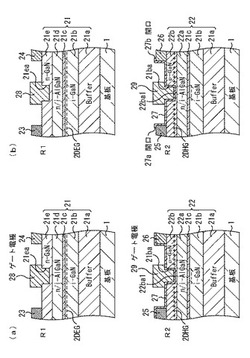

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置の製造方法

【課題】高いオン電流を得つつ、オフリーク電流を抑制することができる半導体装置を簡単に製造することができる方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上にゲート電極を形成する。ドレイン層形成領域に第1導電型の不純物を導入する。次に、熱処理を行うことによってドレイン層形成領域の第1導電型の不純物を活性化する。次に、ソース層形成領域に不活性不純物を導入することによって該ソース層形成領域の半導体基板の単結晶をアモルファス化する。次に、ソース層形成領域に第2導電型の不純物を導入する。次に、半導体基板にマイクロ波を照射することによって少なくともソース層形成領域のアモルファス半導体を単結晶化し、かつ、ソース層形成領域の第2導電型の不純物を活性化する。ソース層形成領域における第2導電型の不純物の深さは、ドレイン層形成領域における第1導電型の不純物の深さよりも浅い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】特性の低下を抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、が含まれている。p型半導体層8に含まれるp型不純物として、少なくとも電子走行層3及び電子供給層5のいずれかを構成する元素と同種の元素が用いられている。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】レジストパターンの下地層への悪影響を及ぼすことなくスカムを最適に除去する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上に酸化膜5cを形成し、前記酸化膜5c上にフォトレジスト8を塗布し、前記フォトレジスト8を露光し、露光された前記フォトレジスト8を現像することにより前記フォトレジス8トに開口部8aを形成し、前記フォトレジスト8をマスクとして、前記酸化膜5cを酸素プラズマ処理し、前記酸素プラズマ処理の後、前記酸化膜5cと前記フォトレジスト8に希釈フッ酸を供給し、前記希釈フッ酸を供給する工程の後、前記フォトレジスト8をマスクとして前記酸化膜5cを通して記半導体基板1に一導電型不純物をイオン注入する工程を含む。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

半導体装置

【課題】トンネル型FETのオン電流とオフ電流との比と、単位基板面積あたりのオン電流を増大させる。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側面に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記半導体基板上に順に積層された第1導電型の下部主端子層と、中間層と、第2導電型の上部主端子層とを有し、前記ゲート絶縁膜を介して前記ゲート電極の側面に形成された積層体とを備える。さらに、前記上部主端子層は、前記ゲート電極の側面に、前記ゲート絶縁膜と半導体層を介して形成されている。

(もっと読む)

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置及びその駆動方法

【課題】閾値電圧(Vth)の経時的に変動する現象を抑制することで、高信頼性を保つことが可能なMIS型半導体装置を提供する。

【解決手段】本発明は、半導体ボディ領域とゲート絶縁膜の間に半導体ボディ領域とは逆の半導体極性のチャネル層を有するMIS型半導体装置であり、当該半導体装置のフラットバンド電圧Vfbを−10ボルト以下とすることにより、半導体ボディ領域表面近傍に誘起されるキャリア電荷密度を当該半導体装置の動作保証範囲内において所定量以下に抑制する。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】シンカー層を含むエピタキシャル層の厚さを増大させても耐圧性能の向上が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、第1導電型の埋め込み拡散層16Na,16Nd,16Nbを有する支持基板10と、第1導電型と同じ導電型のシンカー層21Na,21Nbを有するエピタキシャル層20と、シンカー層21Na,21Nbから離れた領域でエピタキシャル層20上に形成された電極層31とを備える。支持基板10の上層部は、エピタキシャル層の上面に向けて突出する凸状部10Pa,10Pbを有し、シンカー層21Na,21Nbは、エピタキシャル層20の上面近傍から凸状部10Pa,10Pbにおける埋め込み拡散層16Na,16Nbにまで延在する不純物拡散領域からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の表面に導入された不純物を、前記表面の浅い領域に高精度かつ高濃度で分布させ、不純物が半導体基板の深い領域に拡散することを防ぐことで、半導体装置の歩留まりおよび性能を向上させ、装置の微細化を容易にする。

【解決手段】N型MISトランジスタにおいて、半導体基板300に打ち込まれた炭素が、同じ領域に打ち込まれたホウ素を引き寄せる性質を利用し、ホウ素をN型の不純物として注入したハロー領域306に炭素を共注入して炭素注入層307を形成する。これにより、ホウ素が増速拡散することを防ぎ、ハロー領域306を高い精度で形成することを可能とすることで、微細化された半導体素子の短チャネル効果の発生を抑制する。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】被処理体の所定領域に注入された、N型領域を形成する元素のイオンを、アニール処理の前後において被処理体の内部に維持し、所望のキャリア濃度のN型領域を形成することを可能とする、半導体デバイスの製造方法を提供する。

【解決手段】減圧雰囲気とした真空チャンバ内に、シリコンからなる被処理体101を配して、該真空チャンバ内に導入した、N型領域106Nを形成する元素Xを含むガスをプラズマ励起し、励起された該元素Xのイオンを、被処理体101の所定領域に注入する前工程と、該元素Xが注入された被処理体101をアニール処理する後工程と、を含み、該前工程と該後工程との間に、該真空チャンバ内に導入した酸素元素を含むガスをプラズマ励起し、励起された該酸素元素のラジカルに、該被処理体101の所定領域を曝露する工程を、さらに備えてなることを特徴とする半導体デバイスの製造方法。

(もっと読む)

1 - 20 / 555

[ Back to top ]