Fターム[5F140AC31]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 用途 (713)

Fターム[5F140AC31]の下位に属するFターム

Fターム[5F140AC31]に分類される特許

1 - 20 / 49

撮像装置の製造方法

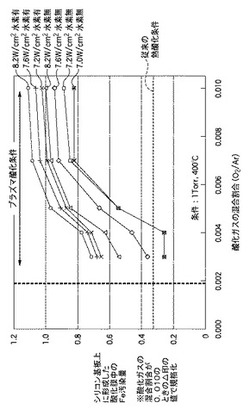

【課題】プラズマ酸化によりシリコン基板上に形成される酸化膜の金属汚染量を低減すること。

【解決手段】酸化膜の形成方法は、不活性ガスと、前記不活性ガスに対する混合割合が0よりも大きく且つ0.007以下である酸化ガスと、を含む混合ガスからプラズマを生成する工程と、前記プラズマを用いてシリコン基板の表面に酸化膜を形成する工程と、を含む。

(もっと読む)

電子装置

【課題】 信頼性及び色再現性の高い電子装置を提供する。

【解決手段】 単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

半導体装置

【課題】放熱効率が高く低コストでの実装が可能な半導体装置を提供する。

【解決手段】第1の方向に延在するゲート電極を有する複数のトランジスタを有し、複数のトランジスタが第1の方向と交差する第2の方向に配置されたトランジスタアレイ54と、トランジスタアレイの第1の方向に配置され、複数のトランジスタのソース領域に電気的に接続されたパッド電極50とを有する。

(もっと読む)

炭化ケイ素半導体デバイス

【課題】航空機の配電システムでの使用に際しても、十分に信頼できる炭化シリコンを使用したMOSFETを提供する。

【解決手段】炭化シリコンMOSFETのゲート絶縁膜16を、シリコンからなる第1の層と炭化シリコンからなる第2の層15に貼着することによって、第1の層と第2の層との間に境界面を形成した後、シリコンからなる第1の層の一部又は全部を酸化することにより境界面に炭素クラスターの存在しないゲート絶縁膜16を形成する。

(もっと読む)

半導体装置

【課題】同期整流方式のDCDC変換装置において、短絡防止期間中に、同期整流用FETのドレインが負電圧となると、基板−ドレインの間に電流が流れ、基板の電位が揺すられる。同期整流用FETを内蔵した素子の場合、この基板の電位の揺れは制御回路の誤動作を招く。

【解決手段】P型基板とバックゲートとが分離されたNチャネルMOSFETを2段縦積みにした構造を有する複合素子を、同期整流用FETとして用い、複合素子の上段側FETを、メイン側FETがオフかつ下段側FETがオフとなる短絡防止期間において、オフとする。

(もっと読む)

プラズマ処理方法

【課題】3次元トランジスタ構造のPolyシリコンゲート側壁の窒素含有シリコン膜をシリコン基板削れを抑制しつつ、所望の形状に加工する方法を提供する。

【解決手段】3次元トランジスタ構造上の窒素含有シリコン膜をプラズマエッチングするために、堆積性の高いガスでエッチングする第1ステップと、堆積成分を除去する第2ステップとを有し、前記第1ステップと前記第2ステップを交互に繰り返すことにより、Polyシリコンゲート電極31の側壁にのみ窒素含有シリコン膜34を残し、かつ、シリコン基板33の削れを抑制するようにエッチング加工する。

(もっと読む)

可動ゲート型電界効果トランジスタ

【課題】可動ゲート電極の変位を制御可能な可動ゲート型電界効果トランジスタを提供する。

【解決手段】ソース電極17とドレイン電極18との上に導電シールド電極20が配置される可動ゲート型電界効果トランジスタ1とした。そして導電シールド電極20の電位を固定することとした。導電シールド電極20が配置されることにより、可動ゲート15とドレイン電極18またはソース電極17との間に発生する静電力を抑制することができる。

(もっと読む)

保護トランジスタおよび半導体集積回路

【課題】占有面積が小さく、所望の耐圧と熱破壊の防止を両立した保護トランジスタを提供する。

【解決手段】ゲート長方向の一方の側でゲート直下の領域に隣接しているゲート・ドレイン間領域REgdが、ゲート幅方向に互いに隣接する領域として、第1領域REgd1と第2領域REgd2とを有する。第1領域は、ドレイン耐圧が相対的に大きく、第2領域は、ドレイン電極(ドレインコンタクト部に設けられているシリサイド層10D)からの距離が平面視で第1領域より遠く、ドレイン耐圧が相対的に小さい。このため、耐圧が低いゲート・ドレイン間領域REgd2の加熱部分Aからドレインコンタクト部が遠いが、面積は小さく(または拡大しない)構造となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の拡散によるナローチャネル効果の発生を抑制することを可能にする半導体装置を提供する。

【解決手段】半導体基体1と、半導体基体1に少なくとも一部が埋め込まれた、素子分離のための絶縁層2と、半導体基体1内に形成された不純物領域を含んで成る能動素子と、絶縁層2と半導体基体1との間に形成された、負の固定電荷を有する膜11とを含んで半導体装置を構成する。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】RTSノイズを低減することが可能な絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】チャネル領域として機能するp型の半導体層11と、チャネル領域を少なくとも囲み、活性領域21Bを定義する素子分離絶縁膜21と、活性領域21Bの一方に設けられたn型の第1主電極領域12と、活性領域21Bの他方に設けられたn型の第2主電極領域13と、活性領域21B上に設けられたゲート絶縁膜22と、ゲート絶縁膜22上において、第1主電極領域12と第2主電極領域13との間のチャネル領域を流れるキャリアの流路に直交する方向に伸延するゲート電極24とを備え、チャネル領域への前記キャリアの注入口が素子分離絶縁膜21から離間して設けられている。

(もっと読む)

電磁気素子の製造方法

【課題】レジスト残渣に起因するリーク電流の増大を生じさせることがなく、微細パターンの形成が可能であり、電極のエッジ部分の絶縁膜が薄くなることに起因するリーク電流の増大を抑制することが可能な電磁気素子の製造方法を提供すること。

【解決手段】基板上に、12(CaxSr1-x)O・7Al2O3(0≦x≦1)を含む絶縁膜を形成する絶縁膜形成工程と、絶縁膜の上にアンモニウム塩アルカリ溶液を含む現像液で現像可能な第1フォトレジストを塗布し、第1フォトマスクパターンに応じて第1フォトレジストを露光する第1フォトレジストパターン形成工程と、第1フォトレジストをアンモニウム塩アルカリ溶液を含む現像液に接触させ、第1フォトレジストの可溶部分の溶解と同時に、絶縁膜をエッチングする現像・エッチング工程とを備えた電磁気素子の製造方法。

(もっと読む)

歪み検出素子

【課題】ゲート電極、ソース電極、およびドレイン電極を備えたトランジスタ型の歪み検出素子であって、金属製歪みゲージよりも格段に優れた検出感度を有する歪み検出素子の提供。

【解決手段】ゲート電極と、ソース電極と、ドレイン電極と、チャネルが形成される圧電材料からなる層と、を備えた歪み検出素子であって、(a)上記ゲート電極の長さが2μmより大きいこと、(b)上記ゲート電極の幅が1mmより小さいこと、(c)上記ゲート電極と上記ソース電極の距離と、上記ゲート電極と上記ドレイン電極の距離との和が13μmより大きいこと、の3条件のうち少なくともいずれか1つの条件が成立していることを特徴とする。

(もっと読む)

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

半導体装置

【課題】製造工程を変更することなくMOSトランジスタのドレイン電流−温度特性を制御する。

【解決手段】半導体層1に互いに間隔をもって形成されたソース11s及びドレイン11d,13dと、ソース11sとドレイン11d,13dの間の半導体層1上にゲート絶縁膜5を介して形成されたゲート電極7とをもつMOSトランジスタを備えている。MOSトランジスタで、ソース11sは上方から見てゲート電極7とは間隔をもつ位置に形成されている。ドレイン13dは上方から見てゲート電極7に一部重複する位置に形成されている。上方から見たソース11sとゲート電極7の間の距離AはMOSトランジスタが温度上昇に対してドレイン電流が増加するドレイン電流−温度特性をもつ寸法に設定されている。

(もっと読む)

出力制御用半導体装置

【課題】 チップサイズを縮小することができ、低コスト化が可能となるスイッチングトランジスタ、及びそれを用いた出力制御装置を提供する。

【解決手段】 第一導電型の半導体基板1の主面上に、第二導電型の高濃度埋め込み層2を有し、エピタキシャル層3の表面に形成される第二導電型のドレイン領域9と第二導電型の高濃度埋め込み層2が第二導電型の柱状の高濃度拡散領域11を介して電気的に接続していることにより、ドレイン端子10が基板表面上にある縦型トランジスタを用いる。

(もっと読む)

MOSトランジスタ、CMOS及びこれを用いたモータ駆動用半導体集積回路装置

【課題】本発明は、製造工程の大きな変更もなく、1枚のマスクの変更のみで駆動時の出力波形の立ち上がりの時間的変化率を緩やかにできるMOSトランジスタを提供することを目的とする。

【解決手段】半導体基板上80に所定のゲート幅Wを有して延在する複数のゲート10が略平行に配置され、該ゲートの両側にソース20とドレイン30が交互に配置された複数のトランジスタセルを含むMOSトランジスタ100、100aであって、

前記ゲート10の両端部11、12と平面視的に重なり、前記ゲート10の両端部11、12から同電位の供給が可能に配置されたゲート配線層70を有し、

該ゲート配線層70と前記ゲート10の端部とを電気的に接続するゲートコンタクト40が、前記ゲート10の端部11、12の片側のみに設けられたトランジスタセルを含むことを特徴とする。

(もっと読む)

耐高圧定電流源デバイス及びその製造方法

【課題】直接に交流電源及び直流電源に実用でき、過電流・過電圧保護機能を有する耐高圧定電流源デバイス及びその製造方法を提供する。

【解決手段】このデバイスは、P型シリコン基層1、酸化層6、ドレーン金属2、ソース金属3、ゲート金属4、P+基層接触リージョン、N+ドレーンリージョン52、N+ソースリージョン53、N+ドレーンリージョン52とN+ソースリージョン53を接続するN−チャンネルリージョン54、N+ドレーンリージョン52を囲んでいるN−ドレーンリージョン92で構成され、ドレーン金属2はN+ドレーンリージョン52と接続し、ソース金属3はN+ソースリージョン53、P+基層接触リージョンと互いに接続し、ソース金属3とゲート金属4は接続金属によって接続されている。

(もっと読む)

MOSトランジスタ、固体撮像装置、電子機器、及びそれらの製造方法

【課題】チャネル領域の特性向上及び、1/fノイズの改善を図ったMOSトランジスタを提供する。また、そのMOSトランジスタを用いた固体撮像装置を提供する。

【解決手段】ゲート電極31と、ゲート電極31に対して、チャネル領域34が素子分離領域32により複数に分割されたソース・ドレイン領域33から構成されるMOSトランジスタとする。

(もっと読む)

LCD駆動チップとその製造方法

【課題】小さいながら高い電流性能をもつ、LCD駆動チップとその製造方法を提供する。

【解決手段】基板に形成された第1導電型ウェルと、前記第1導電型ウェルに形成された第2導電型ドリフト領域と、前記第2導電型ドリフト領域内に形成された第1素子分離膜と、前記第1素子分離膜の一側に形成されたゲートと、前記第1素子分離膜と前記ゲートの間の第2導電型ドリフト領域内に形成された第2導電型第1イオン注入領域を含む。

(もっと読む)

1 - 20 / 49

[ Back to top ]