Fターム[5F140BA05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 4族 (5,747) | SiGe (619)

Fターム[5F140BA05]に分類される特許

1 - 20 / 619

半導体装置の製造方法

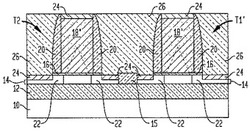

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置の製造方法

【課題】注入した導電性不純物により形成される結晶欠陥の密度を低減し、歩留まり率が向上するような半導体装置の製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板を加熱することにより、半導体基板の基板温度を200から500℃の間の所望の温度に維持すると同時に、半導体基板に導電性不純物をイオン注入法もしくはプラズマドーピング法を用いてドーピングし、ドーピングした導電性不純物を活性化させるための活性化処理を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

グラフェンを含む電極構造体及び電界効果トランジスタ

【課題】グラフェンを含む電極構造体及び電界効果トランジスタを提供する。

【解決手段】半導体層上のグラフェンと、グラフェン上の電極メタルと、を備え、該グラフェンは、半導体層と直接的に接触し、電極メタルは、グラフェンと直接的に接触する電極構造体である。半導体層は、シリコン、ゲルマニウム、シリコン・ゲルマニウム、III−V族半導体、及びII−VI族半導体を含むグループから選択された一つで形成される。グラフェンは、単層または二層のグラフェンで形成される。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】製造コストの低減、およびプロセス時間の短縮を可能とするfinFETの製造方法を提供する。

【解決手段】finFETは、ソース領域、ドレイン領域、およびソース領域とドレイン領域との間のチャネル領域を有するフィンを備えるように形成される。上記フィンは、半導体ウエハ上でエッチングされる。ゲートスタックは、上記チャネル領域に直接接触する絶縁層と、上記絶縁層に直接接触する導電性のゲート材料とを有するように形成される。上記ソース領域および上記ドレイン領域は、上記フィンの第一領域を露出するためにエッチングされる。次に、上記第一領域の一部が、ドーパントでドーピングされる。

(もっと読む)

半導体装置及びその製造方法

【課題】higher-k材料であるチタン酸化膜の半導体基板との界面を安定化でき、さらなる微細化に対応できるゲート構造を実現できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜と、該ゲート絶縁膜の上に形成されたゲート電極とを備えている。ゲート絶縁膜は、アナターゼ型酸化チタンを主成分とする高誘電率絶縁膜5であり、ゲート電極は、第1の金属膜6又は第2の金属膜8を含む導電膜から構成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】 チャンネルドーピングあるいは複雑なゲート電極パターン化の必要性なしに、複数のトランジスタが多閾値電圧を有する半導体装置を提供する。

【解決手段】 半導体装置及びその製造方法において、第1トランジスタは、第1材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第2トランジスタは、第3材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第3トランジスタは、第1材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第4トランジスタは、第3材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第1材料乃至前記第4材料の仕事関数は互いに異なる。第1トランジスタ乃至第4トランジスタは、互いに異なる閾値電圧を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置

【課題】トンネル型FETのオン電流とオフ電流との比と、単位基板面積あたりのオン電流を増大させる。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側面に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記半導体基板上に順に積層された第1導電型の下部主端子層と、中間層と、第2導電型の上部主端子層とを有し、前記ゲート絶縁膜を介して前記ゲート電極の側面に形成された積層体とを備える。さらに、前記上部主端子層は、前記ゲート電極の側面に、前記ゲート絶縁膜と半導体層を介して形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOI基板を用いることなく、絶縁層上にフィン型半導体を形成する。

【解決手段】半導体基板1上に支柱型半導体4を形成し、支柱型半導体4の下部を埋め込む絶縁層5を半導体基板1上に形成し、支柱型半導体4の上部の側面に接合されたフィン型半導体6を絶縁層5上に形成し、フィン型半導体6を絶縁層5上に残したまま支柱型半導体4を除去する。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】finFETにおける高集積化可能な、高濃度ソースドレインの形成方法の提供。

【解決手段】ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを形成する。チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有するゲートスタックを形成する。チャネル領域を残したまま、ソース領域およびドレイン領域をエッチング除去する。ソース領域およびドレイン領域に隣接したチャネル領域の両側にソースエピタキシー領域およびドレインエピタキシー領域を形成する。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を成長させながら、その場ドープされる。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置

【課題】ゲート絶縁膜を形成する際に、界面準位を低減しつつ、EOTのさらなる低減が実現可能な金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置を提供すること。

【解決手段】単結晶領域102を有する基板101上に、金属膜であって、該金属膜の酸化物の誘電率が酸化シリコン膜よりも高く、かつ金属膜の酸化物が単結晶領域102とエピタキシャル関係を有する金属膜103を、単結晶領域102と金属膜103とが界面反応しない基板温度で形成する(図1(b))。金属膜103が形成された基板101を、上記界面反応しない基板温度で、単結晶領域102と金属膜103とが界面反応しない酸素分圧の酸素ガス雰囲気に暴露する(図1(c))。酸素ガス雰囲気に暴露された基板103を、上記酸素分圧の酸素ガス雰囲気に保持し、金属膜の酸化物である金属酸化物高誘電体膜が結晶化する基板温度で熱処理する(図1(d)。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

1 - 20 / 619

[ Back to top ]