Fターム[5F140BA12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 非単結晶半導体材料 (90)

Fターム[5F140BA12]の下位に属するFターム

多結晶、ポリシリコン (59)

Fターム[5F140BA12]に分類される特許

1 - 20 / 31

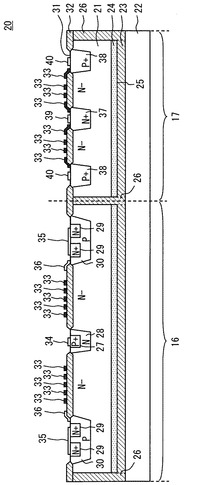

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

炭素ベース材料上の向上した結合界面を有する半導体構造体、その形成方法、及び、電子デバイス

【課題】 高密度で、構造部寸法がより小さく、より正確な形状の半導体構造体及び電子デバイスを提供する。

【解決手段】 炭素ベース材料の上面上に配置された少なくとも一層の界面誘電体材料を含む、半導体構造体及び電子デバイスが提供される。少なくとも一層の界面誘電体材料は、炭素ベース材料のものと同じである、典型的には六方晶短距離結晶結合構造を有し、従って、少なくとも一層の界面誘電体材料が、炭素ベース材料の電子構造を変えることはない。炭素ベース材料のものと同じ短距離結晶結合構造を有する少なくとも一層の界面誘電体材料の存在により、炭素ベース材料と、誘電体材料、導電性材料、又は誘電体材料及び導電性材料の組み合わせを含む、上にある任意の材料層との間の界面結合が改善される。その結果、改善された界面結合が、炭素ベース材料を含むデバイスの形成を容易にする。

(もっと読む)

半導体デバイスおよび方法

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

FINFETSおよびその形成方法

【課題】フィン電界効果トランジスタのソース/ドレイン構造を提供する。

【解決手段】基板上のフィンチャネル本体110a、110b、フィンチャネル本体110a、110b、上に配置されたゲート電極115、およびフィンチャネル本体110a、110b、に隣接して配置され、どのフィン構造も実質的に含まない、少なくとも1つのソース/ドレイン(S/D)領域120a,120b及び125a,125bを含むフィン電界効果トランジスタ(FinFET)。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 リーク電流の低減を実現しながらも従来に比べて更に素子サイズを縮小させることが可能な、高耐圧MOSトランジスタを実現する。

【解決手段】 P型ウェル10上に、チャネル領域chを隔てて、ドレイン領域12及びドレイン側ドリフト領域7を含むN型の第一不純物拡散領域と、ソース領域12及びそース側ドリフト領域8を含むN型の第二不純物拡散領域が形成されている。また、第一不純物拡散領域の一部上方、前記チャネル領域の上方、及び前記第二不純物拡散領域の一部上方にわたってゲート酸化膜6を介してゲート電極20が形成されている。ゲート電極20は、N型にドープされており、第一及び第二不純物拡散領域の上方に位置する部分の電極20bの不純物濃度が、前記チャネル領域の上方に位置する部分20aの不純物濃度よりも低濃度である。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜とゲート電極との間の界面層にカーボン層を導入して、低い閾値電圧を実現している例では、カーボン層中のカーボンはSi半導体基板中に入り、欠陥準位を形成するため、EWFが不安定であった。本発明は上記問題点を解決するためになされたもので、p−metalを用いたMIS型半導体装置において、EWFを安定して増加させることが可能な半導体装置を提供する。

【解決手段】半導体基板10と、半導体基10上に形成された絶縁膜20と、絶縁膜20上に形成され、且つ、CN基又はCO基を含む界面層30と、界面層30上に形成された金属層40とを備えて半導体装置を構成する。

(もっと読む)

半導体基板、半導体装置およびその製造方法

【課題】 (111)表面のシリコン(Si)基板に、原子レベルで超平坦な表面を実現する。

【解決手段】 シリコン基板(111)表面を、予め、フッ化アンモニウム(NH4F)溶液で表面処理した後、濃度68%,沸点120.7℃の共沸硝酸溶液内に浸漬して、前記シリコン基板表面に二酸化シリコン(SiO2)主体の被膜を形成し、ついで、濃度40重量%のフッ化アンモニウム(NH4F)溶液で上記二酸化シリコン(SiO2)主体の被膜をエッチング除去する。AFM像では、バイレイヤー ステップが観測され、表面粗さの指標(RMSラフネス値)が0.07nmと判定され、原子レベルでの超平坦な表面が形成できた。

(もっと読む)

ダイヤモンド電界効果トランジスタ

【課題】最大ドレイン電流密度が高く、長時間の電力動作にも耐える信頼性の高い、実用的なダイヤモンド電界効果トランジスタを提供すること。

【解決手段】p型またはn型の伝導性を有するダイヤモンド結晶層1をCVD装置などで成長させる。次に、金を蒸着させ、ソース電極2、ドレイン電極3を形成する。次に、76Torrに減圧したCVDチャンバ内で、上記ダイヤモンド結晶層1に、酸素ガス、水素ガス、トリメチルアルミニウムを供給し、ソース電極2とドレイン電極3との間のゲート部に厚さ8nmのAl(OH)3またはAl1-x-yOxHy化合物からなる絶縁層4を形成する。最後に、絶縁層4上にAl金属膜6を蒸着させてゲート部を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子形成領域間の分離絶縁膜を保護し、接合リークなしに素子と配線膜とを電気的に接続することができる半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板1に形成されて素子形成領域2を画定する分離絶縁膜3と、素子形成領域2に形成された素子と、素子および分離絶縁膜3を覆うように半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5をエッチングして形成されたコンタクトホール内に埋め込まれて素子と電気的に接続する配線膜6、7とを備え、少なくとも分離絶縁膜3と層間絶縁膜5との間に、前記エッチングによる分離絶縁膜3の浸食を防止するための3層以上の絶縁膜4a、4b、4cが積層されてなる保護積層膜4が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】高い平坦性の素子分離領域を得ることを課題とする。

【解決手段】トレンチ領域形成用のマスクとしての第1絶縁膜を半導体基板の直上に形成する工程と、マスクを用いて半導体基板にトレンチ領域を形成する工程と、トレンチ領域を含む半導体基板及び第1絶縁膜の直上に第2絶縁膜を形成することで、トレンチ領域上の第2絶縁膜からなる凹部と、第1絶縁膜上の第2絶縁膜からなる凸部と得る工程と、凹部の底面まで凸部を構成する第2絶縁膜を除去する第1除去工程と、第1絶縁膜及び第2絶縁膜を所定の膜厚まで化学的機械研磨法により除去することで、凹部及び凸部より形成された段差を20nm以下に低減する第2除去工程とを含み、第1絶縁膜及び第2絶縁膜が、同一の化学的機械研磨条件で研磨レートに差がない絶縁膜からなり、第2除去工程が、0.2〜0.6重量%の研磨粒子を含むスラリーを用いて行なわれることを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】 チャネル抵抗の上昇を最小限に抑えつつ、トランジスタのコンダクタンス特性に優れた半導体装置を提供する。

【解決手段】 半導体基板上にMOS型トランジスタが形成してある半導体装置において、MOS型トランジスタは、ウェルと逆導電の不純物をチャネルドープすることにより形成されるデプレッション型トランジスタであって、かつ、MOS型トランジスタのチャネル領域が、多結晶シリコン層もしくはアモルファスシリコン層からなる第1のチャネル領域と、単結晶シリコン層からなる第2のチャネル領域と、が順次設けられた積層構造を有しており、更に、第1のチャネル領域が、チャネルドープされた領域とウェルとの境界に形成されるPN接合よりも表面側に位置している。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置

【課題】円柱型構造のトランジスタの特性を向上させる。

【解決手段】導電層の形成された基板において前記導電層上に形成された柱状半導体と、前記柱状半導体の周囲に形成された絶縁層と、前記絶縁層の周囲に形成された一つのトランジスタのゲート電極を有しており、ゲート電極は、仕事関数の異なる少なくとも2層以上の導電膜の積層構造により構成されていることを特徴とする半導体装置を提供することにより、上記課題を解決する。

(もっと読む)

ゲート絶縁膜、ゲート絶縁膜の製造方法、ゲート絶縁膜の評価方法、半導体素子、電子デバイスおよび電子機器

【課題】薄膜化した場合においても、SBDが生じ難く、高い絶縁破壊耐性(TZDB、TDDBの改善)が経時的に得られるゲート絶縁膜、かかるゲート絶縁膜の製造方法および評価方法、さらに、このゲート絶縁膜を用いた半導体素子、信頼性の高い電子デバイスおよび電子機器を提供すること。

【解決手段】ゲート絶縁膜3は、半導体基板(基材)2上に化学的気相成膜法を用いて成膜され、平均厚さが10nm以下のものであり、シリコン、酸素原子および水素原子で構成され、その密度が2.5g/cm3以下なる関係を満足することにより、ソフトブレークダウンが生じるまでに流れる総電荷量が、40C/cm2以上となるよう構成されている。

(もっと読む)

1 - 20 / 31

[ Back to top ]