Fターム[5F140BA16]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | エピタキシャル基板 (980)

Fターム[5F140BA16]の下位に属するFターム

Si基板上に化合物半導体成長 (318)

Fターム[5F140BA16]に分類される特許

1 - 20 / 662

化合物半導体装置及びその製造方法

パワートランジスタ装置のための多層構造を作製する方法、ヘテロ接合電界効果トランジスタ装置のための多層構造を作製する方法、および窒化物系ヘテロ接合電界効果トランジスタ装置

高電子移動度トランジスタ構造及び方法

半導体装置

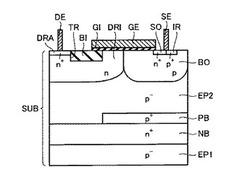

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

半導体装置

【課題】基板電位を安定化させることができる半導体装置を提供する。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】特性ばらつきの少ない絶縁ゲートを備えた窒化物半導体の半導体装置を提供すること。

【解決手段】 半導体装置が備える絶縁ゲートは、窒化物半導体層1上に設けられているアモルファスの酸化シリコン膜2と、酸化シリコン膜2上に設けられているゲート電極8を有している。ゲート電極8に対向する窒化物半導体層1が酸化されている。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

半導体装置

【課題】ノーマリオフで動作するとともに、高い耐圧と低いオン抵抗を具備した半導体装置を提供すること。

【解決手段】 半導体装置1では、ドレイン電極21が第1ヘテロ接合面32に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ソース電極29が第1ヘテロ接合面32に形成される2次元電子ガス層から電気的に絶縁可能に構成されているとともに第2ヘテロ接合面34に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ゲート部28が第2ヘテロ接合面34に対向しており、導通電極25が第1ヘテロ接合面32及び第2ヘテロ接合面34に形成される2次元電子ガス層の双方に対して電気的に接続可能に構成されている。第1ヘテロ接合面32に形成される2次元電子ガス層の電子濃度は、第2ヘテロ接合面34に形成される2次元電子ガス層の電子濃度よりも濃い。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

電界効果トランジスタの製造方法および電界効果トランジスタ

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

第III族金属窒化物−絶縁半導体ヘテロ構造電界効果トランジスタ

【課題】ヘテロ構造電界効果トランジスタに関して、電流崩壊、ゲートリークおよび高温信頼性などの課題を解消する。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に、第1の半導体層14、第2の半導体層15及びp型の不純物元素が含まれている半導体キャップ層16を順次形成する工程と、前記半導体キャップ層を形成した後、開口部を有する誘電体層21を形成する工程と、前記開口部において露出している前記半導体キャップ層の上に、p型の不純物元素が含まれている第3の半導体層17を形成する工程と、前記第3の半導体層の上にゲート電極31を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】オン抵抗を増加させることなく、ノーマリーオフとなる半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層14と、第2の半導体層14の上に形成された第3の半導体層15と、第3の半導体層15の上に形成されたゲート電極21と、第2の半導体層14の上に形成されたソース電極22及びドレイン電極23と、を有し、第3の半導体層15には、半導体材料にp型不純物元素がドープされており、第3の半導体層において、ゲート電極の直下にはp型領域15aが形成されており、p型領域15aを除く領域は、p型領域15aよりも抵抗の高い高抵抗領域15bが形成されている半導体装置。

(もっと読む)

半導体装置

【課題】横型DMOSの素子面積の増大を抑制し高耐圧化をはかる。

【解決手段】第1の半導体素子100Aは、第1半導体層12Aと、第2半導体層14Aと、第2半導体層に隣接する第3半導体層16Aと、第1絶縁層20Aと、第2半導体層の表面に選択的に設けられた第1ベース領域30Aと、第1ベース領域の表面に選択的に設けられた第1ソース領域32Aと、第1絶縁層の内部に設けられた第1ゲート電極40Aと、第1ベース領域の下に設けられ、第1半導体層の表面から第1ベース領域の側に延在する第1ドリフト層18Aと、第1ソース領域32Aに対向し、第1絶縁層20Aを挟んで第3半導体層16Aの表面に設けられた第1ドレイン領域34Aを有す。第1ドリフト層18Aの不純物元素の濃度は、第1半導体層12Aの不純物元素の濃度よりも低い。第1ドリフト層の不純物元素の濃度は、第2半導体層14Aの不純物元素の濃度よりも高い。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

1 - 20 / 662

[ Back to top ]