Fターム[5F140BB00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673)

Fターム[5F140BB00]の下位に属するFターム

チャネル形状、配置 (1,483)

短チャネル効果の積極的な利用

狭チャネル効果の積極的な利用 (2)

チャネル部の不純物プロファイル (687)

超格子構造、ヘテロ構造 (487)

Fターム[5F140BB00]に分類される特許

1 - 14 / 14

電界効果トランジスタの製造方法および電界効果トランジスタ

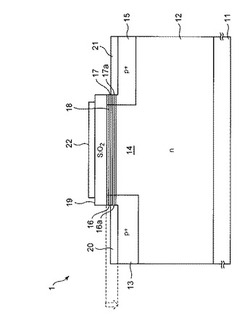

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置

【課題】半導体装置の実装時の特性値変動を従来よりも低減した、より高精度の特性を有する半導体装置を提供する。

【解決手段】特性値に影響の大きい対を形成したトランジスタ間の特性値変動、ここではK値の変動を等しくし、シフトを相殺する事でシフトを低減することが可能となる。希ガスのイオン注入などにより、MOSトランジスタ形成領域の結晶性を崩す。このことにより、対となったトランジスタ間でのシフトが同じになるため、結果的にパッケージング時の特性変化を低減することが可能となる。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 チャネル抵抗の上昇を最小限に抑えつつ、トランジスタのコンダクタンス特性に優れた半導体装置を提供する。

【解決手段】 半導体基板上にMOS型トランジスタが形成してある半導体装置において、MOS型トランジスタは、ウェルと逆導電の不純物をチャネルドープすることにより形成されるデプレッション型トランジスタであって、かつ、MOS型トランジスタのチャネル領域が、多結晶シリコン層もしくはアモルファスシリコン層からなる第1のチャネル領域と、単結晶シリコン層からなる第2のチャネル領域と、が順次設けられた積層構造を有しており、更に、第1のチャネル領域が、チャネルドープされた領域とウェルとの境界に形成されるPN接合よりも表面側に位置している。

(もっと読む)

半導体装置の製造方法

【課題】ニッケルシリサイドの耐熱性を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】ゲート領域2、ソース領域4及びドレイン領域5が形成された半導体基板1上にニッケル(またはニッケル合金)6を形成し(図1(A))、第1アニール工程でダイニッケルシリサイド7を形成し(図1(B))、プラズマ処理工程では水素イオンを含有するプラズマにより、水素イオンをダイニッケルシリサイド7またはダイニッケルシリサイド7の下部のゲート領域2、ソース領域4及びドレイン領域5に注入し、第2アニール工程でダイニッケルシリサイド7をニッケルシリサイド8に相変態させる(図1(C))。

(もっと読む)

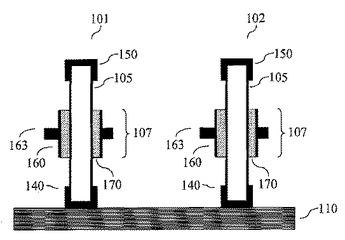

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高性能化が必要な回路ブロックや回路部に対して応力を付加することにより、その回路ブロックや回路部の高性能化が実現できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体チップ基板30内に少なくとも金属酸化物半導体(MOS)トランジスタ36を含む回路と、この回路を含み、上部にこの回路を保護する保護膜41で覆われた回路ブロックを複数有してなる半導体装置20であって、この半導体装置20の電流能力およびしきい値電圧が所定の値を満たさない高性能化が必要な回路ブロックの上部のみに、少なくとも保護膜41を介して複数のバンプ23a、23b、23cが形成され、この複数のバンプ23a、23b、23cはMOSトランジスタ36に応力を付加して移動度を増加させて高性能化が実現できる。

(もっと読む)

半導体装置及びその製造方法

【課題】縦型トランジスタのカットオフ時のリーク電流を低減する半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板と前記半導体基板の内部に形成された第1の不純物拡散領域と前記第1の不純物拡散領域の上方に形成された柱状半導体層と前記柱状半導体層の側方に形成されたゲート絶縁膜と前記ゲート絶縁膜の側方に形成されたゲート電極と前記不純物拡散領域の上方で前記ゲート電極に接して形成された絶縁体からなる層間膜と前記柱状半導体層の上方で前記ゲート電極に接して形成された絶縁体からなるスペーサと前記柱状半導体層の上方に形成された第2の不純物拡散領域とを具備し前記柱状半導体層の略中央に絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】動作特性が向上した半導体装置の製造方法及びそれによって製造された半導体装置を提供する。

【解決手段】基板上にNMOSトランジスタを形成し、NMOSトランジスタ上に第1層間絶縁膜を形成し、第1層間絶縁膜を脱水素化することを含む半導体装置の製造方法。脱水素化することは、第1層間絶縁膜のストレスを変化させうる。特に、第1層間絶縁膜は脱水素化の後、200MPa以上の引張ストレスを有しうる。脱水素化された層間絶縁膜を含む半導体装置も提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの駆動力を調整する。

【解決手段】SRAMアクセス領域SAにおけるN型のMISトランジスタの上に、圧縮応力含有絶縁膜50および引っ張り応力含有絶縁膜51を形成する。一方、SRAMドライブ領域SDにおけるN型のMISトランジスタの上に、引っ張り応力含有絶縁膜51を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されてもnMOS及びpMOSのそれぞれの素子特性を向上させることが可能な半導体装置及びその製造方法を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板上に絶縁膜を介して形成された第1のゲート電極と、前記第1のゲート電極を挟んで前記半導体基板中に形成された第1の拡散層と、前記第1の拡散層に形成された第1方向の内部応力を内在する第1の導電体層とを具備する第1の半導体素子と、前記半導体基板上に絶縁膜を介して形成された第2のゲート電極と、前記第2のゲート電極を挟んで前記半導体基板中に形成された第2の拡散層と、前記第2の拡散層に形成され、前記第1の導電体層と同じ元素により構成され、前記第1方向と逆向きの第2方向の内部応力を内在する第2の導電体層とを具備する第2の半導体素子と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長が100nm以下であってもオフリーク電流を十分に抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】N型ウェル並びにゲート絶縁膜32及びゲート電極33が形成された半導体基板31に対し、リンをイオン注入することにより、半導体基板31の表面にN型ポケット層34を形成する。ゲート電極33の長さ(ゲート長)は、100nm以下である。イオン注入は、4方向からの斜めイオン注入により行う。また、例えば、注入エネルギを15乃至30keVとし、ドーズ量を1方向当たり3×1012乃至1.5×1013cm-2とする。この方法によれば、N型ポケット層34の形成にあたり、リンのイオン注入を行っているので、ゲート長を100nm以下と短くしても、チャネル近傍に強い電界が発生することを抑制することができる。このため、BD間リーク電流を抑制して、オフリーク電流を低減することが可能である。

(もっと読む)

1 - 14 / 14

[ Back to top ]