Fターム[5F140BB02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル形状、配置 (1,483) | 基板表面に平行でないチャネル (901)

Fターム[5F140BB02]の下位に属するFターム

段差部に形成されたもの (818)

Fターム[5F140BB02]に分類される特許

1 - 20 / 83

半導体装置とその製造方法

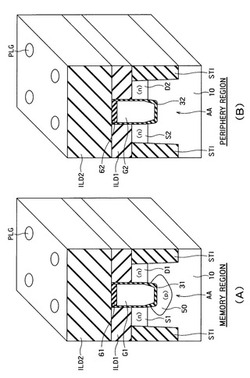

【課題】製造プロセスが容易であり、かつ、Fin型FETおよび従来型トランジスタを混載した半導体記憶装置を提供することである。

【解決手段】半導体記憶装置は第1の領域および第2の領域を備える。メモリ部のトランジスタは第1導電型のFin型半導体層を備える。第1導電型の第1のソース層および第1のドレイン層はFin型半導体層の両端に設けられる。第1のゲート電極はFin型半導体層の両側面に設けられる。第2導電型のパンチスルーストッパ層は第1のゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は第1のソース層および第1のドレイン層の下の不純物濃度よりも高い。周辺回路部のトランジスタは、第2のゲートトレンチを備える。第1導電型の第2のソース層および第1導電型の第2のドレイン層は、第2のゲートトレンチの両側に設けられる。第2のゲート電極は、第2のゲートトレンチ内に充填される。

(もっと読む)

半導体装置

【課題】短チャネル効果の抑制およびオフリーク電流の抑制が可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置は、半導体基板において素子分離領域によって仕切られた素子領域と、前記素子領域を横切る所定の方向に沿って前記素子領域の表層に設けられたゲートトレンチにより分離されて前記素子領域の表層に形成されたソース領域およびドレイン領域とを備える。また、実施形態の半導体装置は、少なくとも一部が前記ゲートトレンチ内にゲート絶縁膜を介して埋め込まれて前記ソース領域およびドレイン領域よりも深い位置まで形成されたゲート電極を備える。ドレイン領域における前記ゲート絶縁膜と接触する界面は、前記ゲート電極側に突出した凸部を有する。

(もっと読む)

電界効果トランジスタ

【課題】高耐圧性をより確実に実現することができる電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、前記キャリア走行層上に形成され、前記キャリア走行層とは反対の導電型を有し、前記キャリア走行層内部に到る深さまで形成されたリセス部によって分離したキャリア供給層と、前記分離した各キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記分離した各キャリア供給層上にわたって前記リセス部内における前記キャリア走行層の表面を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備え、前記リセス部の前記キャリア供給層上面からの深さが、前記キャリア供給層の層厚より大きく200nm以下である。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体を用いたノーマリーオフ動作の電界効果型トランジスタにおいて、閾値電圧が制御でき、十分な素子特性が得られるようにする。

【解決手段】c軸方向に結晶成長された窒化物半導体から構成されて主表面が極性面とされた第1領域121,第1領域121より厚く形成された第2領域122,および、第1領域121と第2領域122との間に形成されて主表面が半極性面とされた第3領域123を備える半導体層101を備える。また、窒化物半導体装置は、第1領域121における半導体層101の上に形成されたドレイン電極102と、第2領域122における半導体層101の上に形成されたソース電極103と、第3領域123における半導体層101の上に形成されたゲート電極104とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】消費電力が低く、かつ、動作時の電流値が高い半導体装置およびその製造方法を提供する。

【解決手段】実施形態の半導体装置は、第1導電型の基板上のソース領域に形成された第2導電型の第1の不純物拡散層と、前記基板上のポケット領域に形成された第1導電型の第2の不純物拡散層と、前記基板上のドレイン領域に形成された第1導電型の第3の不純物拡散層と、前記第1乃至第3の不純物拡散層の表面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲートと、を含む。前記ポケット領域は前記ソース領域に隣接し、リセスを有するように形成される。前記ゲートは、前記ゲート絶縁膜を介して前記リセスを埋め込むように前記ゲート絶縁膜上に形成される。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーデバイスの高耐圧とオン抵抗の低減とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板101内のソース領域107A、ドレイン領域107B、及びドレイン領域107Bに接したドリフト領域105と、ソース領域107A及びドレイン領域107B間のドリフト領域105内のSTI絶縁層I−2と、STI絶縁層I−2上、ドリフト領域105上、並びに、ソース領域107A及びドレイン領域107B間のチャネル領域上のゲート電極110とを備える。STI絶縁層I−2は、第1及び第2のトレンチの内面上の第1の酸化膜102及び窒化膜103と、第1及び第2のトレンチを満たす窒化膜103上の第2の酸化膜104とを備える。第2のトレンチは、第1のトレンチ内に形成され、第1のトレンチの底面よりも低い底面を有し、第1のトレンチの幅よりも狭い幅を有する。

(もっと読む)

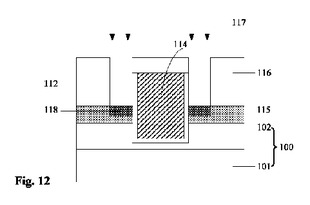

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】特性を十分に向上することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、SiC膜11を形成する工程と、このSiC膜11の表面にSiを供給した状態で、このSiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。このようにすれば、Siを供給した状態でSiC膜11を熱処理することにより、SiC膜11をエネルギ的に安定な表面状態に再構成させることができる。その結果、一周期が100nm以上のファセットが得られ、ファセットの平坦部分の長さを従来に比べて長くすることができる。したがって、界面準位の密度を減少することによりキャリアの移動度を向上することができ、半導体装置の特性を十分に向上することができる。

(もっと読む)

半導体ヘテロ電界効果トランジスタ

【課題】ピエゾ電界により発生するシートキャリアの利用とチャネル部におけるピエゾ電界により深いディプレッション形成の抑制とを提供できる半導体ヘテロ電界効果トランジスタを提供する。

【解決手段】第1及び第3の領域23a、23cの主面24a、24cの法線ベクトルNV1、NV3は、該III族窒化物半導体のc軸Cxに直交する面に対して有限な角度で傾斜する。第2の領域23bの主面24bの法線ベクトルNV2は、該III族窒化物半導体のc軸Cxに直交する面に沿って延在する。第2の領域23bにおけるチャネル層25の第2の領域25bのピエゾ分極PZC2は、III族窒化物半導体領域23からバリア層27への方向に向いている。第1及び第3の領域23a、23cにおけるチャネル層25の第1及び第3の領域25a、25cのピエゾ分極PZC1、PZC3は、バリア層27からIII族窒化物半導体領域23への方向に向いている。

(もっと読む)

トレンチDMOSトランジスタの製造方法

トレンチDMOSトランジスタの製造方法であって、半導体基板上に酸化物層及びバリア層を形成するステップと、トレンチを形成するために、酸化物層及び半導体基板をエッチングするステップと、トレンチの内壁にゲート酸化物層を形成するステップと、バリア層上にポリシリコン層を形成し、トレンチを充填するステップと、トレンチゲートを形成するために、ポリシリコン層をエッチバックするステップと、バリア層及び酸化物層を除去するステップと、拡散層を形成するために、トレンチゲートの両側の半導体基板内にイオンを注入するステップと、拡散層上をフォトレジスト層で覆い、ソース/ドレイン配置を定義するステップと、拡散層内にイオンを注入するステップと、トレンチゲートの両側に側壁を形成するステップと、拡散層及びトレンチゲート上に金属シリサイド層を形成するステップとを含む。低コスト及び改善された製造効率を伴う効果的な結果が達成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ゲート・オール・アラウンドトランジスタの複数のチャネルそれぞれに流れる電流を均一にし、ゲート・オール・アラウンドトランジスタの信頼性を向上させる。

【解決手段】半導体基板と、半導体基板上に一定の間隔をおいて形成された第1の半導体層上に第2の半導体層を形成した積層構造が複数積み重なったソース・ドレイン領域と、第2の半導体層の同一レイヤ間をそれぞれ接続するようにワイア状に形成された複数のチャネル領域と、前記複数のチャネル領域をそれぞれ包み込むようにゲート絶縁膜を介して形成されたゲート電極とを具備し、チャネル領域のチャネル幅は、半導体基板から離れるほど狭く形成され、第2の半導体層及びチャネル領域の膜厚は、半導体基板から離れるほど広く形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コスト増や大型化を招くことなく、耐圧特性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体層13と、半導体層13上のゲート電極15、ソース電極16sおよびドレイン領域16dと、を備えたMOSFET1は、半導体層13中であってこの半導体層13の上面および下面それぞれから離間する中間領域に所定の導電性を備えたドーパント(例えばシリコン(Si))を含む縦方向電界緩和領域19を備えている。

(もっと読む)

電界効果トランジスタ

【課題】オン動作時における耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、キャリア走行層上に形成され、キャリア走行層とは反対の導電型を有し、キャリア走行層に到る深さまで形成されたリセス部によって分離したキャリア供給層と、分離した各キャリア供給層上にリセス部を挟んで形成されたソース電極およびドレイン電極と、分離した各キャリア供給層上にわたってリセス部内におけるキャリア走行層の表面を覆うように形成されたゲート絶縁膜と、リセス部においてゲート絶縁膜上に形成されたゲート電極と、を備え、ソース電極側のキャリア供給層は、該ソース電極直下に位置するソースコンタクト領域と、ゲート電極の下方に位置し、ソースコンタクト領域よりもキャリア濃度が低いソース電界緩和領域とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】閾値電圧が制御されて、且つ特性のばらつきが抑制された半導体装置を提供する。

【解決手段】基板2と、STI素子分離領域3と、活性領域4と、活性領域4に形成された第1ゲートトレンチ5と、第1ゲートトレンチ5の底部に設けられた第2ゲートトレンチ6と、第1及び第2ゲートトレンチ5,6にゲート絶縁膜7を介して埋め込み形成されたゲート電極8と、第1ゲートトレンチ5の幅方向両側の活性領域4にイオンを注入することによって形成されたソース/ドレイン領域9とを備え、第2ゲートトレンチ6と第2ゲートトレンチ6の長手方向に位置するSTI素子分離領域3との間に、チャネルを構成するシリコン薄膜部10が設けられていることを特徴とする半導体装置1。

(もっと読む)

半導体装置の製造方法

【課題】 高誘電率ゲート絶縁膜とメタルゲート電極を用いたメタルゲートCMOSの製造方法を簡略化する。

【解決手段】 高誘電率ゲート絶縁膜6上にシリコン膜7を形成し、PMOS領域のシリコン膜7のみを選択的に窒化してSiN膜9に置換する。そしてNMOS領域上のシリコン膜7及びPMOS領域上のSiN膜9上にキャップ膜としてのLa(O)膜11及びメタル電極のW膜12を形成した後、加熱処理して、La(O)膜11のLa元素をNMOS領域の高誘電率ゲート絶縁膜に拡散させる。この際、PMOS領域においては、SiN膜9によりLa元素の拡散をブロックする。これにより、NMOSFETとPMOSFETの作りわけを容易に行える。また、窒化されやすい高誘電率ゲート絶縁膜6であれば、シリコン膜7を省略して、窒化処理によりPMOS領域の高誘電率ゲート絶縁膜6だけを選択的に窒化してもよい。

(もっと読む)

トレンチゲート型MOSトランジスタを有する半導体装置の製造方法

【課題】トレンチゲート形成方法において、STI領域のライナー窒化膜がエッチングされることなく、隣接ゲート電極が短絡することのない、トレンチゲートの形成方法を提供する。

【解決手段】ハードマスクとして、活性領域15上のパッドシリコン酸化膜10、シリコン膜11及びシリコン窒化膜12の積層構造を用い、シリコン窒化膜12はシリコン膜11にパターンを形成するためのハードマスクとなり、パッドシリコン酸化膜10のエッチングに際して消失するように、また、活性領域へのトレンチ形成にはシリコン膜11及びパッドシリコン酸化膜10をマスクとし、シリコン膜11は、トレンチ形成後に消失するように、各ハードマスクの厚みを最適化する。

(もっと読む)

炭化珪素基板の表面処理方法および半導体装置

【課題】より広い幅を有するテラスを形成することができる炭化珪素基板の表面処理方法およびその炭化珪素基板の表面処理方法により表面処理された炭化珪素基板を用いて製造された半導体装置を提供する。

【解決手段】炭化珪素基板の表面上に固体状シリコンを設置する工程と、固体状シリコン上に蓋材を設置する工程と、蓋材の設置後に固体状シリコンが設置された炭化珪素基板を固体状シリコンの融点以上の温度に加熱して固体状シリコンを溶融させる工程と、固体状シリコンの溶融後に固化した固化シリコンから炭化珪素基板を分離する工程とを含む炭化珪素基板の表面処理方法とその炭化珪素基板の表面処理方法により表面処理された炭化珪素基板を用いて製造された半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加して、チャネル領域に歪みを与えるための新たな手法を提供する。

【解決手段】基板と、前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極の側面に設けられた側壁絶縁膜と、前記基板のソースドレイン領域に埋め込まれており、前記基板のチャネル領域に応力を印加する応力印加層であって、前記基板と前記応力印加層との界面の上端の高さが、前記基板と前記ゲート絶縁膜との界面の下端の高さよりも高いような応力印加層と、を備えることを特徴とする半導体装置。

(もっと読む)

1 - 20 / 83

[ Back to top ]