Fターム[5F140BD13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | 金属酸化膜 (2,702) | 複合金属酸化膜 (873)

Fターム[5F140BD13]に分類される特許

1 - 20 / 873

半導体装置の製造方法

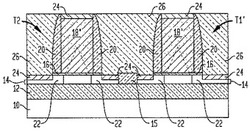

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

電極構造体、それを備える窒化ガリウム系の半導体素子及びそれらの製造方法

【課題】電極構造体、それを備える窒化ガリウム系の半導体素子及びそれらの製造方法を提供する。

【解決手段】GaN系の半導体層GL10と、GaN系の半導体層上に備えられた電極構造体500A,500Bと、を備え、電極構造体500A,500Bは、導電物質を含む電極要素50A、50Bと、電極要素50A,50BとGaN系の半導体層200との間に備えられた拡散層5A、5Bと、を備え、拡散層5A,5Bは、n型ドーパントを含み、n型ドーパントは、4族元素を含み、拡散層と接触したGaN系の半導体層200の領域は、n型ドーパント(例えば、4族元素)でドーピングされる窒化ガリウム系の半導体素子である。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】金属膜あるいは金属酸化膜の成膜量に伴うことなく含有している金属元素の濃度分布に偏りのないゲート絶縁膜を提供する。

【解決手段】図2に示すように、半導体基板1上に、シリコン酸化膜より高い誘電率を有する高誘電体膜10を形成する高誘電体膜形成工程と、高誘電体膜10上に、第1の金属元素を有する第1の金属膜あるいは金属酸化膜20を成膜する第1の成膜工程と、高誘電体膜10に第1の金属元素を拡散させる拡散工程と、高誘電体膜10上に金属元素吸収膜50を成膜する第2の成膜工程と、金属元素吸収膜50に、第1の金属元素を含ませる吸収工程と、金属元素吸収膜60を選択的に除去する除去工程の6工程を含んでいる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】EOTの低減及びリーク電流の低減を両立できる半導体装置の製造方法を提供すること。

【解決手段】被処理体上に第1の高誘電率絶縁膜を成膜する第1の成膜工程と、前記第1の高誘電率絶縁膜を、650℃以上で60秒未満の間熱処理する結晶化熱処理工程と、前記第1の高誘電率絶縁膜上に、前記第1の高誘電率絶縁膜の金属元素のイオン半径よりも小さいイオン半径を有する金属元素を有し、前記第1の高誘電率絶縁膜よりも比誘電率が大きい、第2の高誘電率絶縁膜を成膜する第2の成膜工程と、を含む、半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

半導体装置とその製造方法

【課題】 チャンネルドーピングあるいは複雑なゲート電極パターン化の必要性なしに、複数のトランジスタが多閾値電圧を有する半導体装置を提供する。

【解決手段】 半導体装置及びその製造方法において、第1トランジスタは、第1材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第2トランジスタは、第3材料で形成された下層と第2材料で形成された上層とを含むゲートスタックを有する。第3トランジスタは、第1材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第4トランジスタは、第3材料で形成された下層と第4材料で形成された上層とを含むゲートスタックを有する。第1材料乃至前記第4材料の仕事関数は互いに異なる。第1トランジスタ乃至第4トランジスタは、互いに異なる閾値電圧を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク基板上に形成されたフィン型トランジスタにおいて、ソース/ドレインボトム領域での接合リーク電流の増大を抑制しつつ、ソース/ドレインとソース/ドレイン上に形成されたシリサイドとの接触抵抗を低減する。

【解決手段】フィン型半導体3の両端部に形成した高濃度不純物拡散層10からなるソース/ドレインの側面に、フィン型半導体3の上部の表面が露出するようにしてオフセットスペーサ7およびサイドウォールスペーサ8を形成し、フィン型半導体3の上部の高濃度不純物拡散層10の表面には、シリサイド層9を形成する。

(もっと読む)

半導体装置、半導体装置の製造方法、および試験装置

【課題】ゲートリーク電流が少なく、かつ電流コラプスが抑えられた半導体装置の提供。

【解決手段】第1の態様においては、窒化物系半導体で形成された半導体層110と、半導体層上に開口を有して設けられ、タンタル酸窒化物を含む第1絶縁膜120と、第1絶縁膜の開口において半導体層上に積層された第2絶縁膜130と、第2絶縁膜上に設けられたゲート電極140と、を備える半導体装置を提供する。ここで、第2絶縁膜は、第1絶縁膜より絶縁性が高い絶縁膜により構成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOI基板を用いることなく、絶縁層上にフィン型半導体を形成する。

【解決手段】半導体基板1上に支柱型半導体4を形成し、支柱型半導体4の下部を埋め込む絶縁層5を半導体基板1上に形成し、支柱型半導体4の上部の側面に接合されたフィン型半導体6を絶縁層5上に形成し、フィン型半導体6を絶縁層5上に残したまま支柱型半導体4を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

1 - 20 / 873

[ Back to top ]