Fターム[5F140BE01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成前の処理 (668)

Fターム[5F140BE01]の下位に属するFターム

Fターム[5F140BE01]に分類される特許

1 - 20 / 117

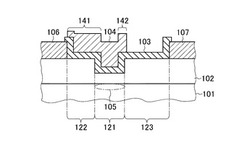

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

コーナートランジスターとその製作方法

【課題】改善された性能を有し、かつ縮小されたサイズを有することのできるコーナートランジスターを提供する。また、コーナートランジスターを製作する方法を提供し、それがトランジスターの性能を改善するとともに、簡単なプロセスを介して、そのサイズを縮小することができる。

【解決手段】この発明のコーナートランジスターを製作する方法を以下に記述する。分離構造(isolation structure)が基板中に形成されて能動エリア(active area)を定義する。処理プロセスが実施されて、能動エリア中の基板がそのトップエッジに鋭いコーナーを有するようにする。能動エリア中の基板がゲート誘電層により被覆される。ゲート導体がゲート誘電層上に形成される。ソース領域およびドレイン領域がゲート導体両側の基板中に形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】低コストでしきい値電圧のバラツキの少ないノーマリーオフ化されたHEMTを提供する。

【解決手段】基板10の上方に半導体層21〜24を形成する工程と、半導体層23〜24にフッ素成分を含むガスを用いたドライエッチングによりリセス51となる開口部を形成する工程と、半導体層を加熱することによりリセス51の側面及び底面に付着しているフッ素を半導体層22〜24に拡散させフッ素を含む領域を形成する工程と、リセス51の内面及び半導体層22〜24上に絶縁膜30を形成する工程と、リセス51が形成されている領域に絶縁膜30を介し電極41を形成する工程と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置の製造方法

【課題】1回のゲート絶縁膜形成工程で複数の厚みのゲート絶縁膜を同一の半導体基板上に形成することができるとともに、ゲート絶縁膜に酸化促進物質による欠陥が発生するのを抑制することができる半導体装置の製造方法の提供。

【解決手段】半導体基板の所定領域に拡散性を有する酸化促進物質を注入する酸化促進物質注入工程と、上記半導体基板に熱処理を行うことで当該半導体基板に上記酸化促進物質の注入量に応じた複数の厚みの酸化膜を形成する酸化膜形成工程と、上記所定領域に注入された酸化促進物質を拡散させることで上記酸化膜中に存在する上記酸化促進物質の濃度を低下させる酸化促進物質拡散工程とを備える。

(もっと読む)

炭化ケイ素半導体デバイス

【課題】航空機の配電システムでの使用に際しても、十分に信頼できる炭化シリコンを使用したMOSFETを提供する。

【解決手段】炭化シリコンMOSFETのゲート絶縁膜16を、シリコンからなる第1の層と炭化シリコンからなる第2の層15に貼着することによって、第1の層と第2の層との間に境界面を形成した後、シリコンからなる第1の層の一部又は全部を酸化することにより境界面に炭素クラスターの存在しないゲート絶縁膜16を形成する。

(もっと読む)

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】チャネル移動度と閾値電圧とのトレードオフの関係を打破し、チャネル移動度を向上させ、かつ、閾値電圧の低下を抑えた炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】この発明に係る炭化珪素半導体装置1aの製造方法は、炭化珪素エピタキシャル層6を有する炭化珪素基板2の炭化珪素エピタキシャル層6上に、リンをドープした多結晶珪素膜18を形成する工程と、多結晶珪素膜18を熱酸化してゲート絶縁膜12を形成する工程と、を備えた。

(もっと読む)

炭化珪素半導体装置の製造方法および炭化珪素半導体装置の製造装置

【課題】特性を向上できるSiC半導体装置の製造方法およびSiC半導体装置の製造装置を提供する。

【解決手段】SiC半導体装置の製造方法は、SiC半導体の第1の表面に第1の酸化膜を形成する工程(ステップS4)と、第1の酸化膜を除去する工程(ステップS5)と、SiC半導体において第1の酸化膜が除去されることにより露出した第2の表面に、SiC半導体装置を構成する第2の酸化膜を形成する工程(ステップS6)とを備える。第1の酸化膜を除去する工程(ステップS4)と、第2の酸化膜を形成する工程(ステップS6)との間において、SiC半導体は大気が遮断された雰囲気内に配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

電界効果半導体装置の製造方法

【課題】半導体装置を構成する半導体層の表面上にAlOx層を安価に形成でき、且つAlOx層を厚膜化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1と、前記半導体基板1上に形成された窒化物系化合物半導体層2、3、4と、前記窒化物系化合物半導体層2、3、4上に隣接して形成された酸化アルミニウム層7と、を備える半導体装置の製造方法であって、

前記窒化物系化合物半導体層2、3、4上に多結晶又は非晶質の窒化アルミニウム層6を形成する第1の工程と、前記多結晶又は非晶質の窒化アルミニウム層6を熱酸化して前記酸化アルミニウム層7を得る第2の工程と、を備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の信頼性の高い半導体装置を提供する。

【解決手段】半導体基板42上に台形状の凸部領域と台形状の凹部領域を設け、凹部領域のシリコン表面にはゲート酸化膜45が設けられ、ゲート酸化膜上にはゲート電極46が形成されている。凹部領域に設けられたゲート電極46の両側の凸部領域にはソース・ドレイン高濃度領域48が位置し、ソース・ドレイン高濃度領域48とゲート電極46の間にはソース・ドレイン低濃度領域47が形成されている。ソース・ドレイン高濃度領域48の上表面には第1層目の金属配線49と第2層目の金属配線50と第3層目の金属配線52が積層され、ソース・ドレイン高濃度領域48から第3金属配線までの接続にコンタクトホールやビアホールなどを利用していない。このように本発明の半導体装置は、コンタクトホールやビアホールなどの接続孔を形成しないで素子と配線との接続や配線間接続を行なうことができる。

(もっと読む)

電荷トラップを有するゲート誘電体を含む揮発性メモリ及びその製造方法

【課題】チャネルイオン注入領域のドーピング濃度を相対的に低下しながらも所望のしきい電圧値を得ることができる揮発性メモリを提供する。

【解決手段】ゲート誘電体として順次積層された下部ゲート誘電体、電荷トラップのための中間ゲート誘電体、及び上部ゲート誘電体を備えたセルトランジスタと、ゲート誘電体として単一層の酸化膜を備えたロジック用トランジスタとで、揮発性メモリを構成する。

(もっと読む)

半導体装置の製造方法

【課題】FIN状の半導体部により構成されるFIN型トランジスタを有する半導体装置において、FIN状の半導体部の上面の不純物濃度と側面の不純物濃度との差を小さくすることにより、FIN型トランジスタの特性ばらつきを抑えて、信頼性を向上させる。

【解決手段】

FIN状の半導体部10の上面に2〜5nm程度の厚さのパッド絶縁膜3を形成し、FIN状の半導体部10の一方の側面に、第1注入角度θ1を有する斜め方向からクラスタイオンを注入した後、FIN状の半導体部10の他方の側面に、第1注入角度θ1と対称の第2注入角度θ2を有する斜め方向からクラスタイオンを注入する。その後、FIN状の半導体部10に注入されたクラスタイオンを活性化して、ソース領域およびドレイン領域の一部を構成する拡散領域を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

酸化膜形成方法

【課題】膜中欠損を生じさせることなくGe基板の表面にGe酸化膜を形成する。

【解決手段】Ge基板2の表面にGe酸化膜を形成するプロセスシステム1の酸化炉13において、1000Pa以下の圧力及び300℃以下の基板温度のもとでGe基板2にオゾン供給装置11からオゾンガスを供して当該基板の表面にGe酸化膜を形成する。室温よりも低温の基板温度のもとで前記基板に前記オゾンガスを供給してGe基板2上にオゾン分子層を形成させる。次いで、前記オゾンガスの供給を遮断させた後、Ge基板2を室温まで加熱することにより前記オゾン分子層によって当該基板の表面を酸化させてGe酸化膜を形成させる。Ge基板2が室温まで達した後に前記加熱を遮断して当該基板の温度を室温よりも低温に降下させるとよい。Ge基板2を加熱するための加熱源として赤外光光源を用いるとよい。前記オゾンガスはオゾン濃度が100%であるとよい。

(もっと読む)

半導体デバイス及びその製造方法

【課題】従来よりも界面準位密度を低減させることができる半導体デバイス及びその製造方法を提供する。

【解決手段】窒素ガス雰囲気下で低ダメージなECRプラズマを用いたECRプラズマ処理を行うことにより、III−V族化合物半導体層2の表面を窒化処理したことで、当該III−V族化合物半導体層2にIn−N結合及びGa−N結合を形成しAs酸化物を抑制して界面特性を向上させることができ、かくして従来よりも界面準位密度が低減されたMOSFET1を提供できる。また、アニール処理することにより、窒化処理層5においてGa−N結合が支配的となった界面結合状態を形成し、界面準位密度を一段と低減させることができる。

(もっと読む)

エンハンスメント型窒化ガリウム高電子移動度トランジスタ

実施形態には、これに限定されないが、第1バリア層と、該第1バリア層上の窒化ガリウムチャネル層と、該窒化ガリウムチャネル層上に存在し、第1サブレイヤーと第2サブレイヤーと第3サブレイヤーとを備える第2バリア層と、を有するヘテロ構造を備える装置とシステムが含まれる。該第1バリア層、第1サブレイヤーおよび第3サブレイヤーは各々アルミニウムを含んでいてもよい。他の実施形態も、本明細書に記載され特許請求される。 (もっと読む)

III−V族加工基板の製造方法およびそのIII−V族加工基板

【課題】パッシベーション層を備え、改善した性能を持つデバイスを実現できるIII−V族加工基板およびその製造方法を提供する。

【解決手段】III−V族加工基板の製造方法は、<110>または<111>の結晶方位を持つ第1のIII−V化合物からなる上側層(2)を備えたベース基板(I)を用意すること、第2のIII−V化合物からなるバッファ層(3)を少なくとも形成することを含んだ、中間層(II)を形成することであって、中間層(II)は、ベース基板の上側層(2)の上に位置し、これと接触するようにすること、IV族半導体材料からなる擬似格子整合パッシベーション層(4)を成長させることであって、擬似格子整合パッシベーション層は、中間層(II)の上に位置し、これと接触するようにすることを含む。

(もっと読む)

半導体装置の製造方法

【課題】 シャロートレンチアイソレーション法により素子分離絶縁膜を形成した後に、従来の方法で自然酸化膜除去のための水素熱処理を行うと、所望のトランジスタ特性が得られない場合がある。

【解決手段】 シリコン基板を、水素を含む還元性雰囲気中で、温度が930℃〜1030℃の範囲内であり、時間が0秒よりも長くかつ30秒以下の条件で第1の熱処理を行う。第1の熱処理後、水素を含む還元性雰囲気中に配置したまま、温度が第1の熱処理時の基板温度よりも低く、かつ900℃〜980℃の範囲の基板温度に、0秒よりも長くかつ30秒よりも短い時間維持して第2の熱処理を行う。

(もっと読む)

1 - 20 / 117

[ Back to top ]