Fターム[5F140BE06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜の製造 (6,009) | ゲート絶縁膜を形成するための処理 (4,399) | 直接変換 (2,415)

Fターム[5F140BE06]の下位に属するFターム

Fターム[5F140BE06]に分類される特許

1 - 20 / 55

半導体装置の製造方法及び半導体装置

【課題】導電材料のゲートトレンチへの埋め込みが容易な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上の絶縁膜と、絶縁膜に設けられた凹部と、凹部の底部であって半導体基板上に設けられたゲート絶縁膜とを形成する工程と、凹部の内壁面上と絶縁膜の上面上に、第1金属を含む導電材料で第1ゲート電極膜を形成する工程と、第1ゲート電極膜上に、凹部の側面部分の一部は覆わないように、導電材料の融点よりも高い融点を持つ材料でカバー膜を形成する工程と、カバー膜が形成された状態で、熱処理を行って、第1ゲート電極膜をリフローさせる工程とを有する。

(もっと読む)

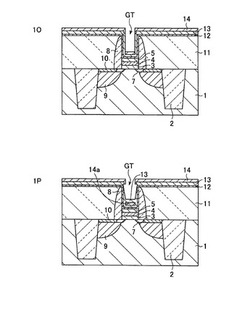

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極中の不純物がゲート絶縁膜を突き抜けてチャネル領域に拡

散するのを抑制し、ソース・ドレイン領域の不純物イオンが部分的にチャネル領

域方向に異常拡散するのを防ぐ。

【解決手段】ゲート絶縁膜3上に、ポリシリコン膜4を被着してゲート電極5

パターンにパターンニングした後、ソース・ドレイン領域9を形成する前に、窒

素を含む雰囲気中で窒化処理を行って、ゲート電極5端部付近のゲート絶縁膜3

中に新たに窒素を導入する。または、ゲート電極5のパターンニング後、ソース

・ドレイン領域9を形成する前に、酸化処理を行うことによってゲート電極5の

パターンニングの際に生じるダメージや汚染の一部を酸化膜中に取り込んで基板

から除去する。その後、窒化処理を行うことにより、酸化処理によってゲート電

極5端部付近に形成され、ダメージを含む酸化膜に積極的に窒素を導入する。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

半導体デバイスの形成方法及びエッチング・マスク

【課題】 フィン型FETデバイス及びこれの製造方法を提供する。

【解決手段】 半導体デバイスは、基板を準備しそして基板上に半導体含有層を形成することにより形成される。次いで、複数個の開口を有するマスクが、半導体含有層上に形成され、ここでマスクの複数個の開口のうち互いに隣接する開口は、最小構造寸法だけ離されている。その後、半導体含有層の第1部分にドーパントを導入するために、角度付けしたイオン注入が行われ、ここでドーパントがほぼ存在しない残りの部分がマスクの下側に存在する。サブリソグラフィック寸法のパターンを形成するために、半導体含有層のうちドーパントを含む第1部分がこの半導体層のうちドーパントをほぼ含まない残りの部分に対して選択的に除去され、そしてサブリソグラフィック寸法のフィン構造を生じるために、パターンが基板に転写される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置、およびその製造方法

【課題】フィン内に形成されるチャネル領域に効果的に歪みを発生させて、チャネル領域内の電荷移動度を向上させたフィン型トランジスタを有する半導体装置、およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、半導体基板上に、フィンおよび前記フィンの上と下の少なくともいずれかに位置する所定の膜を形成する工程と、ゲート絶縁膜を介して前記フィンの両側面を挟むようにゲート電極を形成する工程と、前記所定の膜を膨張または収縮させ、前記フィンの前記ゲート電極に挟まれた領域に位置するチャネル領域に前記フィンの高さ方向の歪みを与える工程と、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 ゲート電極とドレイン領域間のリーク電流の増加を抑制する。

【解決手段】 半導体基板上にゲート酸化膜を介してゲート電極を形成する工程と、ゲート電極に第1の不純物を注入し、ゲート電極をマスクとして半導体基板に第1の不純物を注入する第1の不純物注入工程と、第1の不純物を活性化させる第1の熱処理を行う工程と、ゲート電極のゲート絶縁膜から離間させた位置に第2の不純物を注入する第2の不純物注入工程と、第2の不純物を含有する領域を活性化する形成する第2の熱処置を行う工程と、を含み、第1の不純物はリンからなる。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの性能向上を図ってスペーサを形成できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲートを覆って、半導体基板上に、高誘電体材料を含むバリア絶縁膜を形成する工程と、バリア絶縁膜上に、スペーサ絶縁膜を形成する工程と、スペーサ絶縁膜を、異方性エッチングして、ゲートの側壁上にスペーサを残して除去する工程と、露出したバリア絶縁膜を除去する工程と、ゲート及びスペーサをマスクとして、半導体基板に不純物を注入し、エクステンションを形成する工程と、さらにサイドウォールを形成し、ゲート、スペーサ、及びサイドウォールをマスクとして、ソース/ドレイン領域を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、EOTの増膜が抑制され、且つ、良好な品質を有する高誘電率膜を備えた信頼性の高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1内に形成された第1導電型の第1の領域3及び第2導電型の第2の領域4と、半導体基板1上であって、第1の領域3及び第2の領域4の上に形成されたゲート絶縁膜5と、ゲート絶縁膜5上に形成された保護膜6と、保護膜6のうち第1の領域3の上に設けられた部分上に形成され、金属からなる第1のゲート電極9と、保護膜6のうち第2の領域4の上に設けられた部分上に形成された第2のゲート電極12とを備えている。ゲート絶縁膜5及び保護膜6は、高誘電率膜からなる。

(もっと読む)

半導体集積回路装置

【課題】基板とゲート絶縁膜との界面近傍における窒素濃度を必要以上に高くすることなく、ゲート絶縁膜中の窒素濃度を高める。

【解決手段】電界効果トランジスタのゲート絶縁膜は、半導体基板に近い第1領域と、第1領域よりもゲート電極に近い第2領域とで窒素濃度のピークが異なっており、第1領域における窒素濃度のピークは、2.5atomic%〜10atomic%であり、第2領域における窒素濃度のピークは、第1領域における窒素濃度のピークよりも高い。

(もっと読む)

酸窒化処理装置及び方法、並びに半導体装置の製造方法

【課題】NOガスを処理ガスとして用いた酸窒化処理を行うに際して、当該酸窒化処理により所望の膜厚及び窒素濃度のシリコン酸窒化膜を得る。

【解決手段】酸窒化処理を行うに際して、処理ガスの不純物濃度を計測し、生成される酸窒化膜の膜厚又は酸窒化膜の窒素濃度が所定範囲内の値となるように、計測された不純物濃度に応じて当該酸窒化処理を行う。ここで、詳細には、処理ガス中の不純物濃度と膜厚又は窒素濃度との相関関係を予め計測し規定しておく。そして、当該相関関係に基づき、膜厚又は窒素濃度が所定範囲内の値となるように、計測された不純物濃度に応じて、具体的には酸窒化処理における処理圧力を調節設定して当該処理を行う。

(もっと読む)

半導体装置、およびその製造方法

【課題】表面にエクステンション層を形成したフィンを有し、十分に寄生抵抗を低減することのできる半導体装置、およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成されたフィンと、ゲート絶縁膜を介して前記フィンの両側面を挟むように形成されたゲート電極と、前記ゲート電極の両側の前記フィンの側面に形成され、前記半導体基板の表面と鋭角に対向する面を有するエクステンション層と、前記半導体基板の表面と鋭角に対向する前記面の表面に形成されたシリサイド層と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】チャネル領域に応力を与えるため、ソース・ドレイン・コンタクト領域に形成されるシリサイド膜がシリコン基板側に突出することを防ぎ、接合リーク不良の発生やゲートリーク不良の発生を回避する半導体装置の製造方法及び製造された半導体装置の提供。

【解決手段】シリコンを含む半導体基板101と、前記半導体基板101中に形成された素子分離絶縁膜102によって区画された半導体領域と、前記半導体領域にゲート絶縁膜103を介して形成されたゲート電極と、前記半導体領域に形成された第1の拡散層107と、前記ゲート電極及び前記第1の拡散層107と前記素子分離絶縁膜102の間に形成されたシリコンゲルマニウム領域113と、前記SiGe領域113上に形成されたシリサイド膜114を含み、前記SiGe領域113は、前記ゲート電極又は前記素子分離絶縁膜102に近接した部分で最も厚いことを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧の変動などに代表される素子特性の劣化を抑制しながら微細化を図ることができる半導体装置およびその製造技術を提供する。

【解決手段】ソース領域あるいはドレイン領域を構成する不純物拡散領域であって、ゲート電極Gに整合して形成されたn+型半導体領域NR1をMISFETのチャネル領域よりも上部に形成し、かつ、n+型半導体領域NR1のうちチャネル領域に隣接する隣接領域の深さをチャネル領域の底部と同等になるように構成する。さらに、n+型半導体領域NR1の不純物拡散を抑制するためにn+型半導体領域NR1に接触するように形成されるp型半導体領域PRを、チャネル領域へ入り込まないように構成して、n+型半導体領域NR1とチャネル領域がp型半導体領域PRを介さず直接接触するようにする。

(もっと読む)

縦型スピントランジスタ及びその製造方法

【課題】トランジスタ及びその製造方法に関して、新たな構造のスピントランジスタ及びその製造方法を提案すること。

【解決手段】磁性体で形成された層を含んでいる第1のソースドレイン層と;前記第1のソースドレイン層上に形成されており、半導体で形成された層を含んでいる、チャネル層と、前記チャネル層上に形成されており、磁性体で形成された層を含んでいる、第2のソースドレイン層と、を含む突起構造と;前記チャネル層の側面に形成されたゲート絶縁膜と;前記ゲート絶縁膜の表面に形成されたゲート電極と;を具備することを特徴とする縦型スピントランジスタ。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】浅いソース、ドレイン接合位置を保ちつつ、ソース、ドレインがシリサイド化され、かつ、接合リークが低く抑えられた半導体装置の製造方法および半導体装置を提供する。

【解決手段】MISFET(金属絶縁物半導体電界効果トランジスタ)を有する半導体装置の製造方法であって、シリコン基板1100の表面に、このMISFETのゲート絶縁膜を形成し、このゲート絶縁膜上にゲート電極を形成し、このゲート電極の両側に、{110}面方位を有するシリコン面上に設けられ、このシリコン面上の<100>方向に垂直な長辺と、この<100>方向に平行で幅が0.5μm以下の短辺からなる矩形状を呈し、MISFETのソース、ドレイン領域の一部を構成する複数のニッケルシリサイド(NiSi)領域501a、502aを形成する。

(もっと読む)

1 - 20 / 55

[ Back to top ]