Fターム[5F140BF00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255)

Fターム[5F140BF00]の下位に属するFターム

単層 (2,376)

最下層材料 (6,467)

2層 (1,957)

2層目材料 (3,048)

3層 (490)

4層以上 (153)

3層目より上層の材料 (915)

構造、不純物の状態 (690)

複数種類を用い単純多層でないもの (119)

形状、配置 (2,388)

マスク性能の向上(プロセス時を含む) (49)

ゲート電極への配線コンタクト構造 (591)

Fターム[5F140BF00]に分類される特許

1 - 12 / 12

化合物半導体装置及びその製造方法

【課題】特性の低下を抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、が含まれている。p型半導体層8に含まれるp型不純物として、少なくとも電子走行層3及び電子供給層5のいずれかを構成する元素と同種の元素が用いられている。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子サイズの拡大を伴うことなくゲート−ドレイン間(又はゲートソース間)耐圧を確保できる半導体装置とその製造方法を提供する。

【解決手段】基板表面のドレイン側又はソース側の少なくとも一方にLOCOS膜を形成する工程と、基板表面に、LOCOS膜に接続されたゲート酸化膜を形成する工程と、ゲート酸化膜とLOCOS膜を覆う導電膜の形成工程と、導電膜の端部がLOCOS膜の上に位置するように導電膜をエッチングするゲート電極の形成工程と、ゲート電極の端部とエッチング端面が揃うようにLOCOS膜とゲート酸化膜をエッチングして、基板表面のLOCOS膜を除去した部分に凹部を形成する工程と、ゲート電極の側壁を覆い、その底面が凹部の底面と接するようにサイドウォールスペーサを形成する工程と、基板表面のゲート電極とサイドウォールスペーサを挟む位置に不純物を添加して、ドレイン及びソース領域の形成工程と、を含む。

(もっと読む)

半導体素子

【課題】より大きな電流ノイズを容易に発生させることが可能な半導体素子を提供する。

【解決手段】本発明に係る半導体素子100は、所定の物質により形成されるゲート電極101と、ゲート電極の少なくとも一部を覆うように所定の誘電体を用いて形成されるゲート絶縁膜103と、ゲート絶縁膜上に不純物及び/又は欠陥によるトラップを有する化合物を用いて形成されるチャネル形成領域105と、チャネル形成領域の端部に形成されるソース107/ドレイン109と、を備え、チャネル形成領域の幅は、不純物及び/又は欠陥によるトラップを有する化合物のデバイ長とする。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数の増加や前後のプロセスへの影響を抑えて、n型MOS−FET、p型MOS−FETのそれぞれに適する応力を付与することが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体基板wと、半導体基板wに形成されたソース領域12aおよびドレイン領域13aと、半導体基板w上のソース領域12a、ドレイン領域13a間に形成されたゲート電極16と、半導体基板wおよびゲート電極16上に形成された層間膜18と、層間膜18に埋め込み形成され、引張または圧縮応力を有する金属または金属化合物を含む膜22a、22bを有し、半導体基板wおよびゲート電極16と離間するように形成されたダミーフローティングパターン22を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

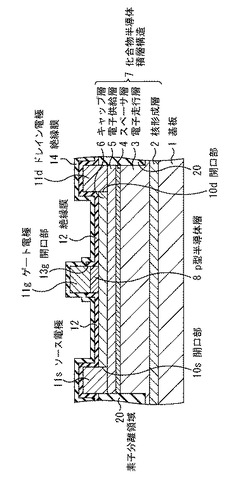

【課題】超短チャネル長化でき、Si層厚一定によって閾値を変化させずにON電流を増加でき、さらにバックゲートにより閾値も動的に変更できる縦型トランジスタ構造を備えた半導体装置および半導体装置の製造方法を提供することを目的とする。

【解決手段】基板2上に、中心軸Mが基板2面と垂直方向に形成されてなる筒型の基柱3と、基柱3の上部と下部に、中心軸Mを中心とする同心形状に形成された第1導電型からなるソース・ドレイン拡散層4a,4bと、ソース・ドレイン拡散層4a,4bに挟まれた基柱3の中間部に形成された第1導電型からなるボディ層と、基柱3の側面にゲート絶縁膜6を介して形成されたフロントゲート電極7とを備えたことを特徴とする。また、第2導電型からなるバックゲート電極8が、基柱3の内側に上部から下部まで貫通する柱状に形成されてなることとする。

(もっと読む)

半導体装置及びその製造方法

【課題】フィールド・プレート電極下の絶縁膜における電界集中を抑制することを課題とする。

【解決手段】本発明は、フィールド・プレート電極下の絶縁膜の端部形状を緩やかにしている。例えば、本発明に係る半導体装置は、半導体基板と;前記半導体基板上に形成されたゲート絶縁膜と;前記半導体基板上に形成された保護絶縁膜と;前記ゲート絶縁膜上に形成されたゲート電極と;前記保護絶縁膜上に形成され、前記ゲート電極と同電位のフィールド・プレート電極とを備える。そして、前記保護絶縁膜は、前記半導体基板の表面に形成され、当該基板内側には形成しない構造を採用する。

(もっと読む)

半導体構造

【課題】BTS試験の影響のない半導体構造を有する高電圧MOS素子を提供する。

【解決手段】高電圧MOS素子は、基板上に横たわった第1高電圧ウェル(HVW)領域24と、基板上に横たわった第2HVW領域26と、基板上に横たわり、第1・第2HVW領域の導電型とは反対の導電型となり、かつ、少なくとも一部が第1HVW領域と第2HVW領域との間に設けられる第3HVW領域28と、第1・第2・第3HVW領域の中に設けられた絶縁領域30と、第1HVW領域から第2HVW領域まで覆いかつ延伸するゲート誘電体と、ゲート誘電体上に設けられたゲート電極38と、絶縁領域上に設けられ、前記ゲート電極から電気的に絶縁された遮蔽パターン42と、を備える。ゲート電極と遮蔽パターンとの間隔は、好ましくは約0.4μm未満である。遮蔽パターンは、好ましくはゲート電極に印加されるストレス電圧よりも低い電圧に接続される。

(もっと読む)

半導体構造およびその製作方法(チャネルの応力向上のための低ヤング率スペーサ)

【課題】チャネル領域を有する半導体基板を使用する半導体構造およびその製作方法を提供すること。

【解決手段】ゲート電極が、半導体基板上に配置される。スペーサが、ゲート電極の側壁に隣接して配置される。このスペーサは、約10〜約50GPaのモジュラスを有する材料で形成される。このモジュラスは、チャネル領域内に向上した応力をもたらす。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長が100nm以下であってもオフリーク電流を十分に抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】N型ウェル並びにゲート絶縁膜32及びゲート電極33が形成された半導体基板31に対し、リンをイオン注入することにより、半導体基板31の表面にN型ポケット層34を形成する。ゲート電極33の長さ(ゲート長)は、100nm以下である。イオン注入は、4方向からの斜めイオン注入により行う。また、例えば、注入エネルギを15乃至30keVとし、ドーズ量を1方向当たり3×1012乃至1.5×1013cm-2とする。この方法によれば、N型ポケット層34の形成にあたり、リンのイオン注入を行っているので、ゲート長を100nm以下と短くしても、チャネル近傍に強い電界が発生することを抑制することができる。このため、BD間リーク電流を抑制して、オフリーク電流を低減することが可能である。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の閾値電圧を制御する。

【解決手段】 nMOS形成領域とpMOS形成領域にマスク9を形成した後、pMOS形成領域にあるマスク9を除去し、nMOS形成領域とpMOS形成領域に所定量の金属11を堆積して、pMOS形成領域のゲート電極3bをフルシリサイド化する。そして、これと同様の手順でnMOS形成領域のゲート電極3aを所定量の金属でフルシリサイド化する。堆積する金属の量によって各ゲート電極3a,3bのシリサイド組成をそれぞれ制御することができるため、各トランジスタについて最適な閾値電圧を得ることが可能になる。

(もっと読む)

1 - 12 / 12

[ Back to top ]