Fターム[5F140BF10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 最下層材料 (6,467) | 金属 (3,194) | 金属化合物(窒化物、酸化物) (807)

Fターム[5F140BF10]に分類される特許

1 - 20 / 807

半導体装置の製造方法

半導体装置の製造方法

化合物半導体装置及びその製造方法

電界効果トランジスタ

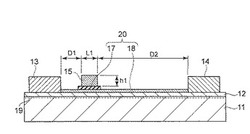

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置の製造方法

【課題】縦型トランジスタのソース又はドレイン用の拡散層を形成するにあたって形成されるシリコン膜に表面凹凸を発生させない半導体装置の製造方法を提供する。

【解決手段】複数の半導体ピラーを形成する工程と、隣り合う前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程と、前記絶縁膜の前記溝の底部に近い領域に側面開口を形成する工程と、前記溝の内部を覆うようにシリコン膜からなる被覆膜を形成する工程と、前記被覆膜上に前記半導体ピラー内へ拡散させる不純物で構成された不純物層を形成する工程と、前記不純物を、前記側面開口を塞ぐように形成されている前記被覆膜を通して前記半導体ピラー内に熱拡散させてソース又はドレイン用の拡散層を形成する工程と、を含む。前記被覆膜の成膜温度を510℃より高く度550℃未満の範囲とすることにより、非晶質状態のシリコン膜を形成する。

(もっと読む)

半導体装置

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法

【課題】しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

トンネルトランジスタ、トランジスタを含む論理ゲート、論理ゲートを使用するスタティックランダムアクセスメモリ、およびトンネルトランジスタの製造方法

【課題】第1、第2ゲートを有するトンネルトランジスタで、第1、第2のゲート間の電圧の差がより小さい場合にしようできるトンネルトランジスタを提供する。

【解決手段】ドレイン2、ソース4およびドレイン2とソース4との間で電流を制御するための少なくとも第1ゲート6とを含み、第1および第2のゲート誘電体材料7、11の第1側9、13が、それぞれ第1および第2の半導体部分14、15に実質的に沿って、実質的に接続して配置されたトンネルトランジスタ1。

(もっと読む)

半導体装置の製造方法

【課題】注入した導電性不純物により形成される結晶欠陥の密度を低減し、歩留まり率が向上するような半導体装置の製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板を加熱することにより、半導体基板の基板温度を200から500℃の間の所望の温度に維持すると同時に、半導体基板に導電性不純物をイオン注入法もしくはプラズマドーピング法を用いてドーピングし、ドーピングした導電性不純物を活性化させるための活性化処理を行う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、オン抵抗を低くしつつ、閾値電圧を高くする。

【解決手段】キャップ層400と障壁層300の界面、及びチャネル層200とバッファ層100の界面には圧縮歪が生じており、障壁層300とチャネル層200の界面には引張り歪が生じている。このため、キャップ層400と障壁層300の界面、並びにチャネル層200とバッファ層100の界面において、負の電荷が正の電荷よりも多くなっており、障壁層300とチャネル層200の界面において、正の電荷が負の電荷よりも多くなっている。チャネル層200は、第1層、第2層、及び第3層の積層構造を有している。第2層は、第1層及び第3層よりも電子親和力が大きい。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】製造コストの低減、およびプロセス時間の短縮を可能とするfinFETの製造方法を提供する。

【解決手段】finFETは、ソース領域、ドレイン領域、およびソース領域とドレイン領域との間のチャネル領域を有するフィンを備えるように形成される。上記フィンは、半導体ウエハ上でエッチングされる。ゲートスタックは、上記チャネル領域に直接接触する絶縁層と、上記絶縁層に直接接触する導電性のゲート材料とを有するように形成される。上記ソース領域および上記ドレイン領域は、上記フィンの第一領域を露出するためにエッチングされる。次に、上記第一領域の一部が、ドーパントでドーピングされる。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】EOTの低減及びリーク電流の低減を両立できる半導体装置の製造方法を提供すること。

【解決手段】被処理体上に第1の高誘電率絶縁膜を成膜する第1の成膜工程と、前記第1の高誘電率絶縁膜を、650℃以上で60秒未満の間熱処理する結晶化熱処理工程と、前記第1の高誘電率絶縁膜上に、前記第1の高誘電率絶縁膜の金属元素のイオン半径よりも小さいイオン半径を有する金属元素を有し、前記第1の高誘電率絶縁膜よりも比誘電率が大きい、第2の高誘電率絶縁膜を成膜する第2の成膜工程と、を含む、半導体装置の製造方法。

(もっと読む)

1 - 20 / 807

[ Back to top ]