Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

201 - 220 / 411

半導体装置及びその製造方法

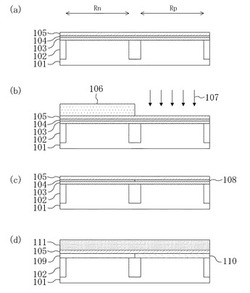

【課題】STI幅の増加や信頼性の低下を招くことなく、所定の導電型トランジスタ領域において最適なHigh-kゲート絶縁膜を実現する。

【解決手段】N型トランジスタ領域RnとP型トランジスタ領域Rpとを含む半導体基板101上の全面にHigh-k絶縁膜103、N型トランジスタ用キャップ膜104及び金属含有膜105を順次堆積する。P型トランジスタ領域Rpに位置するN型トランジスタ用キャップ膜104にイオン107を導入することにより、P型トランジスタ用キャップ膜108を形成する。金属含有膜105上にポリシリコン膜111を堆積した後、パターニングにより、N型トランジスタ用ゲート電極113及びP型トランジスタ用ゲート電極114を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】Hf及びZrの少なくともいずれかを含むゲート絶縁膜の膜質を安定させることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、半導体層と、半導体層の上に設けられ、Hf及びZrの少なくともいずれかを含むゲート絶縁膜と、ゲート絶縁膜の上に設けられ、Hf及びZrの少なくともいずれかを含む炭窒化物を含むゲート電極と、を備えている。

(もっと読む)

成膜装置及び成膜方法

【課題】 ドーパントの活性化率の高いシリコンゲルマニウム膜を成膜するにあたり、シリコンゲルマニウム膜のマイグレーションを抑えること。

【解決手段】 反応容器内に処理ガスを供給すると共に処理雰囲気の温度を所定の温度に設定して基板上にシリコンゲルマニウム膜を成膜する工程(P4)と、次いで反応容器内に水素ガスを供給してシリコンゲルマニウム膜をアニールする工程(P5)と、その後、反応容器内を真空排気し続いてパージガスによりパージする工程を1回行うかまたは複数回繰り返す工程(P6)と、しかる後に基板を反応容器内から搬出する工程(P7)と、を含む。

(もっと読む)

半導体加工方法

【課題】high−k膜/メタルゲート構造を有する半導体素子のドライエッチングにおいて、メタルゲート部分を垂直にエッチングする。

【解決手段】減圧処理室204と、該減圧処理室に処理ガスを供給するガス供給手段と、前記減圧処理室内に、半導体基板を載置して保持する試料台205と、前記減圧処理室に供給された処理ガスに高周波エネルギを供給してプラズマを生成するプラズマ生成手段を備え、生成したプラズマにより前記半導体基板にプラズマエッチング処理を施す半導体加工方法において、前記試料台上に、HfあるいはZrを含む高誘電率絶縁膜、TiあるいはTaを含む仕事関数制御金属導体膜、およびレジストを順次形成した半導体基板206を載置し、前記レジストを用いて前記導体膜をエッチング加工するに際して、前記試料台にオンオフ変調された基板バイアス電圧を印加する。

(もっと読む)

半導体装置の製造方法

【課題】仕事関数金属膜と低抵抗膜とで構成されたゲート電極をプラズマエッチングする際に、膜質に応じたエッチングステップの切り替えの遅延を防ぐ。

【解決手段】低抵抗膜6中であって、仕事関数金属膜4との界面の近傍に、プラズマ発光モニタに感度のある、窒素を含む進捗モニタ層5を設けることで、エッチング中のプラズマ発光の変化を検知し、エッチングの進捗をモニタすることでエッチングステップ切り替えの遅延を防止することができる。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】短チャネル効果を抑制すると共に、MISトランジスタの駆動能力が劣化することを防止するMIS(Metal Inserted Semiconductor)トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10における活性領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第1の導電膜14、及び該第1の導電膜14上に形成された第2の導電膜15からなるゲート電極15Aと、活性領域10xにおける第2導電膜15の側方下に形成されたエクステンション領域16と、第1の導電膜14上に、第2の導電膜15の側面と接して形成された第1のサイドウォール17とを備え、第1の導電膜14のゲート長方向の長さは、第2の導電膜15のゲート長方向の長さよりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】高速動作が可能なMIPS構造を持つメタルゲートを含む半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜3と、該ゲート絶縁膜3の上に順次形成され、TiN膜4とポリシリコン膜5とにより構成されたゲート電極20の第2のゲート電極部20bと、半導体基板1の上にゲート電極20を覆うように形成された層間絶縁膜8とを有している。層間絶縁膜8及びポリシリコン膜5を貫通して形成されたコンタクト9は、TiN膜4と直接に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】

歪み技術を用いたMOSトランジスタにおいて、リーク電流を抑える。

【解決手段】

半導体装置は、第1の格子定数を有する第1の半導体で形成された半導体基板に形成され、活性領域を画定する素子分離領域と、活性領域の中間位置を横断して、半導体基板上方にゲート絶縁膜を介して形成されたゲート電極と、ゲート電極側壁上に形成されたサイドウォールスペーサとを含むゲート電極構造と、ゲート電極構造両側の活性領域と素子分離領域との界面が半導体基板の表面に表出した境界の一部を覆って半導体基板の表面上方に配置された他のゲート電極構造であって、他のゲート電極と該他のゲート電極の側壁上に形成された他のサイドウォールスペーサとを含む他のゲート電極構造と、ゲート電極構造と他のゲート電極構造の間の活性領域をエッチして形成されたリセスと、リセスを埋めてエピタキシャル成長され、第1の格子定数と異なる第2の格子定数を有する第2の半導体で形成された半導体層と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜13aと、下層導電膜15aと第1の導電膜18aと第1のシリコン膜19aとを有する第1のゲート電極30aとを備えた第1導電型の第1のトランジスタが形成されている。半導体基板10の第2の活性領域10b上には、高誘電体材料と第2の金属とを含有する第2のゲート絶縁膜13bと、第1の導電膜18aと同一の材料からなる第2の導電膜18bと第2のシリコン膜19bとを有する第2のゲート電極30bとを備えた第2導電型の第2のトランジスタが形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極である金属膜/多結晶シリコン膜間の接触抵抗が大きい場合であっても、ゲートコンタクトプラグに印加した電界を十分な速度で十分に金属膜に伝えることができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置は、半導体基板1と、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成された金属膜4、当該金属膜4上に形成された多結晶シリコン膜5、を有するゲート電極6と、ゲート電極6上に形成された層間絶縁膜11と、層間絶縁膜11および多結晶シリコン膜5を貫通して金属膜4と接触するように形成されたコンタクトプラグ12と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜2上にアモルファスシリコン膜3を形成する工程と、前記アモルファスシリコン膜3に不純物イオン4をイオン注入する工程と、前記アモルファスシリコン膜3を加工することにより、前記ゲート絶縁膜2上にゲート電極3aを形成する工程と、を具備することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】ゲート電極の構造が異なる2種類のトランジスタを形成する際のゲート絶縁膜の突き抜け及び基板掘れが生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11と、半導体基板11の第1の領域13に形成された第1のトランジスタ20と、第2の領域14に形成された第2のトランジスタ30とを備えている。第1のトランジスタ20は、第1のゲート絶縁膜21と、第1のゲート電極22とを有し、第2のトランジスタ30は、第2のゲート絶縁膜31と、第2のゲート電極32とを有している。第1のゲート絶縁膜21及び第2のゲート絶縁膜22は、第1の絶縁膜41と第2の絶縁膜42とを含む。第1のゲート電極22に含まれる元素と、第2のゲート電極32に含まれる元素とは少なくとも一部が異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率絶縁膜を含むゲート絶縁膜を備えた電界効果型トランジスタにおいてゲート絶縁膜におけるゲート電極の端部下に位置する部分の厚膜化を試みると、高誘電率絶縁膜が結晶化し、ゲートトンネルリーク電流の発生を抑制出来ない場合があった。

【解決手段】半導体装置では、半導体基板1上にはゲート絶縁膜2が形成され、ゲート絶縁膜2上にはゲート電極3が形成されている。ゲート絶縁膜2では、ゲート絶縁膜2におけるゲート電極3の両端部下に位置する厚膜部分2aの膜厚は、ゲート絶縁膜2におけるゲート電極3の中央部下に位置する中央部分2bの膜厚よりも厚い。

(もっと読む)

半導体装置及びその製造方法

【課題】 空乏化が抑制されたゲート電極を備え、特性のばらつきが小さく十分な駆動能力を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1における活性領域1a上に形成された第1のゲート絶縁膜5aと、第1のゲート絶縁膜5a上に形成され、第1導電型の不純物を含む多結晶シリコン膜からなる第1のゲート電極6aとを備えている。第1のゲート電極6aに含まれる第1導電型の不純物は、第1のゲート電極6aにおける第1のゲート絶縁膜5aとの界面部分に第1の濃度ピークを有し、且つ、第1のゲート電極6aの上面部分に第2の濃度ピークを有し、第1の濃度ピークは、第2の濃度ピークよりも濃度が大きい。

(もっと読む)

半導体装置

【課題】メモリセルに対して設けられる選択ゲートについて、この選択ゲートのゲート長を長くすることなく、選択ゲートの制御性を向上させる。

【解決手段】本発明の一態様において、メモリセルA1に対して設けられる選択ゲートS1を含む半導体装置は、選択ゲートS1のチャネル上に形成されているゲート絶縁膜9の上面が、選択ゲートS1の素子分離領域10の上面の一部又は全部よりも高く、Tri-gate構造を持つ。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート誘電膜を用いるpチャネルFETをゲート先作りプロセスにより形成すると閾値が大きくなる。

【解決手段】High-Kゲート誘電膜104の側面と接触するようにHigh-K誘電膜102を形成した後、酸素雰囲気中でアニールする。

(もっと読む)

半導体装置の製造方法

【課題】 製造プロセスが比較的容易で、かつMOSFETの特性のばらつきを抑えることができる半導体装置の製造方法を提供する。

【解決手段】 Si基板1上に、界面酸化膜5,5a、ゲート絶縁膜6、金属ゲート電極7およびポリシリコンゲート電極8を順次形成してパターニングし、側面にシリコン酸化膜10を形成し、さらにサイドウォール17を形成する。サイドウォール17をマスクとしてSiGe−p型S/D18a、n型S/D20およびp型S/D21を形成した後、サイドウォール17を除去し、露出したシリコン酸化膜10をマスクとして、エクステンション層12,14,25,27およびハロー層13,15,26,28を形成する。さらにシリコン酸化膜10を介して、金属ゲート電極7などの側面にサイドウォール33を形成した後、サイドウォール33をマスクとして、金属シリサイド35を形成する。

(もっと読む)

201 - 220 / 411

[ Back to top ]