Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

121 - 140 / 411

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、pチャネルトランジスタのチャネル領域には圧縮歪を、nチャネルトランジスタのチャネル領域には引っ張り歪をそれぞれ効果的に印加できる新しい歪技術を提供する。

【解決手段】pチャネルトランジスタ105のゲート電極は、引っ張り内部応力を持つpチャネルメタル電極110を有する。nチャネルトランジスタ106のゲート電極は、圧縮内部応力を持つnチャネルメタル電極116を有する。

(もっと読む)

誘電体膜、誘電体膜を用いた半導体装置の製造方法及び半導体製造装置

【課題】高誘電率を有する誘電体膜の製造方法を提供する。

【解決手段】薄いシリコン酸化膜を形成したSi基板上に、HfN/Hf積層膜を形成し、アニール処理によりHf、Si、O、Nの混合物からなる金属酸窒化物とする誘電体膜の製造する。(1)EOTの低減が可能であり、(2)リーク電流がJg=1.0E−1A/cm2以下に低減され、(3)固定電荷の発生によるヒステリシスが抑制され、(4)700℃以上の熱処理を行ってもEOTの増加が無く耐熱性に優れる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】容易に製造できる半導体装置を提供する。

【解決手段】半導体装置は、PMOSトランジスタのゲート電極1pの仕事関数値が、High-kゲート絶縁膜16(16a)、及び、High-kゲート絶縁膜16・酸化シリコン膜15界面へのAlの拡散により調整されており、NMOSトランジスタのゲート電極1nの仕事関数値が、High-kゲート絶縁膜16・金属ゲート膜19間に挿入された、数原子層程度のAl層18により調整されている構成を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISトランジスタとPMISトランジスタの閾値電圧を同時に低減できる半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板10に形成された第1の活性領域10a上に高誘電体を含む第1のゲート絶縁膜17aと、金属材料を含む第1のゲート電極18aとを形成し、基板10に形成された第2の活性領域10b上に高誘電体を含む第2のゲート絶縁膜17bと、金属材料を含む第2のゲート電極18bとを形成する工程と、第1のゲート絶縁膜17aの端部と第2のゲート絶縁膜17bの端部とに負の固定電荷を導入する工程と、第1のゲート絶縁膜17aの端部を除去する工程とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体絶縁膜及びメタルゲート電極を有する半導体装置において、高仕事関数を得ると共にNBTI信頼性劣化を低減する。

【解決手段】半導体装置100において、基板101上に、高誘電体ゲート絶縁膜109を介してメタルゲート電極110が形成されている。高誘電体ゲート絶縁膜109とメタルゲート電極110との界面におけるメタルゲート電極110の側に、ハロゲン元素が偏析している。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】高誘電率ゲート絶縁膜として機能するHf含有絶縁膜4a,4b上にメタルゲート電極であるゲート電極GE1,GE2が形成され、ゲート電極GE1,GE2は、金属膜7a,7b,7cの積層膜からなる金属膜7とその上のシリコン膜8との積層構造を有している。金属膜7の最下層の金属膜7aは、窒化チタン膜、窒化タンタル膜、窒化タングステン膜、炭化チタン膜、炭化タンタル膜または窒化タングステン膜からなり、金属膜7bは、ハフニウム膜、ジルコニウム膜またはアルミニウム膜からなり、金属膜7cは、金属膜7aと同種の材料からなる膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

半導体装置の製造方法

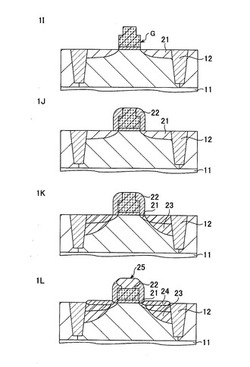

【課題】チャネルに大きな歪を生じさせることができ、制御を容易に行うことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、絶縁膜3、多結晶シリコン膜4及びアモルファスシリコン膜5を含む積層体を、ゲート電極の平面形状に形成する。多結晶シリコン膜4及びアモルファスシリコン膜5の側方にサイドウォール6を形成する。サイドウォール6をマスクとして半導体基板1の表面にp型不純物を導入して不純物導入領域7を形成する。サイドウォール6をマスクとして不純物導入領域7の表面に溝8を形成する。溝8内にSiGe層9を選択成長させる。アモルファスシリコン膜5を選択的に除去して、多結晶シリコン膜4を露出する。多結晶シリコン膜4上に導電層11を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を備えたCMISFETの性能を向上させる。

【解決手段】nチャネル型MISFETQnは、半導体基板1のp型ウエルPWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3aを介して形成されたゲート電極GE1を有し、pチャネル型MISFETQpは、n型ウエルNWの表面上に、ゲート絶縁膜として機能するHf含有絶縁膜3bを介して形成されたゲート電極GE2を有している。ゲート電極GE1,GE2は、金属膜7とその上のシリコン膜8との積層構造を有している。Hf含有絶縁膜3aは、Hfと希土類元素とSiとOとNとからなる絶縁材料膜またはHfと希土類元素とSiとOとからなる絶縁材料膜であり、Hf含有絶縁膜3bは、HfとAlとOとNとからなる絶縁材料膜またはHfとAlとOとからなる絶縁材料膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】High-k/metalゲート電極構造において各極性のFETに要求される仕事関数値を実現する。

【解決手段】第1の領域と第2の領域とを有する半導体基板101の上にゲート絶縁膜103を形成する。次に、ゲート絶縁膜103の上に第1の金属窒化膜105を堆積する。次に、第1の金属窒化膜105における第2の領域に位置する部分を除去することにより、ゲート絶縁膜103における第2の領域に位置する部分を露出させる。次に、ゲート絶縁膜103における第2の領域に位置する部分の上に、第1の金属窒化膜105と同じ金属窒化物からなる第2の金属窒化膜107を形成する。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:酸化ランタンまたは酸化ランタニド(例えば、Dy2O3、Pr2O3、Ce2O3)を含む層を準備する工程と;炭酸水である水溶液を供給することにより、酸化ランタンまたは酸化ランタニドを含む層を特定の領域で除去して、酸化ランタンまたは酸化ランタニドを含む層が上に蒸着された表面を露出させる工程とを備える方法が開示されている。

(もっと読む)

半導体装置及びその製造方法

【課題】導電型に応じて容易に構成を変えることが可能なFinトランジスタ及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に設けられた凸状の半導体からなるトランジスタ活性領域104と、トランジスタ活性領域104の一部の側面上及び上面上に設けられたゲート絶縁膜105aと、ゲート絶縁膜105aを間に挟んでトランジスタ活性領域104の側面及び上面の一部上に設けられたゲート電極350とを備えている。ゲート電極350のうち、トランジスタ活性領域104の側面上に設けられた部分の構成とトランジスタ活性領域104の上面上に設けられた部分の構成とは互いに異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜として高誘電体膜を使用すると、半導体装置の微細化を図ることができるが、半導体装置の性能低下を招来する場合があった。

【解決手段】半導体装置では、半導体基板101の上面上に、界面酸化層102、ゲート絶縁膜104及びゲート電極107が順に設けられている。ゲート絶縁膜104は、第1の高誘電体膜103と第2の高誘電体膜105とを有している。第1の高誘電体膜103は、界面酸化層102の上に設けられ、窒素を含有している。第2の高誘電体膜105は、第1の高誘電体膜103の上に設けられ、窒素を含有している。第1の高誘電体膜103における窒素濃度は、第2の高誘電体膜105における窒素濃度よりも低い。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極の酸化を抑制しつつ、MOSFETの寄生容量の増大を抑制する。

【解決手段】半導体装置は、半導体基板10と、前記半導体基板上に形成されたシリコンと酸素とを含む第1絶縁膜12aと、前記第1絶縁膜上に形成された前記第1絶縁膜よりも誘電率が高く、高融点金属と酸素とを主成分とする第2絶縁膜12bと、で構成されるゲート絶縁膜12と、前記ゲート絶縁膜上に形成された金属層13を含むゲート電極15と、前記ゲート電極の前記金属層の側面、および前記ゲート絶縁膜の前記第2絶縁膜の側面に形成されたシリコンと窒素を含む第1側壁絶縁膜16と、前記第1側壁絶縁膜の側面、および前記第1絶縁膜の前記第1絶縁膜の側面に形成されたシリコンと酸素とを含む第2側壁絶縁膜17と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

半導体装置の製造方法

【課題】ハーフピッチサイズが32nm以下のCMISデバイスを有する半導体装置において、nチャネル型電界効果トランジスタおよびpチャネル型電界効果トランジスタのそれぞれの閾値電圧を適切に設定することのできる技術を提供する。

【解決手段】pMIS形成領域に、主としてAlが拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜5ならびに下層メタルゲート電極6Dと上層メタルゲート電極6Uとの積層膜からなるメタルゲート電極6を有するpMIS100pを形成し、nMIS形成領域に、主としてLa(ランタン)が拡散した高誘電体膜5h(例えばHfO2膜)により構成されるゲート絶縁膜11ならびに上層メタルゲート電極6Uからなるメタルゲート電極12を有するnMIS100nを形成する。

(もっと読む)

121 - 140 / 411

[ Back to top ]