Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

141 - 160 / 411

半導体装置及びその製造方法

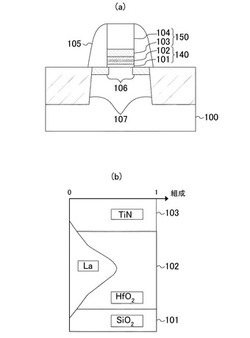

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含むチャネル形成領域を有する電界効果トランジスタにおいて、基板リーク電流を低減する。

【解決手段】半導体装置150は、Geを含む第1導電型の第1の半導体領域101と、第1の半導体領域101上にゲート絶縁膜121を介して形成されたゲート電極122と、第1の半導体領域101におけるゲート電極122の両側方に形成された第2導電型の拡散領域107と、第1の半導体領域101と拡散領域107との間に形成された第1導電型の第2の半導体領域108とを備える。第2の半導体領域108は、第1の半導体領域101におけるゲート電極122下方のチャネル形成領域よりも高い濃度のSiを含有する。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜及びメタルゲート電極を備えたCMISFETの生産性や性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有絶縁膜5を形成し、その上に窒化金属膜7を形成し、窒化金属膜7上のフォトレジストパターンをマスクにしたウェットエッチングによって、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aの窒化金属膜7を選択的に除去する。それから、希土類元素を含有するしきい値調整層8を形成し、熱処理を行って、nMIS形成領域1AのHf含有絶縁膜5をしきい値調整層8と反応させるが、pチャネル型MISFET形成予定領域であるpMIS形成領域1BのHf含有絶縁膜5は、窒化金属膜7があるためしきい値調整層8とは反応しない。その後、未反応のしきい値調整層8と窒化金属膜7を除去してから、nMIS形成領域1AとpMIS形成領域1Bにメタルゲート電極を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置全体としてみたとき、微細化によるチップ面積の減少を図りつつ、各素子に必要とされる特性を維持・向上させる。

【解決手段】半導体装置は、FinFET10と、FinFET10と同一のチップ上に設けられたPlanarFET20とを具備する。PlanarFETの第2ゲート絶縁層24は、FinFET10の第1ゲート絶縁層14よりも厚い。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのしきい値電圧制御のために使用する金属酸化膜の膜減り等に起因するしきい値電圧ばらつきを抑制し、所望のしきい値電圧を有するトランジスタを形成することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に、高融点金属酸化物を含む材料からなるゲート絶縁膜3が形成され、ゲート絶縁膜3上に金属酸化膜4が形成される。次いで、金属酸化膜4を構成する金属原子を、金属酸化膜4からゲート絶縁膜3の表面部へ拡散させる処理が実施される。当該金属原子の拡散工程後、上記金属酸化膜4がゲート絶縁膜3に対して選択的に除去される。そして、金属原子が拡散されたゲート絶縁膜3上に導電膜7、8が形成され、当該導電膜7、8を加工することでゲート電極30、31が形成される。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】(110)面を主面とする半導体基板に形成されたp型MISトランジスタを備えた半導体装置において、p型MISトランジスタのさらなる性能向上を図る。

【解決手段】半導体装置は、(110)面を主面とする半導体基板10に形成されたp型MISトランジスタPTrを備えた半導体装置である。p型MISトランジスタPTrは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され第1の金属膜14a及び第1の金属膜14a上に形成された第1のシリコン膜15aからなる第1のゲート電極14Aとを備えている。第1の金属膜14aは、膜厚が1nm以上であって且つ10nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】希土類含有複合酸化物膜の新規なエッチング方法を含む、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、希土類元素と、希土類でない他の金属元素と、Oとを含む希土類含有複合酸化物膜を形成する工程と、希土類含有複合酸化物膜に対し、フッ素を含まない酸によるエッチングと、他の金属元素の酸化物を溶解するフッ素含有溶液によるエッチングとを、交互に複数回行なうエッチング工程とを有する。

(もっと読む)

半導体装置

【課題】寿命を可及的に長くすることの可能なMISFETを備えた半導体装置を提供する。

【解決手段】半導体領域2が形成された半導体基板1と、半導体領域に離間して形成されたソース領域5aおよびドレイン領域5bと、ソース領域とドレイン領域との間の半導体領域3上に形成され金属および酸素を含む金属酸化層12を有するゲート絶縁膜10と、ゲート絶縁膜上に形成されたゲート電極16と、を有するMISFETを備え、金属酸化層に含まれる金属はHf、Zrのうちから選択された少なくとも1つであり、金属酸化層は、更にRu、Cr、Os、V、Fe、Tc、Nb、Taのうちから選択された少なくとも1つの元素が添加され、金属酸化層は元素が添加されたことにより形成される電荷を捕獲または放出する電荷トラップを有し、金属酸化層中における元素の密度は、1×1015cm−3以上、2.96×1020cm−3以下の範囲にあり、電荷トラップは、金属酸化層の中央より半導体領域側にピークを有するように分布することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

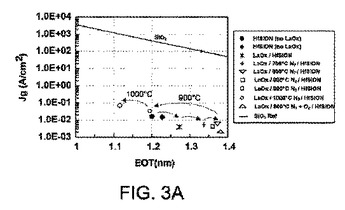

低減された等価酸化膜厚を有する高誘電率ゲートスタックの形成方法

低減された均等酸化物厚さ(EOT)を持つhigh−kゲートスタックを形成する方法を提供し、該方法は:シリコン含有基板を準備し;前記シリコン含有基板上に境界層を形成し、前記境界層が第一の等価酸化物厚さを有し;前記境界層上に第一のhigh−k膜を堆積し;前記第一のhigh−k膜及び前記境界層を、前記第一の等価酸化物厚さと等しいかそれより小さい第二の等価酸化物厚さを持つ変性境界層を形成する温度で熱処理し;及び前記変性境界層上に第二のhigh−k膜を堆積する方法である。ひとつの実施態様によると、前記第一のhigh−k膜がランタン酸化物を含み、前記第二のhigh−k膜がハフニウムシリケートを含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】半導体の酸化物を安定化させることができる上、欠陥密度が低くて電子移動度が高い誘電体層を得て、デバイスの信頼性及び性能を大幅に改善することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10内に設け、第1のゲルマニウムドープト領域を含む第1の電極と、第1の電極上に設け、半導体酸化物及び安定金属を含む第1の誘電体層23と、第1の誘電体層23上に設ける第2の電極とを備える。第1の電極及び第2の電極によりキャパシタを形成する。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成するときのハードマスクを除去するときにゲート絶縁膜の側面がエッチングされることを抑制し、かつ、サイドウォールの上端がゲート電極の上面より上に位置することを抑制する。

【解決手段】ゲート絶縁膜110上に、ゲート電極126となる導電膜120を形成する。次いで、導電膜120上に、ハードマスクパターン70を形成する。次いで、ハードマスクパターン70をマスクとして導電膜120を選択的に除去することにより、ゲート電極126を形成する。次いで、ゲート電極126の側面に第1のサイドウォール140を形成する。次いで、ハードマスクパターン70をウェットエッチングにより除去する。ハードマスクパターン70を形成した後、第1のサイドウォール140を形成する前に、ハードマスクパターン70の側面52を、上に行くにつれてハードマスクパターン70の幅が狭くなる方向に傾斜させる。

(もっと読む)

半導体装置

【課題】メタル電極/high−kゲート絶縁膜からなるゲート構造において、半導体特性や信頼性の劣化をおこさせることなく、サイドウォールを形成したゲート構造を有する半導体装置の提供。

【解決手段】半導体基板1上に設けられた、high−k誘電体材料からなるゲート絶縁膜2と、ゲート絶縁膜2の上に設けられたメタル電極3と、メタル電極3の側壁を覆い、ゲート絶縁膜2を挟んで半導体基板1と対向配置された酸化防止膜4と、ゲート絶縁膜2と酸化防止膜4とを覆うように、半導体基板上に設けられたサイドウォール5とを含むゲート構造。

(もっと読む)

半導体素子及びその製造方法

【課題】 加熱処理により、ランタンやアルミニウムがhigh−k材料とシリコン基板との間の酸化シリコン膜まで拡散する。ランタンやアルミニウムの拡散が、チャネル移動度の低下や素子の信頼性の低下の原因になる。

【解決手段】 半導体基板の一部の領域上に、SiとOとを含む絶縁層が形成されている。絶縁層の上に、ハフニウムシリケートを含む下側高誘電率膜が形成されている。下側高誘電率膜の上に、ハフニウム酸化物、またはHfとSiとの合計の原子数に対するHfの原子数の比が、下側高誘電率膜のそれよりも大きいハフニウムシリケートを含む上側高誘電率膜が形成されている。上側高誘電率膜の上にゲート電極が形成されている。ゲート電極の両側にソース及びドレインが配置されている。

(もっと読む)

半導体装置

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できようにする。

【解決手段】半導体装置は、素子分離領域102により分離された活性領域103を有する半導体基板101と、活性領域103の上に形成されたゲート絶縁膜111と、ゲート絶縁膜111の上に形成されたゲート電極121とを備えている。ゲート絶縁膜111は、シリコン及び酸素を除く第1の元素が拡散している。素子分離領域102は、第1の素子分離膜102Aと、第1の素子分離膜102Aよりもゲート絶縁膜111側に形成され且つ第1の素子分離膜102Aと比べて第1の元素が拡散しにくい第2の素子分離膜102Bとを有している。

(もっと読む)

半導体装置の製造方法

【課題】素子特性を劣化させることなく、しきい値電圧の低い、金属のゲート電極を有するPチャネルMOSトランジスタを備えた半導体装置を製造することを可能にする。

【解決手段】半導体領域2上にゲート絶縁膜5を形成するステップと、第1金属元素と、OH基、NOx(x=1,2)基のうち少なくとも一つを含有する酸素含有金属層6をゲート絶縁膜上に形成するステップと、酸素含有金属層上に第2金属元素を含むゲート電極膜7を形成するステップと、ゲート電極膜を形成した後、酸素含有金属層の熱分解反応或いは脱水反応が生じる温度以上に加熱するステップと、を備えている。

(もっと読む)

141 - 160 / 411

[ Back to top ]