Fターム[5F140BF27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層目より上層の材料 (915) | 金属 (751) | 高融点金属 (221)

Fターム[5F140BF27]に分類される特許

201 - 220 / 221

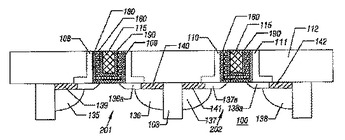

半導体装置の製造方法

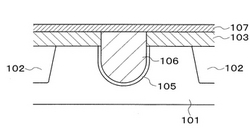

【課題】 特性の良好なトレンチゲート型トランジスタを有する半導体装置の製造方法を提供する。

【解決手段】 P型シリコン基板101上にシリコン窒化膜103を形成し、シリコン窒化膜103に所定のパターンの開口を形成し、シリコン窒化膜108をマスクとして用いて半導体基板101にゲートトレンチ104を形成した後、ゲートトレンチ104の内部および開口内にポリシリコン膜106を埋め込むことにより、ゲート電極を自己整合的に形成する。さらに、シリコン窒化膜103の全面にコバルトなどの高融点金属107をスパッタ法により堆積させた後、アニール処理を行い、さらに余剰金属を除去することにより、ポリシリコン膜106の表面にこれらの金属のシリサイド108を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたゲート電極をCo膜を用いてシリサイド化する場合であっても、ゲート電極の抵抗のばらつきを抑制しうる半導体装置及びその製造方法を提供する。

【解決手段】ゲート長Lgが50nm以下のゲート電極30上に、Co膜72を形成する工程と、熱処理を行うことにより、Co膜72とゲート電極30とを反応させ、ゲート電極30の上部にCoSi膜76aを形成する第1の熱処理工程と、Co膜72のうちの未反応の部分を選択的にエッチング除去する工程と、熱処理を行うことにより、CoSi膜76aとゲート電極30とを反応させ、ゲート電極30の上部にCoSi2膜42aを形成する第2の熱処理工程とを有し、第1の熱処理工程では、CoSi膜76aの幅wに対するCoSi膜76aの高さhの比h/wが0.7以下となるように、CoSi膜76aを形成する。

(もっと読む)

高誘電率ゲート誘電体および金属ゲート電極をもつ半導体デバイスの作成方法

半導体デバイスを作成する方法に関する。該方法は、基板上で二酸化ケイ素層に窒素を加えて窒化二酸化ケイ素層を形成することを含む。窒化二酸化ケイ素層の上に犠牲層を形成したのち、犠牲層が除去されて溝が生成される。窒化二酸化ケイ素層の上で溝の中に高誘電率ゲート誘電体層が形成され、該高誘電率ゲート誘電体層の上に金属ゲート電極が形成される。

(もっと読む)

(もっと読む)

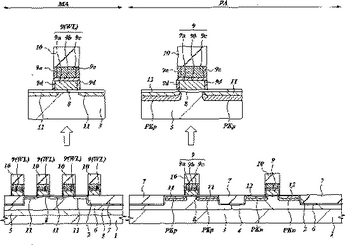

半導体集積回路装置およびその製造方法

ポリメタルゲートを構成する高融点金属膜の洗浄工程における欠けを防止し、装置の特性を向上させ、また、洗浄効率を向上させるため、基板1上の低抵抗多結晶シリコン膜9a、WN膜9bおよびW膜9cを、窒化シリコン膜10をマスクにドライエッチングし、これらの膜よりなるゲート電極9を形成し、ウエットハイドロゲン酸化により薄い酸化膜9dを形成した後、RPN法を用いて窒化処理を行い、ゲート電極の側壁から露出したW膜9cをWN膜9eとする。その結果、その後の洗浄工程、例えば、n−型半導体領域11やp−型半導体領域12の形成時に行われる、1)レジスト膜のホトリソグラフィー工程、2)不純物の注入工程、3)レジスト膜の除去工程および4)基板表面の洗浄工程が繰り返し行われても、W膜9cの欠けを防止でき、また、洗浄液としてU洗浄液やフッ酸系の洗浄液のような強い洗浄液を用いることができる。  (もっと読む)

(もっと読む)

半導体MOS装置及びCMOS装置、コンデンサ、及び製造方法

回路装置の作製方法を提供する。導電性にドープされたシリコンと誘電材との間に厚さ20Å以下(または70以下のALDサイクルで生じた厚さ)の金属含有材を形成する。導電性にドープされたシリコンとしてn型を用いることができ、誘電材は高k誘電材を用いることができる。金属含有材は誘電層上へ直接形成でき、導電性にドープされたシリコンは金属含有材上へ直接形成できる。回路装置はコンデンサ構造体あるいはトランジスタ構造体とすることができる。回路装置がトランジスタ構造体である場合はCMOS装置中へ組み入れることができる。本発明による種々装置はメモリ構造体中へ組み入れられる他、電子システムへも組み入れることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】フォトレジスト膜の除去の際の洗浄における半導体層上のシミのない半導体装置の製造方法を提供する。

【解決手段】露出している半導体層の表面部を酸化して、アッシング酸化膜17を形成した後、CVD酸化膜を堆積する。CVD酸化膜の上に形成したフォトレジスト膜9をマスクとする気相フッ酸処理により、アッシング酸化膜17は残したままでCVD酸化膜を部分的に除去し、非シリサイド領域Rnsを覆う反応防止用酸化膜18を形成する。フォトレジスト膜9を除去した後、アッシング酸化膜17を除去し、乾燥処理を行なった後、基板上に金属膜を堆積する。そして、半導体層と金属膜との反応により、高濃度ソース・ドレイン領域11などの半導体層の上部にシリサイド層12を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板上に形成されるトランジスタの導電型によらず、移動度を向上させる。

【解決手段】 半導体装置は、シリコン基板1上にPMOSトランジスタ2と、NMOSトランジスタ3とを備えている。いずれのトランジスタも、シリコン基板1上に形成されるゲート絶縁膜4と、このゲート絶縁膜4上に形成されるゲート電極5a,5bとを有する。ゲート電極5a,5bは例えばタングステン(W)で形成されている。PMOSトランジスタ2のゲート電極5aとNMOSトランジスタ3のゲート電極5bとに、互いに異なる応力を持たせる。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極上に形成するコンタクトホールの底面の金属膜の表面が酸化されるのを抑制する。

【解決手段】 基板上コンタクトホール19a、19bと、底面に金属膜7aを露出させたゲート電極上コンタクトホール19cとを形成した後、基板上コンタクトホール19a、19bの底面に露出したシリコン基板1にそれぞれ不純物を注入してN型イオン注入層21、P型イオン注入層23を形成する。その後、基板上コンタクトホール19a、19bおよびゲート電極上コンタクトホール19cが埋め込まれない膜厚で、これらのコンタクトホールの内面に金属酸化防止膜24を形成する。そして、熱処理により不純物を活性化させた後に、それぞれのコンタクトホールの底面の金属酸化防止膜24を除去する。

このように形成することにより、上記熱処理において金属膜7aの表面が酸化されるのを抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】

ポリメタル構造のゲート電極を有するMOSFET、特に、DRAMのメモリセルトランジスタの接合リークをよりいっそう低減する。

【解決手段】

半導体基板上に、ゲート絶縁膜、ポリシリコン膜、タングステンなどの高融点金属膜、ゲートキャップ絶縁膜を順次積層し、エッチングによりゲートキャップ絶縁膜および高融点金属膜を選択的に除去する。その後、ゲートキャップ絶縁膜、高融点金属膜及びポリシリコン膜の側面に、シリコン窒化膜及びシリコン酸化膜からなる2重の保護膜を形成し、これをマスクとして用いてポリシリコン膜をエッチングする。その後、ライト酸化処理を行って、ポリシリコン膜の側面にシリコン酸化膜を形成する。

(もっと読む)

半導体センシング用電界効果型トランジスタ及びこれを用いた半導体センシングデバイス

【解決手段】 シリコン上にゲート絶縁層が形成された半導体センシング用電界効果型トランジスタであり、該ゲート絶縁層上に、直接的な検出部として有機単分子膜を形成して用いる半導体センシングデバイス用の電界効果型トランジスタであって、上記ゲート絶縁層が、第1のシリコン酸化物層上にシリコン窒化物層を介して第2のシリコン酸化物層が積層されてなる積層構造を具備する半導体センシング用電界効果型トランジスタ及びこれを用いた半導体センシングデバイス。

【効果】 ゲート絶縁層からのトランジスタ部分への水分やイオンの侵入を遮断することが可能であり、液中測定用として特に好適な、高い検出感度を示す半導体センシングデバイス及びこれを与える電界効果型トランジスタを提供することができる。

(もっと読む)

半導体装置とその製造方法

【課題】シリコン窒化膜を堆積してもシート抵抗が上昇しない配線構造を提供する。

【解決手段】半導体基板上に第一の高融点金属膜5を形成する工程と、前記第一の高融点金属膜上に高融点金属窒化物の反応物7を持つ第二の高融点金属膜6Aを形成する工程と、前記第二の高融点金属膜上にシリコン窒化膜8を形成する工程とからなる。これにより、シリコン窒化膜の膜質を変化させることなく、また成膜時のパーティクルの発生を従来方法と同等としたまま、シリコン窒化膜下の高融点金属のシート抵抗の上昇を最小限に抑えることができる。

(もっと読む)

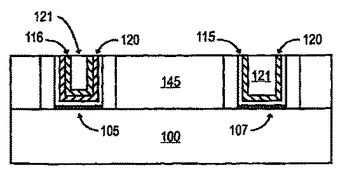

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

半導体装置

【課題】 低抵抗でゲート空乏化が起こらず、高温において安定であるとともに、仕事関数が制御されたゲート電極を有するCMISデバイスを提供する。

【解決手段】 素子分離領域を有する半導体基板と、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するp型MISトランジスタと、前記半導体基板に形成されたソース/ドレイン領域、前記半導体基板上に形成されたゲート絶縁膜、および前記ゲート絶縁膜上に形成されたゲート電極を有するn型MISトランジスタとを具備するCMISデバイスである。前記p型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に第1の金属を有し、前記n型MISトランジスタにおける前記ゲート電極は、少なくとも前記ゲート絶縁膜との界面に、前記第1の金属のホウ化物を有することを特徴とする。

(もっと読む)

タングステンシリサイド薄層の堆積とゲート金属の組込み

ゲート電極の層を堆積させる方法が提供される。その方法には、ドープされた多結晶シリコン層と、タングステンシリサイド薄層と、金属層とを堆積させるステップが含まれる。一態様においては、ドープされた多結晶シリコン層とタングステンシリサイド薄層は集積処理システム内に堆積される。他の態様においては、タングステンシリサイド層を堆積させるステップには、多結晶シリコン層をシリコン源に曝す工程と、タングステンシリサイド層を堆積させる工程と、タングステンシリサイド層をシリコン源に曝す工程とが含まれる (もっと読む)

PMOSを具備する半導体素子の形成方法

【課題】本発明はPMOSを具備する半導体素子を形成する方法を提供する。

【解決手段】前記方法によると、半導体基板の全面上にポリシリコン膜を形成する。前記ポリシリコン膜にP型不純物をドーピングする。熱処理工程を進行する。そして、前記P型不純物がドーピングされたポリシリコン膜の上部を第1厚さだけ除去する。これによって、漏洩電流を防止して、素子の速度を向上させることができるPMOSを具備する半導体素子を形成することができる。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

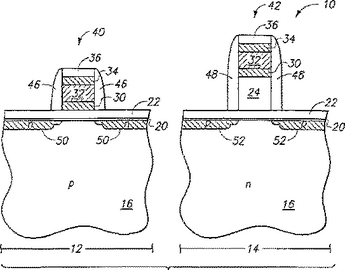

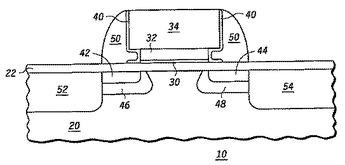

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

201 - 220 / 221

[ Back to top ]