Fターム[5F140BF27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 3層目より上層の材料 (915) | 金属 (751) | 高融点金属 (221)

Fターム[5F140BF27]に分類される特許

141 - 160 / 221

半導体装置及びその製造方法

【課題】短チャネル効果を抑制するとともに、オン電流を向上させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板100に形成されたSTI領域103と、STI領域103に囲まれた活性領域と、活性領域を横切るように一方向に形成されたゲート電極12とを備え、半導体基板100は、活性領域とゲート電極12とが重なる領域において、活性領域の半導体基板100に活性領域の長軸方向と平行に形成された二つのゲートトレンチ108及び二つのゲートトレンチ108の間に位置し半導体基板100の一部であるフィン状部100fを有し、ゲート電極12は二つのゲートトレンチ108内に埋め込まれ且つフィン状部100f上にも形成され、フィン状部100fがチャネル領域となっているフィントランジスタを備える。これにより、チャネル領域の幅がゲート長よりも短いフィントランジスタが得られる。

(もっと読む)

半導体装置の製造方法

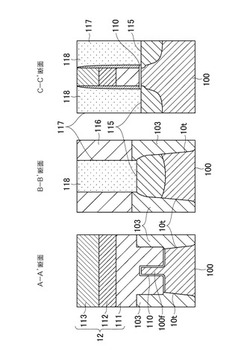

【課題】STI領域とゲートトレンチとの間に形成されるシリコンの薄膜部分をチャネル領域として用いる半導体装置の製造方法において、薄膜部分の膜厚及び幅の均一性を向上させる。

【解決手段】ゲートトレンチの延在方向と水平な断面A−A'において、STI領域104の上端部を半導体基板13の上に乗り上げさせ且つその乗り上げた部分の端部を半導体基板13に対して垂直となるように形成し、全面にシリコン窒化膜105及びシリコン酸化膜106を積層する。シリコン酸化膜106上にシリコン窒化膜107を形成し、シリコン窒化膜107をマスク形状にパターニングするドライエッチングの際、STI領域104の上端部はシリコン酸化膜106及びシリコン窒化膜105により保護される。STI領域104の上端部がマスクとなり、ゲートトレンチとSTI領域104との間にゲートトレンチ側に基板と略垂直な面を持つチャネル領域が形成される。

(もっと読む)

半導体装置の製造方法

【課題】ポリメタルゲート配線のシリコン膜のパターニングに際して、ダミーウエハを用いずに、且つ、チャンバー内の下部電極のダメージを伴うことなく、チャンバーのドライクリーニングを行う半導体装置の製造方法を提供する。

【解決手段】ポリシリコン膜の表面にシリコン窒化膜を有するウエハをチャンバー内に搬送し(ステップS1)、下部電極上に搭載した後に、まず、チャンバーのドライクリーニングを行い(ステップS2)、チャンバー内壁に付着したシリコン系の反応生成物を除去する。次いで、ウエハのドライエッチングを行い、シリコン窒化膜およびポリシリコン膜をパターニングする(ステップS3)。パターニング後に下部電極からウエハを取り外し、チャンバー外に搬出する(ステップS4)。この処理をウエハ毎に繰り返す。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに隣接するシリコンエピタキシャル層同士のショートを防止する。

【解決手段】活性領域13の露出面をドライエッチング又はウェットエッチングで掘り下げることにより、活性領域13の露出面には凹部13aが形成される。これにより、素子分離領域12を構成するフィールド酸化膜12の側面部分12aが露出し、凹部13aの周囲がフィールド酸化膜の側面部分12aで囲まれた状態となる。その後、凹部13aが形成された活性領域13の露出面にシリコンエピタキシャル層19を形成する。ここで、活性領域の露出面は掘り下げられており、活性領域13の幅方向の両端はフィールド酸化膜による壁で囲われていることから、シリコンエピタキシャル層19の横方向への成長を抑制することができ、互いに隣接するシリコンエピタキシャル層19、19間のショートを防止することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CVD法により上部電極を成膜する際の下地層へのダメージを防止する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板11上の層間絶縁膜16に設けられた凹部17の内壁を覆う状態で、層間絶縁膜16上にゲート絶縁膜18を形成する工程と、ゲート絶縁膜18上に、仕事関数を制御する第1ゲート電極層19aを形成する第1工程と、第1ゲート電極層19a上に、下地層へのバリア性を有する第2ゲート電極層19bを形成する第2工程と、第2ゲート電極層19bが設けられた凹部17を埋め込む状態で、第2ゲート電極層19b上に、化学的気相成長法により、第1ゲート電極層19aよりも抵抗の低い第3ゲート電極層19cを形成する第3工程とを行うことを特徴とする半導体装置の製造方法と半導体装置である。

(もっと読む)

CMOSトランジスタゲートにおいてリセスされた仕事関数金属

トランジスタゲートは、表面上に配置された一対のスペーサを有する基板と、スペーサ間で基板上にコンフォーマルに堆積された高k誘電体と、高k誘電体上とスペーサの側壁の一部に沿ってコンフォーマルに堆積されたリセスされた仕事関数金属と、リセスされた仕事関数金属上にコンフォーマルに堆積された第2の仕事関数金属と、第2の仕事関数金属上に堆積された電極金属とを含む。トランジスタゲートは、高k誘電体を基板上のスペーサ間にあるトレンチ内にコンフォーマルに堆積し、高k誘電体上に仕事関数金属をコンフォーマルに堆積し、仕事関数金属上に犠牲マスクを堆積し、仕事関数金属の一部を露出すべく犠牲マスクの一部をエッチングし、リセスされた仕事関数金属を形成すべく仕事関数金属の露出された一部をエッチングすることにより形成されうる。第2の仕事関数金属及び電極金属が、リセスされた仕事関数金属上に堆積されうる。 (もっと読む)

ゲート構造物の形成方法及びそれを用いた半導体装置の製造方法

【課題】改善された電気的特性を有するゲート構造物の形成方法及びそれを用いた半導体装置の製造方法を提供する。

【解決手段】基板上にゲート絶縁膜パターン、第1導電層パターン、及びダミーゲート層パターンを含む第1予備ゲート構造物を形成する。第1予備ゲート構造物に隣接する基板に不純物領域を形成した後、基板上に第1ゲート構造物を覆う絶縁層を形成する。ダミーゲート層パターンを除去してゲート絶縁膜パターン及び第1導電層パターンを含む第2予備ゲート構造物を形成した後、第1導電層パターン上に第2導電層パターンを形成する。ゲート電極を導電層パターンに変化されるか導電層パターンを形成するための犠牲層の役割を遂行するダミーゲート層パターンを適用することで、不純物領域の形成工程を含む半導体装置の製造のための高温工程下でもゲート電極が劣化されることを防止することができる。

(もっと読む)

半導体装置

【課題】埋め込み特性や膜特性に優れたシリコン酸化膜を高アスペクト比を有する凹部に形成することが可能な半導体装置を提供すること。

【解決手段】半導体装置は、半導体基板の主表面側に形成された凹部を有する下地領域と、前記下地領域の凹部内全体に埋め込まれた塩素を含有するシリコン酸化膜とを有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】CVD法でTaSiN系又はTiSiN系膜によるゲート電極を形成することで、成膜時の組成を制御することトランジスタの閾値電圧を制御する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Si原料として水素化シリコン、Ta原料としてTaのアミド化合物、イミド化合物又はハロゲン化物から選択される1つと又はTi原料として四塩化チタンを、N原料としてはNH3とをそれぞれ供給して、Si堆積膜層が0.2〜2.0nm、TaN又はTiN堆積膜層が0.5〜3.0nmを交互に積層させ、TaSixNy又はTiSixNy膜層(ここで、xが0.1〜3.0、yが0.5〜5.0の範囲にする。)を1〜20nmの層厚にする半導体装置の製造方法とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート絶縁膜の膜厚が増加することを抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に絶縁膜20を形成するステップと、絶縁膜上に第1の金属膜30を形成するステップと、第1の金属膜の上方に、酸素分子1モルあたりの金属酸化物を生成する際の生成エネルギーが負であって、かつ生成エネルギーの絶対値が第1の金属膜より大きい第2の金属膜50を形成するステップと、第1及び第2の金属膜にパターニングを行うステップと、所定の熱処理を行うステップとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの微細化に伴うショートチャネル効果やリーク電流の低減を可能とする。

【解決手段】p型シリコン基板101の主平面上に形成されたエピタキシャルSi層と、少なくともエピタキシャル層に形成されたチャネル領域と、該チャネル領域上にゲート絶縁膜106を介して形成されたゲート電極107とを含むトランジスタ構造を有し、このトランジスタ構造同士は互いに素子分離絶縁膜105を挟んで形成される半導体であって、チャネル領域の下部のパンチスルー・ストッパ層102にはチャネル領域よりも高濃度の不純物が含まれ、かつソース・ドレイン拡散層108は素子分離絶縁膜105上には延在しない。

(もっと読む)

AlN障壁層を有するGaN系電界効果トランジスタ、及びそのような電界効果トランジスタの製造方法

【課題】 本発明は、高出力、高耐圧、高速、高周波化などを達成し得る新規なGaN系ヘテロ接合トランジスタを提供することを目的とする。

【解決手段】上記課題は、GaN又はInGaNからなるチャネル層(4)と、AlNからなる障壁層(5)と含むヘテロ界面を構成する層と、トランジスタ素子表面に形成された絶縁膜(9)を有する電界効果トランジスタ(1)、特に絶縁膜としてSiN絶縁膜を用いた電界効果トランジスタや、そのような電界効果トランジスタの製造方法によって解決される。

(もっと読む)

半導体装置の製造方法

【課題】pチャネルトランジスタと共に形成される抵抗体の抵抗値をより安定化できるようにした半導体装置の製造方法を提供する。

【解決手段】ゲート電極5が形成されたシリコン基板1上にレジストパターン7を形成し、当該レジストパターン7とゲート電極5とをマスクにシリコン基板1にP+を斜めイオン注入することによってhalo層9を形成する。次に、抵抗体51の両端部分にp+層52を形成した後で、抵抗体51上にプロテクト酸化膜15を形成する。そして、このプロテクト酸化膜15をマスクにシリコン基板1に向けてAs+をイオン注入することによって、p+層52表面をアモルファス化し、その上にTiを形成し熱処理することによってTiシリサイド17を形成する。レジストパターン7とプロテクト酸化膜15は、抵抗体51の中央部分の真上全体と、その両端部分のうちの中央部分と接する隣接部位の真上とを連続して覆う形状を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体素子の微細化にともない半導体基板の斜面を使用したMOSトランジスタにおいては、斜面の上端に近い箇所と下端に近い箇所とでゲート電極膜の膜厚が異なることになり、ドライエッチングによるパターニングが困難になるという問題点がある。

【解決手段】 斜面上にゲート電極を有するMOSトランジスタは、最初に斜面の下端に近い箇所の下層ゲート電極膜のパターニングを行う。さらにそのゲート電極間のスペースを基板の主表面まで埋設させ主表面と高さを同一とした後、上層のゲート電極膜を成膜しゲート電極膜のパターニングを行う。このためにコンタクトホール開口時のアスペクト比が小さくなり、微細パターンのパターニングが可能となる。

(もっと読む)

複数の金属層を積層した半導体素子

【課題】CET特性及び絶縁特性を向上させた半導体素子を提供する。

【解決手段】基板110と、基板110上に積層され、高誘電体物質から形成されるゲート酸化膜120と、ゲート酸化膜120上に積層され、ゲート酸化膜120と同種金属の窒化物から形成される第1金属層131と、第1金属層131上に積層される第2金属層132と、第2金属層132上に積層される第3金属層133と、第3金属層133上に積層され、第1金属層131〜第3金属層133と共にゲート電極を形成する物質層140と、を含んでいる。これにより、半導体素子のゲート酸化膜と金属層間の化学的な反応により発生するCET特性の低下および電流の漏れなどを防止することで半導体素子の絶縁特性を向上させることができる。

(もっと読む)

二重仕事関数金属ゲートスタックを備えるCMOS半導体装置

【課題】二重仕事関数金属ゲートスタックを備えるCMOS半導体装置を提供する。

【解決手段】CMOS半導体装置は、PMOS及びNMOS装置の仕事関数を独立的に調節できる工程技術を利用して形成された二重仕事関数金属ゲート構造物を備えて、ゲート絶縁膜の信頼性に悪い影響を与えることをかなり低減または除去できる。

(もっと読む)

半導体装置の製造方法

【課題】P型MOSFETの閾値のバラつきを抑制して高品質の半導体装置を形成することができ、また、製品開発のコストを抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上100にゲート絶縁膜102を形成する第1の工程と、ゲート絶縁膜102上に、ゲート電極104を構成する導電体膜103を、有機材料を用いた形成法によって形成する第2の工程と、導電体膜103が形成されたシリコン基板100を、酸化性雰囲気である水蒸気と、還元性雰囲気である水素との混合雰囲気中で加熱する第3の工程と、を備えた半導体装置の製造方法であって、第3の工程における水蒸気に対する水素の分圧比が、炭素が酸化され、かつ、導電体膜104を構成する金属材料が還元される分圧であることを特徴とする。

(もっと読む)

接続部構造及びその製造方法

【課題】シリサイド上に接続孔を形成する際のエッチングで、高抵抗の変質層が発生することを防止する。

【解決手段】 基板中もしくは基板上に導電層を形成する。次に、導電層上を含む基板上に第1の金属膜を形成する。次に、基板に対して熱処理を行なって第1の金属膜と導電層とを反応させ、導電層上に選択的にシリサイド膜を形成する。次に、選択CVD法によりシリサイド膜上のみに第2の金属膜を形成する。次に、第2の金属膜上を含む基板上に絶縁膜を形成する。次に、絶縁膜の所定領域を開口して、第2の金属膜に到達するコンタクトホールを形成する。次に、コンタクトホール内を洗浄して、コンタクトホール底面における第2の金属膜表面に形成された変質層を除去する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ型ゲートの溝内への導電性膜の埋め込み性が向上した、半導体装置の製造方法を提供する。

【解決手段】トランジスタが形成される複数の活性領域を囲む、基板面に対して垂直方向の断面が逆テーパ形状の素子分離部を基板に形成する工程と、複数の活性領域におけるトランジスタのソースおよびドレインの領域を覆う耐酸化性絶縁マスクを形成する工程と、耐酸化性絶縁マスクの上から基板に対して異方性エッチング行い、活性領域にトレンチ型ゲート用の溝を形成する工程と、上記溝の基板表面に形成された自然酸化膜を除去する工程と、水素雰囲気で熱処理を行うアニール工程と、耐酸化性絶縁マスクを除去する工程と、アンモニア過酸化水素を含む溶液で洗浄を行う洗浄工程と、熱酸化法により溝の基板表面にゲート酸化膜を形成する工程とを有するものである。

(もっと読む)

電界緩和機能を有するIII族窒化物電力半導体

素子の耐圧性を改善するために、ゲートの周囲の電界を緩和する電界緩和機能を含むIII族窒化物電力半導体素子。 (もっと読む)

141 - 160 / 221

[ Back to top ]