Fターム[5F140BF33]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 構造、不純物の状態 (690) | 結晶性、結晶粒径 (224)

Fターム[5F140BF33]の下位に属するFターム

アモルファス、非晶質 (144)

Fターム[5F140BF33]に分類される特許

1 - 20 / 80

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の一部にメタルゲート電極を有するMISEFTにおいて、メタルゲート電極を構成するグレインの配向性のばらつきに起因するMISFETのしきい値電圧のばらつきを小さくする。

【解決手段】メタルゲート電極4a、4bに炭素(C)を導入することにより、メタルゲート電極4a、4b内のグレインの粒径が大きくなることを防ぎ、メタルゲート電極4a、4bの中に多数の小さいグレインを形成することにより、グレインの配向性を均一化し、ゲート電極の仕事関数のばらつきを低減する。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】電極材料が拡散するのを抑制し、特性の向上を実現する。

【解決手段】半導体装置を、ゲート電極3とゲート絶縁膜2との間、Al含有オーミック電極4、5とAu配線9との間、及び、ゲート電極3の下方及びAl含有オーミック電極4、5の上方、のいずれかに設けられ、第1TaN層6A、Ta層6B、第2TaN層6Cを順に積層した構造を有する電極材料拡散抑制層6を備えるものとする。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】NBTIを改善することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたn型ウェル領域102と、n型ウェル領域102上に形成され、ゲート絶縁膜104と、下部ゲート電極105、及び下部ゲート電極105上に形成された上部ゲート電極106を含むゲート電極120とを有するpチャネル型MISトランジスタとを備える。下部ゲート電極105は、結晶粒界を有する多結晶の金属窒化物で構成されており、当該結晶粒界には金属窒化物を構成する元素とは異なる元素が偏析されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

金属窒化膜、該金属窒化膜を用いた半導体装置、および半導体装置の製造方法

【課題】所望の実効仕事関数(例えば、高い実効仕事関数)を実現し、かつ、EOTが変化しない、またはEOTの変化を低減した金属窒化膜、金属窒化膜を用いた半導体装置、および半導体装置の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る金属窒化膜は、TiとAlとNを含有し、該金属窒化膜のTiとAlとNのモル比率(N/(Ti+Al+N))が0.53以上であり、かつ、上記金属窒化物層のTiとAlとNのモル比率(Ti/(Ti+Al+N))が0.32以下であり、かつ上記金属窒化物層のTiとAlとNのモル比率(Al/(Ti+Al+N))が0.15以下である。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されたMISFETのゲート電極の加工精度を向上することができる技術を提供する。

【解決手段】シリコン上にニッケルプラチナ合金膜を形成する(S101)。そして、第1加熱処理を実施する(S102)。このとき、第1加熱処理において、加熱温度は250℃〜270℃であり、加熱時間は30秒未満である。続いて、未反応のニッケルプラチナ合金膜を除去する(S103)。その後、第2加熱処理を実施する(S104)。このとき、第2加熱処理において、加熱温度は、450℃〜600℃である。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極として窒化チタン膜とシリコン膜の積層膜を用いたときに、窒化チタン膜が消失することを抑制する。

【解決手段】まず基板にゲート絶縁膜を形成する(ステップS10)。次いで、第1の基板温度で成膜処理を行うことにより、ゲート絶縁膜上に結晶化した窒化チタン膜を形成する(ステップS20)。次いで、第1の基板温度より低い第2の基板温度で成膜処理を行うことにより、窒化チタン膜上にシリコン膜を形成する(ステップS30)。次いで、窒化チタン膜及びシリコン膜を選択的に除去することにより、ゲート絶縁膜上に位置するゲート電極を形成する(ステップS40)。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子の特性や信頼性を向上させることが可能な半導体装置およびその製造方法を提供する。

【解決手段】Hfを含む高誘電率ゲート絶縁膜3上にゲート電極13、14を有する相補型電界効果型トランジスタにおいて、ゲート電極13、14の少なくともゲート絶縁膜3に接する部分は、Ni組成が40%を超えない結晶化したNiシリサイドを主成分とし、pチャネル上のゲート電極14に含まれるNiシリサイドとゲート絶縁膜3との界面にB、Al、Ga、In、Tlの中の少なくともひとつの元素を含み、且つ、nチャネル上のゲート電極13に含まれるNiシリサイドとゲート絶縁膜3との界面にN、P、As、Sb、Biの中の少なくともひとつの元素を含む半導体装置を提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】拡散層とゲート電極との少なくとも1つの上に耐熱性が向上したNiSi膜が形成された半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Si基板200と、Si基板200内に形成された拡散層10と、Si基板200上にSiを用いて形成されたゲート電極20との少なくとも1つと、前記拡散層10と前記ゲート電極20との少なくとも1つ上に接触して形成されたP元素を含有したNiSi膜40,42と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】所望のMOSトランジスタのみにチャネル領域に引っ張り応力を印加してキャリア移動度を向上させ、且つ、製造工程の複雑化を抑える。

【解決手段】シリコン基板10上にnMOSトランジスタのゲート絶縁膜13およびゲート電極14を非単結晶シリコンで形成し、ゲート電極14をマスクとして例えばAsやSb等の比較的質量数が大きい(質量数70以上)n型ドーパントを注入することで、nMOSトランジスタのソースドレイン領域を形成する。それにより、ゲート電極14は非晶質化する。そして、ゲート電極14が再結晶化する温度(約550℃)以下の温度条件でゲート電極14を覆うようにシリコン酸化膜40を形成し、その後1000℃程度の加熱処理を行う。それにより、ゲート電極14内に強い圧縮応力が残留すると共に、その下のチャネル領域には強い引っ張り応力が印加され、当該nMOSトランジスタのキャリア移動度は向上する。

(もっと読む)

キャパシタ構造及び半導体素子

【課題】キャパシタ構造において、電極間を流れる電流を抑制しつつ電極間の絶縁層を極限まで薄層化する。

【解決手段】ゲート電極Si層10と対向する電極としてのチャネルSi層30との間に所望の電圧を印加した際に、少なくともどちらか一方の電極物質でキャリアが存在しうるエネルギー範囲に存在する両電極物質の全エネルギーバンドについて、少なくとも片方の電極の該当エネルギーバンドの一部に関して、対向して配置した面の面方向の運動量の一致するエネルギーバンドがもう一方の電極の同一エネルギーのエネルギーバンドに存在しないように接合面及び接合面に垂直な軸に関する相対的回転角度を選択することで、電極間のキャリアの透過を抑制する。本発明のキャパシタ構造では、面方向の運動量が一致しないエネルギーバンドが存在するため、このエネルギーバンドが関与するキャリアの透過による電流を抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応でき、High−kゲート絶縁膜を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、p型層103上に設けられた第1のゲート絶縁膜115、TiNからなる第1のゲート電極116と、及び不純物を含む半導体からなる第1の上部ゲート電極117を有するNチャネル型MOSトランジスタ106と、n型層102上に設けられた第2のゲート絶縁膜109、TiN結晶からなり、(111)配向/(200)配向が1.5以上となるTiN層を少なくとも一部に含む第2のゲート電極110、及び不純物を含む半導体からなる第2の上部ゲート電極111を有するPチャネル型MOSトランジスタ105とを備えている。

(もっと読む)

高応力下にあるチャネルを有するMOSデバイスを製造するための方法

【解決手段】

シリコン含有基板を備えた半導体デバイスを形成するための方法が提供される。1つの例示的な方法は、シリコン含有基板を覆う多結晶シリコン層を堆積させることと、多結晶シリコン層をアモルファス化することと、アモルファス化された多結晶シリコン層をエッチングしてゲート電極を形成することと、ゲート電極を覆う応力誘起層を堆積させることと、シリコン含有基板を焼鈍してゲート電極を再結晶化することと、応力誘起層を除去することと、ゲート電極をエッチングマスクとして用いて基板内へ凹部をエッチングすることと、凹部内に不純物ドープのシリコン含有領域をエピタキシャル成長させることとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中のシリコン混晶層の形成を制御することにより、キャップ膜の形成を不要とし、シリサイド層を精度良く形成する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13と、ゲート絶縁膜13上に形成され、第2導電型のポリシリコン膜28Aとポリシリコン膜28A上に形成された炭素を含む第1のシリコン混晶層25とを有するゲート電極25Aと、第1のシリコン混晶層25上に形成された第1のシリサイド層29と、半導体領域10xにおけるゲート電極25Aの側方下の領域に形成された第2導電型の不純物拡散領域24と、不純物拡散領域24の上部領域に形成された炭素を含む第2のシリコン混晶層26と、第2のシリコン混晶層26上に形成された第2のシリサイド層30とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】high−k膜を含むFETにおいて、低抵抗金属として高融点金属を用いた場合のイオン注入時のゲートにおけるドーパント突き抜けの問題と、低抵抗金属のグレインサイズの下地依存に起因したPMISトランジスタとNMISトランジスタとのゲート抵抗の差を解決する。

【解決手段】high−k膜4上に形成されるゲート電極を、仕事関数金属膜5とその上部の第一の低抵抗膜6、第二の低抵抗膜7で構成したMISトランジスタにおいて、仕事関数金属膜5上の、タングステンからなる第一の低抵抗膜6のグレインサイズを前記第一の低抵抗膜6上の第二の低抵抗膜7のグレインサイズより小さくする。

(もっと読む)

半導体装置及びその製造方法

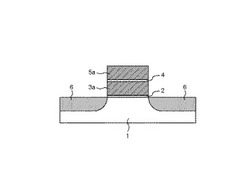

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜2上にアモルファスシリコン膜3を形成する工程と、前記アモルファスシリコン膜3に不純物イオン4をイオン注入する工程と、前記アモルファスシリコン膜3を加工することにより、前記ゲート絶縁膜2上にゲート電極3aを形成する工程と、を具備することを特徴とする半導体装置の製造方法。

(もっと読む)

1 - 20 / 80

[ Back to top ]