Fターム[5F140BF41]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388)

Fターム[5F140BF41]の下位に属するFターム

断面形状 (1,038)

段差部に形成されたもの (483)

埋込みゲート、チャネルの下に埋込み (26)

直列複数ゲート (66)

並列複数ゲート (130)

平面形状、配置 (630)

Fターム[5F140BF41]に分類される特許

1 - 15 / 15

半導体装置

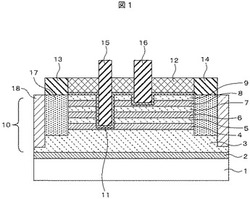

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

(もっと読む)

ゲート電極が駆動する電界効果型トランジスタおよびそれを有するセンサデバイス

【課題】 ゲート電極が可動な電界効果型トランジスタを提供する。

【解決手段】 半導体層と、前記半導体層内に少なくとも2つの活性領域と、前記活性領域に接するソース電極およびドレイン電極と、前記ソース電極と前記ドレイン電極との間の半導体層の上に絶縁層とゲート電極とを有する電界効果型トランジスタであって、

前記電界効果型トランジスタは前記ゲート電極および前記絶縁層の間に配置される、分子を吸着するための吸着部位を有し、

前記ゲート電極を駆動するための駆動手段を有することを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】高性能・高信頼性の半導体装置を製造するための半導体装置の製造方法を提供する。

【解決手段】半導体基板上に保護膜を形成し、保護膜を介して不純物をイオン注入する。注入した不純物を活性化して不純物層を形成した後、保護膜を除去する。その後、不純物層の表面部の半導体基板を除去し、表面部を除去した半導体基板上に半導体層をエピタキシャル成長する。

(もっと読む)

半導体デバイスを形成する方法

【課題】 ボイドフリーかつシームフリーの金属ゲート導体層が比較的薄い高kゲート誘電体層の上に位置決めされている少なくとも1つの高アスペクト比ゲート構造を有する相補型金属酸化膜半導体(CMOS)デバイスを形成する方法を提供する。

【解決手段】 これらの方法実施形態は、高アスペクト比ゲート・スタック開口部を下から上に金属ゲート導体層で充填するために電気メッキ・プロセスを使用するゲート交換戦略を取り入れている。電気メッキ・プロセス用の電子の発生源は、基板の裏面を直接通過する電流である。これは、シード層の必要性を排除し、ボイドまたはシームなしで金属ゲート導体層が形成されることを保証するものである。さらに、実施形態次第で、電気メッキ・プロセスは、所与の領域への電子流を増強するために(すなわち、メッキを増強するために)照明を受けて実行され、所与の領域への電子流を防止するために(すなわち、メッキを防止するために)暗闇で実行される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、FIN状の半導体部やゲート電極を精度良く形成すること、又は素子間の特性バラツキを改善することで、特性の優れたFIN型トランジスタを備える半導体装置を提供することを目的とする。

【解決手段】本発明は、一方にソース領域、他方にドレイン領域が形成されたFIN状の半導体部10と、ソース領域とドレイン領域との間で、FIN状の半導体部10をゲート絶縁膜を介して囲むように形成されたゲート電極17とを備える半導体装置である。そして、本発明に係る1つ解決手段は、ゲート電極17が、ウェットエッチング可能なメタル材料又はシリサイド材料を用いている。

(もっと読む)

半導体装置及びその製造方法

【課題】フィン型活性領域の断面形状が台形状である半導体装置において、パンチスルーの発生を防止する。

【解決手段】テーパー状の側面を有するフィン型活性領域13と、フィン型活性領域13の側面の一部を覆う側面被覆部14s及び上面の一部を覆う上面被覆部14tを有するゲート電極14と、フィン型活性領域13内に形成されたソース領域及びドレイン領域とを備え、ゲート電極14の側面被覆部14sの少なくとも一部は、上部よりも下部の方が幅が広くなっている。これにより、ゲート電極14による電界制御性が高められることから、パンチスルーの発生を防止することが可能となる。

(もっと読む)

半導体装置

【課題】厚いゲート絶縁膜を形成することに起因する不具合を生じさせることなく、高耐圧デバイスにも適用可能なMOSトランジスタを備えた半導体装置を提供する。

【解決手段】ドレイン領域はN−ドレイン領域3dとN+ドレイン領域11dからなる二重拡散構造を備えている。ゲート電極は、ゲート絶縁膜7上に形成された第1ゲート電極9と、第1ゲート電極上9にゲート電極間絶縁膜11を介して形成された第2ゲート電極13とからなる。第2ゲート電極13にゲート配線13gが接続され、第1ゲート電極9にはゲート配線13gは接続されていない。ゲート絶縁膜7とN+ソース領域11sの間の半導体基板1表面にフィールド絶縁膜15配置されている。第1ゲート電極9のドレイン領域側の端部はフィールド絶縁膜15上に配置されている。第2ゲート電極13に印加されるゲート電圧はゲート絶縁膜7とゲート電極間絶縁膜11で分割される。

(もっと読む)

窒化物系半導体ヘテロ接合電界効果トランジスタ

【課題】ノーマリオフ動作を達成でき、充分なチャンネル電流を得ることができ、かつしきい値電圧の制御が容易な窒化物系半導体ヘテロ接合電界効果トランジスタを提供する。

【解決手段】負の電荷を有する第三の層である浮遊ゲート層(32)が制御ゲート電極(34)とAlGaN 層(11)との間に設けられているので、実質的に浮遊ゲート層(32)に隣接するAlGaN 層(11)の電子に対するポテンシャルを実質的に高くし、チャンネルを空乏化する。これにより、ゲート電圧がゼロの時チャンネルに電流(ドレイン電流)を流れなくする、即ちいわゆるノーマリオフ動作を達成することが出来る。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高性能化が必要な回路ブロックや回路部に対して応力を付加することにより、その回路ブロックや回路部の高性能化が実現できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体チップ基板30内に少なくとも金属酸化物半導体(MOS)トランジスタ36を含む回路と、この回路を含み、上部にこの回路を保護する保護膜41で覆われた回路ブロックを複数有してなる半導体装置20であって、この半導体装置20の電流能力およびしきい値電圧が所定の値を満たさない高性能化が必要な回路ブロックの上部のみに、少なくとも保護膜41を介して複数のバンプ23a、23b、23cが形成され、この複数のバンプ23a、23b、23cはMOSトランジスタ36に応力を付加して移動度を増加させて高性能化が実現できる。

(もっと読む)

MOS型電界効果トランジスタ

【課題】 高温環境におけるMOS型電界効果トランジスタのリーク電流を抑制するようにした半導体装置を提供する。

【解決手段】 ソース領域3とチャンネル形成領域4の間に半導体基板よりも濃度の濃いソースオフセット領域7を設けて、かつ、ソースオフセット領域7の上のゲート酸化膜を薄くすることで、しきい値電圧を低く抑えたままリーク電流を抑制する。

(もっと読む)

フラッシュメモリ素子の製造方法

【課題】短いゲート長を有しながらセル接合部間に発生するパンチスルー性漏洩電流を防止するフラッシュメモリの製造方法を提供する。

【解決手段】セル領域、低電圧領域及び高電圧領域が定義された半導体基板100の上部にゲート112を形成した後、上記セル領域のみオープンさせてイオン注入工程を実施し、上記半導体基板内にセル接合を形成する段階;第1の熱処理工程を実施した後、上記低電圧領域のみオープンして低濃度イオン注入工程を実施する段階;上記高電圧領域のみオープンさせてイオン注入工程を実施した後、上記ゲートの側面にスペーサ120を形成する段階;及び上記低電圧領域のみオープンさせて高濃度イオン注入工程を実施した後、第2の熱処理工程を実施する段階を含むフラッシュメモリ素子の製造方法。

(もっと読む)

複合半導体装置

【課題】HEMTとダイオードとから成る複合半導体装置の小型化が要求されている。

【解決手段】本発明に従うHEMTとダイオードとから成る複合半導体装置は、電子走行層3と電子供給層4とを含む半導体領域5と、この一方の主面上に形成されたソース電極7及びドレイン電極8とゲート電極12とを有し、更に、半導体領域5の一方の主面上におけるゲート電極12とドレイン電極8との間にショットキー電極60を有する。ショットキー電極60は導体60aによってソース電極7に接続されている。ショットキー電極60と半導体領域5とで形成されたショットキーダイオードは、帰還又は回生又は保護ダイオードとして機能する。このショットキーダイオードの電流はゲート電極12に基づく空乏層に妨害されない。

(もっと読む)

MOS型半導体装置

【課題】 MOS型半導体装置に関し、薄膜化されたゲート絶縁膜中の可動性且つイオン性の不純物を簡単な構成で排除できるようにして、MOS型半導体装置の信頼性を向上させようとする。

【解決手段】 ゲート絶縁膜13上のゲート電極14両側で、且つ、ゲート絶縁膜13の下地であるチャネル領域18から外れた位置に形成され、ゲート電極14直下のゲート絶縁膜13から可動不純物19を排除する電圧が印加されるサブゲート電極17を備える。

(もっと読む)

イオンバランスセンサ

【課題】簡単な構成でイオンバランスを正確に検出し、小形化及び製造コストの低減を可能にする。除電対象物の表面近くにおけるイオンバランスの検出を可能にする。

【解決手段】正イオンまたは負イオンにより帯電するアンテナ20と、アンテナ20がゲート電極Gに接続され、接地されたソース電極Sとゲート電極Gとの間にイオンバランス検出用抵抗Rが接続されると共に、ソース電極Sとドレイン電極Dとの間に直流電源VDSと負荷抵抗RLとが直列に接続されたノーマリーオン形のMOSFET11とを備える。帯電したアンテナ20接地間をイオンバランス検出用抵抗Rを介して流れる電流による電圧降下によってゲート電極Gの電圧を変化させ、この電圧によるドレイン電流の変化を検出してアンテナ20を帯電させたイオンの正負のバランスを検出する。

(もっと読む)

半導体装置

【課題】 信頼性の高い半導体装置を実現するために、寄生容量の大きな半導体装置を提供する。

【解決手段】 半導体装置は、第1方向に延在する突出部1bを有する半導体基板1を含む。ゲート絶縁膜11は、突出部の上面上および第1方向に沿う側面上に配設される。ゲート電極12は、第1部分12aと第2部分12bを有する。第1部分は、突出部と交差し、且つ突出部の上面上のゲート絶縁膜上に配設される。第2部分は、突出部の側面上のゲート絶縁膜上に配設され、且つ第1方向における長さが第1部分の第1方向における長さより長い。1対のソース/ドレイン領域13が、ゲート電極の第1部分の下方の領域を挟むように突出部の表面に形成される。

(もっと読む)

1 - 15 / 15

[ Back to top ]