Fターム[5F140BG11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁構造及び配置 (6,762) | ゲート側壁材料 (3,458)

Fターム[5F140BG11]の下位に属するFターム

SiO (1,611)

PSG、BSG、BPSG (16)

SiN (1,528)

多結晶Si (32)

高融点金属珪化物(高融点金属を含む) (10)

空隙 (15)

Fターム[5F140BG11]に分類される特許

1 - 20 / 246

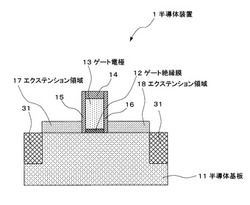

半導体装置の製造方法

【課題】ヒ素(As)を高濃度にドーピングした状態でエクステンション領域のエピタキシャル成長膜表面に凹凸を発生させることなく、平滑な面に形成することを可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介してゲート電極13を備え、前記ゲート電極13の両側の前記半導体基板11上に形成された不純物を含有してなるエクステンション領域17、18を備えた半導体装置1であって、前記エクステンション領域17、18は、シリコンゲルマニウムにヒ素を含む状態でエピタキシャル成長されたエピタキシャル成長膜からなり、このエピタキシャル成長膜は、ヒ素をドーピングしながらシリコンとゲルマニウムとを前記半導体基板11上に選択的にエピタキシャル成長させて形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域のゲート絶縁膜への酸化剤の進入を防止しつつ、第2の領域の複数の第1の配線間に設けられた酸化アルミニウム膜を選択的に除去する。

【解決手段】第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線を覆うように形成した第1の絶縁膜をマスクとして、第1の領域に第1のイオン注入を施す。その後、第1の領域において第1の積層体の側壁を覆い、第2の領域において複数の第1の配線間を埋設するように形成した、酸化アルミニウムを主体とする第2の絶縁膜をマスクとして、第1の領域に第2のイオン注入を施す。第2の絶縁膜を、第1の絶縁膜に対して選択的に除去する。

(もっと読む)

撮像装置の製造方法

【課題】プラズマ酸化によりシリコン基板上に形成される酸化膜の金属汚染量を低減すること。

【解決手段】酸化膜の形成方法は、不活性ガスと、前記不活性ガスに対する混合割合が0よりも大きく且つ0.007以下である酸化ガスと、を含む混合ガスからプラズマを生成する工程と、前記プラズマを用いてシリコン基板の表面に酸化膜を形成する工程と、を含む。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

シリコンに対する誘電材料の選択エッチング方法及びシステム

【課題】 本発明はドライプラズマエッチングを用いた基板のエッチング方法に関する。

【解決手段】 ドライプラズマエッチングシステム内で誘電体層をシリコン及びポリシリコンに対して選択的な均一エッチングを行う方法及びシステムが記載されている。エッチング用化学は、たとえばCH2F2やCHF3のようなフルオロハイドロカーボンを有する。高いエッチング選択性及び受容可能な均一性は、CH2F2の流速やドライプラズマエッチングシステムと結合する出力を含むプロセス条件を選択することによって実現されて良い。それにより、エッチングプラズマ中での活性エッチングラジカルとポリマー生成ラジカルとの適切なバランスがとられる。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても高耐圧トランジスタのドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】ゲート電極104Aの側面の側方下に位置する領域の半導体基板(活性領域)101の表面部が除去されて掘り下げ部121が形成されている。掘り下げ部121の側壁面及び底面の近傍に位置する部分の半導体基板101中に低濃度ドレイン領域105A2が形成されている。ゲート電極104Aの側面並びに掘り下げ部121の側壁面及び底面の一部を覆うように絶縁性サイドウォールスペーサ108Aが形成されている。絶縁性サイドウォールスペーサ108Aの外側で且つ掘り下げ部121の底面の近傍に位置する部分の半導体基板101中に、低濃度ドレイン領域105A2に囲まれるように高濃度ドレイン領域109A2が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

TiC膜を含む半導体構造を形成する方法

【課題】 TiC膜を含む半導体構造を形成する方法を提供する。

【解決手段】 高誘電率(k)の誘電体14および界面層12を含む積層体を基板10の表面上に設けるステップと、Heによって希釈された炭素(C)源およびArを含む雰囲気において、Tiターゲットをスパッタすることにより、前記積層体上にTiC膜16を形成するステップとを含む、半導体構造を形成する方法である。

(もっと読む)

化合物半導体装置

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】用途によって異なるしきい値電圧を有するトランジスタを有する半導体装置、及び工程数の増加を抑えた当該半導体装置を製造する方法を提供する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1のゲート絶縁膜110aと、第1のゲート絶縁膜110a上に形成された第1のゲート電極109aと、第1のゲート絶縁膜110aの側面上及び第1のゲート電極109aの側面上に形成された第1のサイドウォール絶縁膜140aとを有する第1導電型の第1のMISFET150を備えている。第1のサイドウォール絶縁膜140aの少なくとも一部には、第1のゲート絶縁膜110aに正または負の固定電荷を誘起するための元素が含まれている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ファインゲート構造を採用してゲート電極の微細化を図るも、ゲート電極の周辺における電界集中によるデバイス特性の変動・劣化を防止する、信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極8は、ファインゲート構造の幹状の下方部分8aと、下方部分8aの上端から当該上端よりも幅広に傘状(オーバーハング形状)に拡がる上方部分8bとが一体形成されており、下方部分8aは、下端を含む第1の部分8aaと、第1の部分8aa上の第2の部分8abとを有し、保護壁7は、第1の部分8aaの両側面のみを覆うように形成されている。

(もっと読む)

1 - 20 / 246

[ Back to top ]