Fターム[5F140BG18]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | イオン注入時ゲート保護層(最外レジストを除く) (497)

Fターム[5F140BG18]の下位に属するFターム

ゲート保護材料(ゲート電極以外) (478)

Fターム[5F140BG18]に分類される特許

1 - 19 / 19

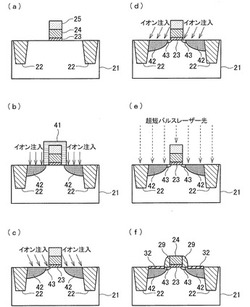

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

半導体装置

【課題】 LDD形成工程に於けるプラズマプロセスが原因となり生じる素子の

損傷を極力低減した半導体装置の作製方法を提供すること。

【解決手段】 基板全面を覆うように導電性膜を形成した状態で、ハードマスク

を利用した半導体装置の作製方法でLDD構造の素子を形成することにより、L

DD形成工程におけるプラズマプロセスによる素子への損傷を極力低減する。導

電性膜が全面に形成されていることにより、異方性エッチング等のプラズマによ

る処理(プラズマプロセス)においてゲート電極に蓄積される電荷密度を低減で

き、プラズマプロセスによる損傷を低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化された構造においても効果を発揮する歪みシリコン技術を適用した半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板中の前記ゲート絶縁膜下に形成されたチャネル領域と、前記チャネル領域の両側に形成された第1の層、および前記第1の層の下層に位置し、ゲート電極中央側の端部の位置が前記第1の層よりも前記ゲート電極中央に近い第2の層を含み、前記チャネル領域に歪みを発生させる歪み付与層と、前記チャネル領域の両側に、少なくとも一部が前記歪み付与層と重なるように形成されたソース・ドレイン領域と、を有する。

(もっと読む)

自己整合エピタキシャルソース及びドレイン張り出し部を有する半導体デバイス

ゲート誘電層に近接する自己整合ソース及びドレイン張り出し部を有するトランジスタの作製方法は、基板上にゲート積層体を作製する工程、前記ゲート積層体に隣接する前記基板の領域へドーパントを注入する工程であって、前記ドーパントは前記基板のエッチング速度を増大させ、かつ前記ソース及びドレイン張り出し部の位置を画定する工程、前記基板のドーパントが注入された領域上に設けられた前記ゲート積層体の横方向で対向する面に一対のスペーサを形成する工程、前記基板のドーパントが注入された領域及び該領域の下に位置する前記基板の一部をエッチングする工程であって、前記ドーパントが注入された領域のエッチング速度は該領域の下に位置する前記基板の一部のエッチング速度よりも速い工程、並びに、前記の基板のエッチングされた部分中にシリコンベースの材料を堆積する工程、を有する。  (もっと読む)

(もっと読む)

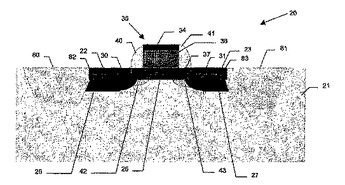

半導体構造体およびその形式、方法(多層埋込みストレッサを形成するための構造および方法)

【課題】デバイス・チャネル領域に歪みを誘起する半導体構造体で使用される、段階的ドーパント分布構造を有する多層埋込みストレッサを提供する。

【解決手段】本発明の多層ストレッサは、ソース/ドレイン領域が一般に位置決めされる半導体構造体の部分内に形成される。本発明の多層ストレッサは、アンドープか低濃度にドープされた第1の共形エピ半導体層と、第1のエピ半導体層に比べて高濃度にドープされた第2のエピ半導体層とを含む。第1および第2のエピ半導体層各々は、同じ格子定数を有し、この格子定数は、それらの半導体層が埋め込まれた基板の格子定数と異なっている。本発明の多層埋込みストレッサを含む構造は、応力近接と短チャネル効果の良好なバランスを実現し、さらに深いソース/ドレイン領域の形成中に一般に生じるどんな可能な欠陥もなくするか、実質的に減少させる。

(もっと読む)

半導体装置およびその製造方法

【課題】携帯電話機などに使用されるRFモジュールの小型化を図ることのできる技術を提供する。

【解決手段】RFモジュール25を構成する配線基板26上に、増幅回路が形成された半導体チップ28と、増幅回路を制御する制御回路が形成された半導体チップ27とを搭載する。そして、半導体チップ27上のボンディングパッド30と半導体チップ28上のボンディングパッド31とを中継パッドを介さずにワイヤ32で直接接続する。このとき、半導体チップ28上に形成されているボンディングパッド31の形状を正方形ではなく矩形形状(長方形)にする。

(もっと読む)

ゲート電極の高さの制御方法

【課題】シリサイドプロセスにおいてゲート電極の高さを制御する方法を提供する。

【解決手段】シリサイドプロセスにおいてゲート電極の高さを制御する方法が、 少なくとも1つのゲート電極13のそれぞれの上に犠牲キャップ層18が、半導体基板10の上に所定の高さで堆積されている工程と、 犠牲層18の上に酸化物からなる追加層14を形成する工程と、 犠牲キャップ層18を上部に有する少なくとも1つのゲート電極を備えた半導体基板10を、材料17を用いて覆う工程と、 化学的機械的ポリッシング(CMP)により平坦化を行う工程と、 少なくとも1つのゲート電極13上の、犠牲キャップ層18が露出するまで除去する工程と、 ゲート電極13のそれぞれから、犠牲キャップ層18を除去し、ゲート電極13のそれぞれが、所定の高さを有するようにする工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ型ゲートの溝内への導電性膜の埋め込み性が向上した、半導体装置の製造方法を提供する。

【解決手段】トランジスタが形成される複数の活性領域を囲む、基板面に対して垂直方向の断面が逆テーパ形状の素子分離部を基板に形成する工程と、複数の活性領域におけるトランジスタのソースおよびドレインの領域を覆う耐酸化性絶縁マスクを形成する工程と、耐酸化性絶縁マスクの上から基板に対して異方性エッチング行い、活性領域にトレンチ型ゲート用の溝を形成する工程と、上記溝の基板表面に形成された自然酸化膜を除去する工程と、水素雰囲気で熱処理を行うアニール工程と、耐酸化性絶縁マスクを除去する工程と、アンモニア過酸化水素を含む溶液で洗浄を行う洗浄工程と、熱酸化法により溝の基板表面にゲート酸化膜を形成する工程とを有するものである。

(もっと読む)

pFET材料としての金属酸窒化物を用いた半導体構造およびその製造方法

【課題】高k誘電体を含むゲート・スタック上において熱に対して安定な新規の金属化合物であって、金属炭化物の場合に起こるような炭素拡散を引き起こさない金属化合物を提供すること。

【解決手段】仕事関数が約4.75から約5.3、好ましくは約5eVであるp型金属であり、高k誘電体とインタフェース層とを含むゲート・スタック上で熱に対して安定なMOxNyを含む金属化合物、およびこのMOxNy金属化合物を製作する方法が提供される。さらに、本発明のMOxNy金属化合物は、1000℃において非常に効率的な酸素拡散障壁であり、p金属酸化物半導体(pMOS)デバイスにおいて、非常に攻撃的な等価酸化膜厚(EOT)および14Å未満の反転層厚を可能にする。上式で、Mは元素周期表のIVB、VB、VIBまたはVIIB族から選択された金属、xは約5から約40原子%、yは約5から約40原子%である。

(もっと読む)

半導体構造およびその製作方法(チャネルの応力向上のための低ヤング率スペーサ)

【課題】チャネル領域を有する半導体基板を使用する半導体構造およびその製作方法を提供すること。

【解決手段】ゲート電極が、半導体基板上に配置される。スペーサが、ゲート電極の側壁に隣接して配置される。このスペーサは、約10〜約50GPaのモジュラスを有する材料で形成される。このモジュラスは、チャネル領域内に向上した応力をもたらす。

(もっと読む)

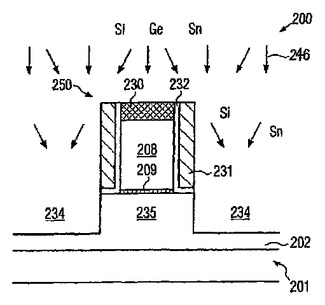

高共有半径の原子を含む埋め込まれた半導体層を利用したシリコンベースのトランジスタに歪みを生成する技術

共有半径が大きくされた原子種、例えば少なくとも一部が置換されたゲルマニウム、を導入することにより、ゲルマニウムの集塊化ならびに格子の欠陥による応力緩和のリスクを低減することができる、非常に実効的な歪みのメカニズムが提供される。錫などの、半径が増加した原子種は、水素化錫に基づくエピタキシャル成長技術により、容易に導入することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 しきい値電圧のばらつきの少ないゲート電極を有するCMOSデバイスを備えた半導体装置を提供することを可能にする。

【解決手段】 半導体基板に設けられた第1導電型チャネルMISトランジスタと、半導体基板に設けられた第2導電型チャネルMISトランジスタと、を備え、第2導電型チャネルMISトランジスタのゲート電極中の、ゲート絶縁膜との界面から膜厚方向に少なくとも1nm以下の領域での酸素濃度は1020cm−3以上、1022cm−3以下である。

(もっと読む)

超格子を間に有するシャロー・トレンチ・アイソレーション(STI)領域を含む半導体デバイス、及びその製造方法

半導体デバイスは、半導体基板と、基板内の複数のシャロー・トレンチ・アイソレーション(STI)領域とを含んでいる。より具体的には、STI領域の少なくとも一部はディボットを含んでいる。半導体デバイスは更に、隣接し合うSTI領域間それぞれの超格子と、ディボット内それぞれの非単結晶の梁部とを含んでいる。

(もっと読む)

(もっと読む)

電気的に活性なドープト結晶性Si含有膜の堆積方法

【課題】

【解決手段】比較的高いレベルの第III族/第V族ドーパントを含有するSi含有膜の製造方法は、トリシランおよびドーパント前駆体を使用しての化学蒸着を包含する。少なくとも約3×1020原子cm−3の電気的に活性なドーパントを含有する結晶性ケイ素膜を含む、非常に高いレベルの置換型組み込みが、得られ得る。置換的にドープされたSi含有膜は、堆積の間にエッチャントガスを導入することによって、混合基板の結晶性表面上へ選択的に堆積され得る。

(もっと読む)

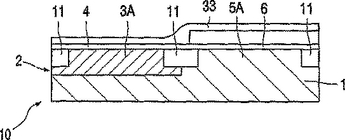

半導体装置の製造方法とそのような方法により得られる半導体装置

この発明は、基板(1)と半導体本体(2)とを有する半導体装置(10)であって、第一のチャネル領域(3A)と第一の導体を含み且つ誘電体層(4)によりチャネル領域から分離された第一のゲート電極(3B)とを有する第一の(NMOS)FET(3)を備え、そして、第二のチャネル領域(5A)と第一の導体とは異なる第二の導体を含み且つ誘電体層(4)によりチャネル領域(5A)から分離された第二のゲート電極(5B)とを有する第二の(PMOS)FET(5)を備え、第一及び第二のゲート電極(3B、5B)を形成するために、誘電体層(4)が備えられた半導体本体(2)上に第一の導体層(33)が堆積され、導体層(33)は、その後、第一のチャネル領域(3A)外部で除去され、その後、第二の導体層(55)が半導体本体(2)上に堆積され、そして、第一の導体層(33)が堆積される前に、誘電体層(4)上に中間層(6)が堆積される半導体装置の製造方法に関する。この発明によれば、中間層(6)のための材料として誘電体層(4)に対し選択的にエッチング可能な材料が選ばれ、そして、第一の導体層(33)が堆積される前に、第一のチャネル領域(3A)の位置で中間層(6)が除去され、そして、第一の導体層(33)が堆積され、第一のチャネル領域(3A)外部で除去された後に、そして、第二の導体層(55)が堆積される前に、第二のチャネル領域(5A)の位置で中間層(6)が除去される。従って、FETが、簡単な方法で、且つ、それらのゲート誘電体にダメージを与えずに得られる。好ましくは、中間層(6)に対して選択的にエッチング可能なさらなる中間層(8)が中間層(6)上に堆積される。  (もっと読む)

(もっと読む)

性能が向上されたCMOS素子及びその製造方法

【課題】 性能が向上されたCMOS素子及びその製造方法を提供する。

【解決手段】 本発明のCMOS素子は、第1の幅領域と、該第1の幅より広い第2の幅領域を有するとともにコンタクト形成領域になる少なくとも一つの多幅アクティブ領域対と、を含む第1のアクティブ領域と、第1のアクティブ領域上に配列された第1のゲートと、第1のアクティブ領域内に形成された第1の導電型ソース/ドレーン領域と、を含む第1の導電型MOSトランジスタ、および、第1の幅より広い第3の幅を有する第2のアクティブ領域と、第2のアクティブ領域上に配列された第2のゲートと、第2のアクティブ領域内に形成された第2の導電型ソース/ドレーン領域と、を含む第2の導電型MOSトランジスタを備える。そして、CMOS素子の製造方法もまた提供される。これにより、電子と正孔の移動度の均衡が得られてCMOS素子の性能を向上することができる。

(もっと読む)

マスキング方法

本発明はマスキング方法を包含する。1つの実施において、ホウ素ドープアモルファスカーボンを含むマスキング材料が、半導体基板上に形成されたフィーチャーを覆って形成される。マスキング材料は少なくとも約0.5原子パーセントのホウ素を含む。マスキング材料は実質的に異方的にエッチングされ、ここでそのエッチングはホウ素ドープアモルファスカーボンを含む異方的にエッチングされたサイドウォールスペーサをフィーチャーのサイドウォール上に形成するのに有効である。次に、スペーサに最も近い基板が、ホウ素ドープアモルファスカーボンを含むスペーサをマスクとして用いながら加工される。スペーサに最も近い基板を加工した後、ホウ素ドープアモルファスカーボンを含むスペーサが基板からエッチングされる。他の実施および面も考えられる。 (もっと読む)

1 - 19 / 19

[ Back to top ]