Fターム[5F140BG41]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極形成後の処理 (1,641)

Fターム[5F140BG41]の下位に属するFターム

Fターム[5F140BG41]に分類される特許

1 - 20 / 99

ポリメタルゲート電極を持つ半導体素子の製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの特性のばらつきを低減するために有利な技術を提供する。

【解決手段】MOSトランジスタを含む半導体装置の製造方法は、半導体基板の上に形成された第1絶縁膜の上にゲート電極材料層を形成する工程と、前記ゲート電極材料層の上にエッチングマスクを形成する工程と、前記ゲート電極材料層をパターニングすることによりゲート電極を形成する工程と、前記ゲート電極が形成された前記半導体基板の上に第2絶縁膜を形成する工程とを含み、前記ゲート電極を形成する工程では、前記ゲート電極材料層がパターニングされるとともに、少なくとも、前記ゲート電極の側面の下部と、前記第1絶縁膜のうち前記側面に隣接する部分とを保護する保護膜が形成され、前記第2絶縁膜を形成する工程では、前記保護膜を覆うように前記第2絶縁膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

プラズマ処理方法、プラズマ処理装置、及び、半導体装置の製造方法

【課題】結晶欠陥および金属汚染低減が可能な半導体基体の処理方法、そのための装置、また、それを用いた半導体装置の製造方法を提供する。

【解決手段】CとNとを含む混合ガスをプラズマ化してCN活性種を生成し、生成したCN活性種により半導体基体11の半導体層の表面を処理する。特に、前記処理としては、前記半導体基体11の表面の半導体層を前記CN活性種によりパッシベートすることを含む。さらに、そのことにより、表面汚染金属および半導体中の欠陥を除去する。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

【課題】CMOSトランジスタのソース−ドレイン置換技術に関し、装置一式を利用して基板材料に窪みをエッチングして、その後、応力を有する異なる材料を堆積することに関し、大気に曝すことなく、エッチングとその後の堆積とを行う方法の提供。

【解決手段】エッチングおよびデポジションによりCMOSトランジスタの接合領域を形成する方法であって、

第1接合領域270を形成すべくゲート電極190の隣の基板120の第1箇所と、前記基板120に第2接合領域280を形成すべく前記ゲート電極190を介して前記第1箇所とは反対側に位置する前記基板120の第2箇所とを除去する工程と、前記第1接合領域270と前記第2接合領域280とに結晶質材料のエピタキシャル厚みを有する層を形成する工程とを含み、前記除去する工程と前記形成する工程は同一のチャンバ内で前記チャンバの封止を破ることなく行う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

【課題】半導体デバイスを提供する。

【解決手段】理論的な金属:酸素化学量論比を有する高kゲート誘電体、前記高kゲート誘電体の上部に設置された、Mを遷移金属として、組成がMxAlyで表されるアルミナイドを含むNMOS金属ゲート電極、および前記高kゲート誘電体の上部に設置された、アルミナイドを含まないPMOS金属ゲート電極、を有するCMOS半導体デバイス。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

半導体素子

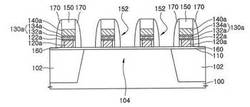

【課題】選択的酸化工程を含む金属ゲートパターンを有する半導体素子を提供する。

【解決手段】半導体素子は、半導体基板、半導体基板上に形成されたポリシリコン層、ポリシリコン層上に形成されたバリヤ金属層、及びバリヤ金属層上に形成されたタングステン層を含み、側壁を有する金属ゲートパターンと、金属ゲートパターンの側壁上に形成されたシリコンオキサイド層と、金属ゲートパターンの側壁のシリコンオキサイド層上に形成されたシリコンナイトライド層と、を含む半導体素子であって、金属ゲートパターンは、90nm未満のゲート長を有し、シリコンオキサイド層は、ポリシリコン層の側壁に接触し、シリコンオキサイド層は、第1部分及び第2部分を含むが、第1部分は、ポリシリコン層の側壁の直接上に位置し、第2部分は、タングステン層の側壁上に位置し、第1部分は、第2部分よりさらに厚いことを特徴とする。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置のチャネル移動度の向上を図る。

【解決手段】ゲート酸化膜形成工程の降温時に、ウェット雰囲気を維持したまま、終端・脱離温度(650〜850℃)以下まで降温させる。これにより、ゲート酸化膜とチャネル領域を構成するp型ベース層の界面のダングリングボンドをHもしくはOHの元素で終端させることが可能となる。このため、高いチャネル移動度の反転型ラテラルMOSFETとすることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極への水素の拡散を防止することにより、ゲート絶縁膜の劣化を抑制し、信頼性の高い半導体装置を提供すること。

【解決手段】半導体装置は、ポリシリコンを含むゲート電極と、ゲート電極の少なくとも上面を覆い、水素を貯蔵する機能を有する水素貯蔵層と、を備える。好ましくは、バリア層は、組成式SixNyOZの酸窒化膜を含有し、x:y:z=1:1:0.1〜0.7である。

(もっと読む)

半導体装置の製造方法

【課題】歩留まりに優れた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板(シリコン基板7)上にゲート絶縁膜5とゲート電極膜(ポリシリコン膜3)とをこの順に形成し、ポリシリコン膜3上にハードマスク(第2のハードマスク2)を形成する工程と、第2のハードマスク2を用いて、ポリシリコン膜3を選択的にエッチングして、ゲート電極20を形成する工程と、ゲート絶縁膜5の側壁、ゲート電極20の側壁、第2のハードマスク2の側壁および上面上、ならびにシリコン基板7上に、第1の絶縁膜(第1のスペーサ用絶縁膜)を形成する工程と、異方性ドライエッチングを行うことにより、シリコン基板7上、ならびに第2のハードマスク2の上面上および側壁上の第1のスペーサ用絶縁膜を除去しつつ、ゲート絶縁膜5およびゲート電極20の側壁上に第1の絶縁膜(第1のスペーサ)を残す工程と、第2のハードマスク2を除去する工程と、ゲート電極20および第1のスペーサをマスクとしてシリコン基板7にイオン注入を行う工程と、を含む

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を有するMISFETを備えた半導体装置の信頼性向上を図る。

【解決手段】nチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとLaとOとを主成分として含有するHf含有絶縁膜4aを形成し、pチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとAlとOとを主成分として含有するHf含有絶縁膜4bを形成する。それから、金属膜7とシリコン膜8を形成し、これらをドライエッチングでパターニングしてゲート電極GE1,GE2を形成する。その後、ゲート電極GE1,GE2で覆われない部分のHf含有絶縁膜4a,4bをウェットエッチングで除去するが、この際、フッ酸を含有しない酸性溶液でのウェット処理とアルカリ性溶液でのウェット処理とを行ってから、フッ酸を含有する酸性溶液でのウェット処理を行う。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

半導体デバイスの製造方法及び基板処理装置

【課題】金属製のゲート電極(メタル電極)のダメージを熱酸化により修復する際の高誘電率ゲート絶縁膜の結晶化を抑制する。

【解決手段】エッチングにより側壁が露出した高誘電率ゲート絶縁膜とメタル電極とを有する基板を処理室内に搬入する工程と、処理室内で、基板を高誘電率ゲート絶縁膜が結晶化しない温度に加熱した状態で、基板に対してプラズマで励起した水素含有ガスと酸素含有ガスとを供給して酸化処理を施す工程と、処理後の基板を処理室内から搬出する工程と、を有し、酸化処理を施す工程では、水素含有ガスの活性化時期と酸素含有ガスの活性化時期とが互いに一致するよう、処理室内への水素含有ガスの供給を開始した後、所定時間経過してから処理室内への酸素含有ガスの供給を開始する。

(もっと読む)

1 - 20 / 99

[ Back to top ]