Fターム[5F140BG43]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極形成後の処理 (1,641) | 不純物の導入 (232) | イオン注入 (191)

Fターム[5F140BG43]に分類される特許

1 - 20 / 191

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

半導体装置の製造方法

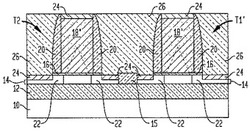

【課題】 CMOS型半導体装置におけるデュアルゲート構造のゲート電極をエッチングにより形成する時に、局所的なゲート絶縁膜の「突き抜け」やゲート電極サイドエッチ等の欠陥が発生することを防止できる製造方法を提供する。

【解決手段】 ゲート絶縁膜5を介して半導体基板1上に形成されたシリコン膜等の、実質的に不純物を含まない半導体膜6を選択的にエッチングしてゲート電極7を形成する。隣接するゲート電極7間の領域をレジスト等の絶縁膜9で埋め込む。さらに例えば所定のゲート電極7が形成された領域を覆うマスク層10を形成し、絶縁膜9とマスク層10とをマスクとして、マスク層10で覆われないゲート電極7にイオン注入等の手段により所定導電型の不純物を導入する。同様の方法を用いてマスク層10で覆われていたゲート電極7に異なる導電型の不純物を導入する。

(もっと読む)

半導体装置、半導体装置の製造方法、基板処理システムおよびプログラム

【課題】閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜30と、ゲート絶縁膜上に形成されたTiN膜41と、TiN膜41上に形成されたTiAlN膜43と、TiAlN膜43上に形成されたシリコン膜45と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ソース領域とドレイン領域間のリーク電流の発生が抑制された、LOCOS分離構造の半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体基板の上部の一部に互いに離間して形成された第1導電型のソース領域及びドレイン領域と、ソース領域とドレイン領域に挟まれた領域を含んで半導体基板上に配置されたゲート絶縁膜と、半導体基板上にゲート絶縁膜と連続して配置された、ゲート絶縁膜よりも膜厚の厚いLOCOS絶縁膜と、ゲート絶縁膜上及びゲート絶縁膜周囲のLOCOS絶縁膜上に渡り連続的に配置された多結晶シリコン膜からなるゲート電極とを備え、ゲート電極のチャネル幅方向の端部である周辺領域におけるゲート閾値電圧がゲート電極の中央領域におけるゲート閾値電圧よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】金属電極と該金属電極の上に形成されたシリコン電極とを有するゲート電極を備えた電界効果型トランジスタを実現する際に、金属電極とシリコン電極との界面に生じる界面抵抗を低減できるようにする。

【解決手段】半導体装置は、半導体基板100における第1の活性領域103aに形成されたP型の電界効果型トランジスタを備えている。第1の電界効果型トランジスタは、第1の活性領域103aの上に形成された第1のゲート絶縁膜106aと、第1のゲート絶縁膜106aの上に形成された第1のゲート電極115aとを有している。第1のゲート電極115aは、第1のゲート絶縁膜106aの上に形成された第1の金属電極107aと、該第1の金属電極107aの上に形成された第1の界面層110aと、該第1の界面層110aの上に形成された第1のシリコン電極111aとを有している。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、ゲート絶縁膜の一方の側のみに、容易に、かつ精度良く、バーズビークを形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】斜めイオン注入により、マスク膜にイオンを注入することで、シリコン酸化膜及びシリコン窒化膜を介して、ゲート絶縁膜の第1の側面と第1の不純物拡散領域の上面とで構成される角部に形成されたマスク膜のエッチング速度を、他の部分に形成されたマスク膜よりも速くし、次いで、ウエットエッチングにより、角部に形成されたマスク膜を選択的に除去して、シリコン窒化膜の表面の一部を露出させ、次いで、ウエットエッチングにより、マスク膜から露出されたシリコン窒化膜を選択的に除去して、シリコン酸化膜の表面の一部を露出させ、その後、熱酸化法により、ゲート絶縁膜の第1の側面側にバーズビークを形成する。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート閾値電圧を低下させることなく、チャネル移動度を向上できる炭化珪素MOSFETを提供する。

【解決手段】炭化珪素半導体装置200は、炭化珪素基板10と、炭化珪素基板10上に形成された炭化珪素層20と、炭化珪素層20上に形成されたゲート絶縁膜30と、ゲート絶縁膜30を介して炭化珪素層20上の所定位置に形成され、III族軽元素であるB、AlまたはGaをp型ドーパントとして含む多結晶シリコンからなるゲート電極40とを有する。そして、ゲート電極40中の上記p型ドーパントを、ゲート電極40直下の炭化珪素層20とゲート絶縁膜30との界面近傍に拡散させ、上記p型ドーパントによって界面近傍の不純物準位をパッシベーションする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

1 - 20 / 191

[ Back to top ]