Fターム[5F140BH01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 形状、配置 (1,748)

Fターム[5F140BH01]の下位に属するFターム

平面形状 (493)

断面形状 (1,038)

コンタクト部との関連 (60)

複数ドレイン (73)

複数ソース (72)

Fターム[5F140BH01]に分類される特許

1 - 12 / 12

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極GE2の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極GE2側に位置する側壁部において、第1の斜面と、第1の斜面と交差する第2の斜面と、を有する。このように、溝g2の形状をΣ形状とすることで、pチャネル型電界効果トランジスタのチャネル領域に加わる圧縮歪みを大きくすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性を向上させる。

【解決手段】本発明の半導体装置は、面方位が(110)のシリコン基板1と、pMIS領域1Bに形成されたpチャネル型電界効果トランジスタを有する。このpチャネル型電界効果トランジスタは、ゲート絶縁膜3を介して配置されたゲート電極GE2と、ゲート電極の両側のシリコン基板1中に設けられた溝g2の内部に配置され、Siより格子定数が大きいSiGeよりなるソース・ドレイン領域と、を有する。上記溝g2は、ゲート電極側に位置する側壁部において、面方位が(100)の第1の斜面と、第1の斜面と交差する面方位が(100)の第2の斜面と、を有する。上記構成によれば、基板の表面(110)面と(100)面とのなす角は45°となり、比較的鋭角に第1斜面が形成されるため、効果的にpチャネル型のMISFETのチャネル領域に圧縮歪みを印加することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

応力印加チャネル領域を有する電界効果トランジスタを備えた半導体構造の形成方法

半導体構造の製造方法は、第1トランジスタ素子および第2トランジスタ素子を有する半導体基板を提供するステップを有する。前記第1トランジスタ素子は少なくとも1つの第1アモルファス領域を含み、前記第2トランジスタ素子は少なくとも1つの第2アモルファス領域を含む。前記第1トランジスタ素子の上に応力発生層が形成される。前記応力発生層は、前記第2トランジスタ素子は覆わない。第1アニールプロセスが実施される。前記第1アニールプロセスは、前記第1アモルファス領域および前記第2アモルファス領域を再結晶化させるために適合されている。前記第1アニールプロセス後に、第2アニールプロセスが実施される。前記第2アニールプロセス中は、前記応力発生層が前記基板上に残されている。  (もっと読む)

(もっと読む)

ヘテロ構造を有する細長い単結晶ナノ構造に基づくトンネル効果トランジスタ

【課題】トンネル電界効果トランジスタ(TFET)は、金属酸化物電界効果トランジスタ(MOSFET)の後継者と考えられるが、シリコンベースのTFETは一般に低いオン電圧、トンネルバリアの大きな抵抗による欠点が問題となる。より高いオン電流を得るために、異なった半導体材料(例えばゲルマニウム(Ge))からなるヘテロ構造を備えた細長い単結晶ナノ構造ベースのTFETが用いられる。

【解決手段】TFETのソース(又は代わりにドレイン)領域として機能する、異なった半導体材料からなる細長い単結晶ナノ構造を導入する。ヘテロ部分の導入は、シリコンとゲルマニウムの間の格子不整合が高い欠陥界面とならないように行われる。従来のMOSFETに匹敵する、静的電力の低減と同様に動的電力の低減が行われる。細長い単結晶ナノ構造のSi/GeTFETによる超高密度オンチップトランジスタを用いた、多層の論理が期待される。

(もっと読む)

静電気放電保護素子および半導体装置

【課題】半導体集積回路のESD保護素子としての性能を向上させるとともに、ESD保護素子形成領域を小さくすることができる静電気放電保護素子を得ること。

【解決手段】半導体基板1上に形成されたゲート絶縁膜12、ゲート電極13およびサイドウォール膜14からなるゲート構造11と、ゲート構造11の両側に形成される高濃度不純物拡散層からなるソース領域15およびドレイン領域16と、ソース領域15とドレイン領域16のゲート構造11側に形成される低濃度不純物拡散層からなるエクステンション部17と、ソース電極と、ドレイン電極と、を備え、ゲート電極とソース電極が接地された複数の電界効果型トランジスタによって構成されるマルチフィンガタイプの静電気放電保護素子において、ソース電極とゲート電極13との間、およびドレイン電極とゲート電極13との間の高濃度不純物拡散層内に、低濃度不純物拡散層からなる抵抗領域18を備える。

(もっと読む)

半導体装置

【課題】サージに対して高い耐性を有すると共に、小型で安価な半導体装置を提供する。

【解決手段】半導体基板1に形成された各トランジスタセルTCのゲート電極に接続するゲート配線が、第1層間絶縁膜Z1を介して、各トランジスタセルTCを覆う2次元的に連結した面状のゲート配線層GHとして形成され、各トランジスタセルTCのドレインに接続するドレイン配線が、第2層間絶縁膜Z2を介して、ゲート配線層GHに対向する2次元的に連結した面状のドレイン配線層DHとして形成されてなる半導体装置100とする。

(もっと読む)

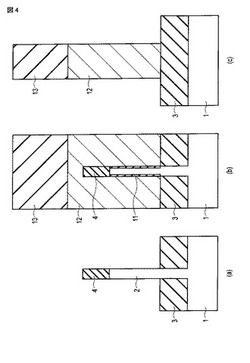

半導体装置の製造方法及び半導体装置

【課題】 自己整合的に基板のコンタクト部をユニバーサルコンタクトホール内に形成できる半導体装置の製造方法及びこれにより形成された半導体装置を提供する。

【解決手段】 層間絶縁膜12にユニバーサルコンタクトホール10開口し、サリサイド層7を除去して底面にソース領域3を露出させた後、ユニバーサルコンタクトホール10から半導体基板100に第1導電型(P型)不純物を注入して底面に露出するソース領域3を基板領域と同じ導電型の第1導電型領域5にする。ユニバーサルコンタクト16は、ユニバーサルコンタクトホール10の側面に露出するサリサイド層7を介してソース領域3に電気的に接続されている。基板領域とソース領域のコンタクトの位置関係が一定となりソース領域における電流の不均衡が解消される。

(もっと読む)

MOSトランジスタ

【課題】 メタル配線の抵抗成分をさらに低減し、システム電源デバイスの高出力・高効率化を実現できるとともにさらなる素子面積の縮小を図ることができるMOSトランジスタを提供する。

【解決手段】 ソース領域とドレイン領域とが格子状に形成されたゲートを挟んで互いに隣接するように形成されたMOSトランジスタにおいて、MOSトランジスタを半導体チップ上の角部に配置し、半導体チップ上の1つの角部の第1のチップエッジに隣接する領域に、ソース領域に接続されたソース側メタル配線が接続される第1のソースボンディングパッドとドレイン領域に接続されたドレイン側メタル配線が接続される第1のドレインボンディングパッドとを設け、角部の第2のチップエッジに隣接する領域に、ソース側メタル配線が接続される第2のソースボンディングパッドとドレイン側メタル配線が接続される第2のドレインボンディングパッドとを設ける。

(もっと読む)

半導体素子およびその製造方法

【課題】素子の微細化が可能でスイッチング性能の高い立体構造を有する電界効果型トランジスタである半導体素子を提供する。

【解決手段】ソース領域と、前記ソース領域の上部に配置された半導体機能層と及び、前記半導体機能層の上部に配置されたドレイン領域とを備え、前記半導体機能層は、前記ソース領域に対してほぼ垂直に配列した、複数の柱状あるいは円筒状の半導体物質からなる第1の部材と、前記第1の部材を取り囲み、前記ソース領域と絶縁体を介して配置された第2の部材から構成され、前記第2の部材はゲート領域と、絶縁体領域とから構成されており、前記第1の部材の平均直径が1nm以上30nm以下であり、前記第1の部材の平均間隔が3nm以上50nm以下であり、前記半導体層の酸素を除く主成分がシリコン、またはゲルマニウム、またはシリコンとゲルマニウムの混合物のいずれかである半導体素子を用いる。

(もっと読む)

半導体装置および半導体集積回路装置

pチャネルMOSトランジスタおよびnチャネルMOSトランジスタの各々においてチャネル方向を<100>方向に設定し、STI型素子分離構造に、引っ張り応力を蓄積した第1の応力補償膜を形成し、さらにシリコン基板上に素子分離構造を覆うように引っ張り応力を蓄積した第2の応力補償膜を形成する。 (もっと読む)

1 - 12 / 12

[ Back to top ]