Fターム[5F140BH15]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 不純物分布 (3,598) | 断面分布の形状、配置 (3,436) | 追加領域(エクステンション領域を含む) (3,054) | LDD(Lightly doped dorain−source) (1,105)

Fターム[5F140BH15]に分類される特許

161 - 180 / 1,105

半導体装置の製造方法

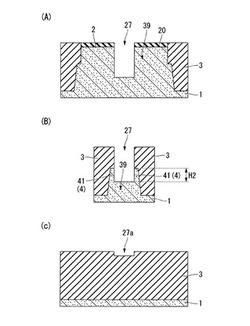

【課題】RC型トランジスタのチャネル領域の高さを所望の範囲に調整するとともに、前記チャネル領域に近接して残存する薄皮状のバリ部を完全に除去して、半導体装置を製造するという課題があった。

【解決手段】半導体基板1の一面に、溝部と、溝部に囲まれ、側壁面の少なくとも一部が傾斜面である凸部39とを形成してから、溝部を埋める素子分離用絶縁膜を形成する第1工程と、素子分離用絶縁膜をマスクの一部にして半導体基板1の一面をドライエッチングして凸部39内に凹部27を設けるとともに、凹部27と素子分離用絶縁膜との間にチャネル領域4となる薄肉部41を形成する第2工程と、ウェットエッチングにより、薄肉部41の高さを調整する第3工程と、を有する半導体装置の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜およびメタルゲート電極を有するMISFETを備えた半導体装置の信頼性向上を図る。

【解決手段】nチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとLaとOとを主成分として含有するHf含有絶縁膜4aを形成し、pチャネル型MISFET用の高誘電率ゲート絶縁膜としてHfとAlとOとを主成分として含有するHf含有絶縁膜4bを形成する。それから、金属膜7とシリコン膜8を形成し、これらをドライエッチングでパターニングしてゲート電極GE1,GE2を形成する。その後、ゲート電極GE1,GE2で覆われない部分のHf含有絶縁膜4a,4bをウェットエッチングで除去するが、この際、フッ酸を含有しない酸性溶液でのウェット処理とアルカリ性溶液でのウェット処理とを行ってから、フッ酸を含有する酸性溶液でのウェット処理を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法の提供。

【解決手段】相対的に薄いゲート絶縁膜25を有するMOSトランジスタが形成される領域のフィールド絶縁膜端23を相対的に厚いゲート絶縁膜24で覆うことにより、フィールド絶縁膜下部に形成された反転防止拡散層31から相対的に薄いゲート絶縁膜25を有するMOSトランジスタのチャネル領域33をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有する第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

半導体装置およびその製造方法

【課題】形成する素子に要求される素子間耐圧や素子内部耐圧に応じたディープトレンチ膜を有する半導体装置を提供する。

【解決手段】P型のシリコン基板11上に、N+型埋め込み層12と、N型半導体層13と、が積層された基板10と、基板10にN+型埋め込み層12の形成位置よりも深く形成され、基板10内の素子形成領域内を区画するディープトレンチ20と、ディープトレンチ20の内壁に沿って形成される側壁酸化膜23,24と、ディープトレンチ20内を埋めるTEOS膜を含むディープトレンチ膜26と、ディープトレンチ膜26で区画される素子形成領域に形成されるLDMOSと、を備え、ディープトレンチ20は、N+型埋め込み層12の上面よりも浅い位置の境界深さまでの第1のディープトレンチ21と、境界深さから底部までの第1のディープトレンチ21よりも小さい開口径を有する第2のディープトレンチ22によって構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】より高い耐熱性を有するシリサイド層を備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上にゲート絶縁膜4を介してゲート電極5を形成する工程と、半導体基板2上のゲート電極5の両側に、Ge含有領域8を形成する工程と、半導体基板2およびGe含有領域8のゲート電極5の両側の領域中に、ソース・ドレイン領域9を形成する工程と、Ge含有領域8上に、濃度5原子%以上のPdを含む金属シリサイドからなるシリサイド層11を形成する工程と、シリサイド層11を形成した後、半導体基板2に650〜750℃の熱処理を施す工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置

【課題】高耐圧で大きな電流駆動能力をもつLOCOSオフセット型MOS型電界効果トランジスタを提供する。

【解決手段】LOCOSオフセット型MOS型電界効果トランジスタのドレイン側のオフセット領域に、LOCOS酸化膜を伴うN型第1低濃度ドレインオフセット領域5と、LOCOS酸化膜を伴わないN型第2低濃度ドレインオフセット領域6を設け、共にゲート電極で覆うように設けたので、N型第1低濃度ドレインオフセット領域5でオフセット領域にかかる電界を緩和し高耐圧を得て、N型第2低濃度ドレインオフセット領域6でオフセット領域のキャリアを増加させ大きな電流駆動能力を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置

【課題】ドレイン端での電流集中を防止して静電放電に対する耐性に優れた半導体装置を提供する。

【解決手段】保護素子1は、MOS構造のデバイスの一部に、縦型バイポーラトランジスタQ1と寄生バイポーラトランジスタQ2とを形成した構造になっている。N+ドレイン領域3とゲート直下のチャネル領域4との間にはNドリフト領域5が形成されている。N+ソース領域6に隣接してP+ベースコンタクト領域7が形成されている。ソース側に縦型トランジスタQ1を形成して、静電放電時に発生したホール電流を縦型トランジスタQ1に流すようにしたため、N+ドレイン領域のベース側端部での電流集中を緩和できる。

(もっと読む)

リセスゲート構造を有する絶縁ゲート型炭化珪素ラテラル電界効果トランジスタ

【課題】短チャネル化を可能とし、オン抵抗と寄生容量の低減を図った絶縁ゲート型炭化珪素ラテラル電界効果トランジスタを提供する。

【解決手段】ドリフト領域(5)表面の一部に電界緩和領域(9)を設け、ソース領域(3)とドリフト領域(5)との間に凹部(リセス)(8)を形成したリセスゲート構造を有し、凹部(リセス)(8)底面の両端部近傍にソース領域(3)、ドリフト領域(5)の薄い領域(3a、5a)を設ける。

(もっと読む)

バンド設計超格子を有する半導体装置

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を提供する。

【解決手段】半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】p型MISトランジスタのゲート絶縁膜の酸化膜換算膜厚の厚膜化を抑制しつつ、p型MISトランジスタの実効仕事関数を増加させて、低閾値電圧を有するn型,p型MISトランジスタを実現する。

【解決手段】半導体装置は、第1,第2のMISトランジスタnTr,pTrを備えている。第1のMISトランジスタnTrは、第1の活性領域10a上に形成され、第1の高誘電率膜14Xaを有する第1のゲート絶縁膜14Aと、第1のゲート電極18Aとを備えている。第2のMISトランジスタpTrは、第2の活性領域10b上に形成され、第2の高誘電率膜14xを有する第2のゲート絶縁膜14Bと、第2のゲート電極18Bとを備えている。第2の高誘電率膜14xは、第1の調整用金属を含む。第1の高誘電率膜14Xaは、第2の高誘電率膜14xよりも窒素濃度が高く、且つ、第1の調整用金属を含まない。

(もっと読む)

半導体装置を製作する方法

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を製作する方法を提供する。

【解決手段】複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造過程において生じるウエハ外周部分からのパーティクルの発生を防止し、十分な歩留りを実現する。

【解決手段】ウエハにゲート電極となる導電膜4、5を形成する第一工程と、導電膜4、5の中の、ウエハの外周部分に形成された導電膜4、5の上に選択的に保護膜7を形成する第二工程と、導電膜4、5の上に第一レジストパターンを形成し、前記第一レジストパターンをマスクとして導電膜4、5をエッチングすることにより、ゲート電極を形成する第三工程と、前記ゲート電極を覆う層間絶縁膜を形成する第四工程と、前記層間絶縁膜の上に第二レジストパターンを形成し、前記第二レジストパターンをマスクとして前記層間絶縁膜をエッチングすることにより、コンタクトホールを形成する第五工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

半導体装置

【課題】高耐圧の電界効果トランジスタを有する半導体装置のキンク現象を抑制または防止する。

【解決手段】高耐圧pMISQHp1のチャネル領域のゲート幅方向の両端の溝型の分離部3と半導体基板1Sとの境界領域に、高耐圧pMISQHp1のソースおよびドレイン用のp+型の半導体領域P1,P1とは逆の導電型のn+型の半導体領域NVkを、高耐圧pMISQHp1の電界緩和機能を持つp−型の半導体領域PV1,PV1(特にドレイン側)に接しないように、そのp−型の半導体領域PV1,PV1から離れた位置に配置した。このn+型の半導体領域NVkは、溝型の分離部3よりも深い位置まで延在されている。

(もっと読む)

半導体装置

【課題】MOSトランジスタの高耐圧化、オン抵抗の低減、HCI耐性の向上、及びデザインルールの縮小を実現する。

【解決手段】MOSトランジスタのドレインは、チャネル長方向で一端がP型低濃度ウェル3内に配置され、他端がP型ウェル5内に配置されたN型低濃度ドレイン7と、低濃度ウェル3上の低濃度ドレイン7内に低濃度ドレイン7の端部とは間隔をもって配置されたN型高濃度ドレイン9からなる。ソースは、チャネル長方向で一端が低濃度ドレイン7とは間隔をもって低濃度ウェル3内に配置され、他端がウェル5内に配置されたN型高濃度ソース11と、低濃度ウェル3内で高濃度ソース11に隣接し、低濃度ドレイン7とは間隔をもって配置されたN型低濃度ソース13からなる。ゲート電極19は、高濃度ドレイン9−低濃度ソース13間の低濃度ウェル3上及び低濃度ドレイン7上に高濃度ドレイン9とは間隔をもって配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

161 - 180 / 1,105

[ Back to top ]