Fターム[5F140BK01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | LDD領域、エクステンション領域の形成 (1,808)

Fターム[5F140BK01]の下位に属するFターム

内側(低不純物)領域→外側(高不純物)領域 (1,620)

外側(高不純物)領域→内側(低不純物)領域 (104)

Fターム[5F140BK01]に分類される特許

1 - 20 / 84

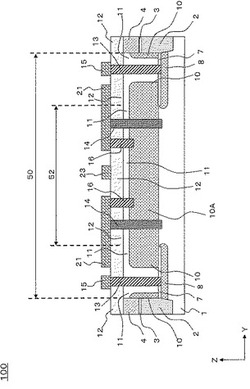

半導体装置およびその製造方法

【課題】同一平面上に形成された2つの配線が互いにショートするのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置する縦型のゲート電極用ダミーピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央に位置するゲート電極用ダミーピラー(1a)へ給電するために第1の方向(X)へ延在して配置されたゲート給電配線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつゲート給電配線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】強い圧縮応力を有するシリコン窒化膜を用いたpMISFETを有する半導体装置及びその製造方法において、歩留まりが高く且つスイッチングスピードが高い半導体装置及びその製造方法を提供する。

【解決手段】ボックスマーク102内においてシリコン基板1を覆うようにシリコン酸化膜14を形成する。次に、基板上の半導体領域にシリサイド化反応によりニッケルシリサイド8を形成する。その後、強い圧縮応力を有するシリコン窒化膜9をpMISFET101及びボックスマーク102を覆うように形成する。その上に層間絶縁膜11を形成した後レジストをパターニングしてコンタクトホール13を形成する。この際、重ね合わせ精度が所定の規格を満たすまで、レジストを一旦除去し再度レジスト12bを形成する。

(もっと読む)

絶縁ゲート型半導体装置及びその製造方法

【課題】 絶縁ゲート型半導体装置及びその製造方法に関し、炭化タンタル膜の仕事関数を適正に選択的に制御する。

【解決手段】 半導体基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に炭化タンタル膜を成膜する工程と、前記炭化タンタル膜の一部を露出する開口を有するマスクパターンを形成したのち、水素プラズマ処理を行う工程とを設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】極浅接合の深さが精密制御された半導体装置およびその製造方法を提供する。

【解決手段】主面が第1面方位である第1導電型の第1半導体層11と、第1半導体層11上に直接接合され、主面が第1面方位と異なる第2面方位である第1導電型の第2半導体層12と、第2半導体層12に連接して第1半導体層11上に形成され、主面が第1面方位である第3半導体層13a、13bと、第2半導体層12上にゲート絶縁膜を介して形成されたゲート電極15と、ゲート電極15をゲート長方向に挟むように第2半導体層12に形成され、第1半導体層11と第2半導体層12との接合面16に至る第2導電型の第1不純物拡散領域17a、17bと、第1不純物拡散領域17a、17bをゲート長方向に挟むように第3半導体層13a、13bから第1半導体層11の上部にかけて形成された第2導電型の第2不純物拡散領域18a、18bと、を具備する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体基板に欠陥が入るのを防止することを目的とする。

【解決手段】素子分離溝20aにより活性領域ARが画定されたシリコン基板20と、素子分離溝20a内に形成された素子分離絶縁膜23とを有し、素子分離絶縁膜23の上面が、活性領域ARにおけるシリコン基板20の上面よりも低い半導体装置による。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの特性が設計特性から離れることを抑制できる半導体装置を提供する。

【解決手段】この半導体装置は、チャネル形成領域180上に位置するゲート絶縁膜130及びゲート電極140と、トランジスタのソース及びドレインとして機能する2つの第2導電型高濃度不純物層170と、第2導電型高濃度不純物層170それぞれの周囲に設けられ、第2導電型高濃度不純物層170を深さ方向及びチャネル長方向に拡張し、第2導電型高濃度不純物層170より低濃度である2つの第2導電型低濃度不純物層160と、第2導電型低濃度不純物層160より下に位置し、素子分離膜120の下方を介してチャネル形成領域180の下方から素子分離膜120の外側まで延伸し、半導体層100より高濃度の第1導電型埋込層190を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタのゲート電極、及びp型MISトランジスタのゲート電極の双方を精度良く実現する。

【解決手段】第1のMISトランジスタと第2のMISトランジスタとを備えた半導体装置において、第1のMISトランジスタは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され、シリコン膜14aとシリコン膜14a上に形成された第1の金属シリサイド膜20aとからなる第1のゲート電極26aとを備え、第2のMISトランジスタは、半導体基板10における第2の活性領域10b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜13b上に形成され、フルシリサイド化された第2の金属シリサイド膜20Bからなる第2のゲート電極26bとを備え、第1の金属シリサイド膜20aは、第2の金属シリサイド膜20Bに比べて膜厚が薄い。

(もっと読む)

半導体装置

【課題】チャネル領域における高いキャリア移動度を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成され、内部におけるキャリアの移動度がSi結晶よりも大きい第1の結晶からなる半導体層と、前記半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層を挟んで形成され、前記半導体層に前記半導体層内のキャリアの移動度が上昇する方向に歪みを与える第2の結晶を含み、前記半導体層に接する深さの浅い領域であるソース・ドレインエクステンション領域を有するソース・ドレイン領域と、を有する。

(もっと読む)

熱処理装置及び方法、並びに半導体装置の製造方法

【課題】例えば表面に様々なパターンが形成される被処理体に適宜対応した正確な光反射率を得ることができ、この光反射率に基づいて被処理体の温度を所望に保持する熱処理を可能とする。

【解決手段】半導体基板の表面における実効吸収率を正確に求めるべく、当該実効吸収率の算出に用いる第1の光源による照射光強度の角度分布(角度強度分布)を、アニール処理に用いる第2の光源による角度強度分布に適合させる。このように第1の光源を第2の光源と同等のものとして、第1の光源の照射光の光照射角度に対する光強度分布に依存した半導体基板の表面における光反射率、即ち実効反射率を求める。

(もっと読む)

半導体装置の製造方法

【課題】従来の半導体装置の製造方法では、製造工程が多くなり、製造コストの増加につながる恐れがあった。

【解決手段】本発明の半導体装置の製造方法は、凸部形成領域と素子分離層形成領域とを有する基板を準備する工程と、基板の表面上に、凸部形成領域を覆うマスクパターンを形成する工程と、素子分離層形成領域をエッチングする第1エッチング工程と、凸部形成領域に第1不純物を注入する第1不純物注入工程と、素子分離層形成領域をエッチングすることにより、凸部形成領域に上面と側面とを有する凸部を形成する第2エッチング工程と、マスクパターンを除去する工程と、凸部に第1不純物と同型の第2不純物を注入する第2不純物注入工程と、凸部の上面と側面とにゲート絶縁膜を形成する工程と、凸部のゲート絶縁膜上にゲート電極を形成する工程と、を有している。

(もっと読む)

膜形成方法、半導体装置およびその製造方法

【課題】Vfbシフトと移動度低下を低減し、界面特性にすぐれたゲート絶縁膜構成を有する半導体装置を提供する。

【解決手段】シリコン基板を直接窒化して、シリコン窒化膜を形成し、前記シリコン窒化膜を、N2OとH2を含む混合ガスでアニールして、シリコン酸窒化(SiON)膜を形成する。このようなシリコン酸窒化膜は、半導体装置のゲート絶縁膜に適用することができる。

(もっと読む)

希王水の調整方法、及び半導体装置の製造方法

【課題】特に半導体装置の製造工程において、Pt及びPdの少なくとも一方を含む残留薄膜を簡易かつ効率的に除去することが可能な方法を提供する。

【解決手段】所定の容器中に、塩酸、硝酸及び水を順次に入れる、又は、硝酸、塩酸及び水を順次に入れて所定濃度の希王水を調整し、この希王水中に、製造過程にある半導体装置を浸漬し、前記半導体装置のPtを含む残留薄膜を除去する。

(もっと読む)

半導体装置とその製造方法

【課題】絶縁膜を研磨せずに、該絶縁膜からゲート電極の上面を露出させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板1の上にゲート絶縁膜5を形成する工程と、ゲート絶縁膜5の上にゲート電極7aを形成する工程と、ゲート電極7aを覆うように液状の絶縁性材料20を塗布する工程と、絶縁性材料20に鋳型100を押し当てることにより、ゲート電極7aの上方の絶縁性材料20を押し流す工程と、絶縁性材料20を硬化して絶縁膜21にする工程と、硬化の後、ゲート電極7a上に高融点金属膜を形成する工程と、高融点金属膜をアニールすることにより、ゲート電極7aの全体をシリサイド化する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリサイドの異常成長によるリーク電流の増加を抑制できる半導体装置を提供すること。

【解決手段】 半導体装置は、半導体基板100と、半導体基板100に形成されたMIS型FETであって、半導体基板100上に形成されたゲート絶縁膜106と、ゲート絶縁膜106上に形成されたゲート電極107と、前記MIS型FETのチャネル領域を挟むように形成され、半導体基板100とは格子間隔が異なり、かつ、高さが一定のSiC層103で構成されたソース/ドレイン層と、SiC層103の上面を含む領域上に形成され、かつ、前記チャネル領域には形成されていない金属シリサイド層110とを備えた前記MIS型FETとを具備している。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極の側壁絶縁膜のエッチングを効果的に防止することが可能な半導体装置を提供する。

【解決手段】 半導体基板11と、半導体基板上に形成されたゲート絶縁膜13と、ゲート絶縁膜上に形成されたゲート電極22と、ゲート電極の側面に形成された第1の絶縁膜17と、第1の絶縁膜の表面を覆い、第1の絶縁膜とは異なった材料で形成された第2の絶縁膜28と、半導体基板、ゲート電極及び第2の絶縁膜を覆い、第2の絶縁膜とは異なった材料で形成された第3の絶縁膜23とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜に用いられるLa−Hf−O膜系は、成膜時にシリコン基板との間に低誘電率層が出現し、これ排除する公知な技術による半導体装置及びその製造方法は提案されていなかった。

【解決手段】本発明に従う実施形態は、非晶質状態でSiが添加されたLa−Hf−O膜をゲート絶縁膜として用いる半導体装置及びその製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】NMOSFETおよびPMOSFETに適した組成のフルシリサイド相を、少ない工程数で、容易に得ることが可能な製造方法を提供すること。

【解決手段】基板1上に、ゲート絶縁膜2を介して前記NMOSFET用第1ゲート電極、およびPMOSFET用第2ゲート電極を形成する工程と、前記ゲート電極を覆う層間膜8を形成する工程と、前記層間膜8を平坦化し、前記第1、第2ゲート電極のシリコン層3を露出する工程と、前記第2ゲート電極の上部を選択的に除去する工程と、前記第2のゲート電極および第1のゲート電極のシリコン層3上に金属膜11を形成し、シリサイド化熱処理を行う工程と、熱処理工程後に未反応の金属膜を除去する工程と、を含み、第2のゲート電極上部を選択的に除去する工程の前に、前記第1および第2のゲート電極の各シリコン層3に、シリサイド相の組成制御のための不純物を同時に導入する工程を含む半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】トランジスタのサイズによらない普遍的な引っ張り歪みをnチャネル型MOSトランジスタに印加できる半導体装置を提供する。

【解決手段】nチャネル型MOSトランジスタのゲート絶縁膜として、高誘電率絶縁膜を使用し、この高誘電率絶縁膜を半導体基板上に界面層を介さず直接形成することにより、チャネル領域に引張り歪を与える。チャネル領域に圧縮歪を有するpチャネル型MOSトランジスタと組み合わせることにより、相補型の高性能半導体装置を構成できる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子の更なる微細化が進行することがあっても、シリサイドの突き抜けによる接合リークが発生することを防止する。

【解決手段】MISトランジスタを備えた半導体装置であって、MISトランジスタは、半導体基板100上における活性領域100aに形成されたゲート絶縁膜102と、ゲート絶縁膜102上に形成されたゲート電極103と、ゲート電極103の側面上に形成されたサイドウォール105と、活性領域100aにおけるサイドウォール105の側方下に位置する領域に形成されたソース・ドレイン領域106と、ソース・ドレイン領域106の上部にサイドウォール105と隣接して形成された第1のシリサイド層108aと、ソース・ドレイン領域106の上部に第1のシリサイド層108aと隣接して形成され、第1のシリサイド層108aの膜厚よりも厚い膜厚を有する第2のシリサイド層112Bとを備えている。

(もっと読む)

1 - 20 / 84

[ Back to top ]