Fターム[5F140BK11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域の形成 (4,176)

Fターム[5F140BK11]の下位に属するFターム

Fターム[5F140BK11]に分類される特許

1 - 20 / 46

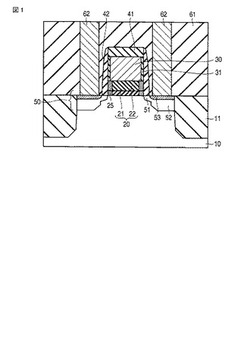

電界効果トランジスタ及びその製造方法

【課題】ゲート絶縁膜界面材料としてGeO2 を用いた場合においてもGeO2 層の劣化を抑制することができ、素子の信頼性向上をはかると共に、プロセスの歩留まり向上をはかる。

【解決手段】本発明の実施形態による電界効果トランジスタは、Geを含む基板10上の一部に設けられた、少なくともGeO2 層を含むゲート絶縁膜20と、ゲート絶縁膜20上に設けられたゲート電極30と、ゲート電極30下のチャネル領域を挟んで前記基板に設けられたソース/ドレイン領域50と、前記ゲート絶縁膜20の両側部に形成された窒素含有領域25と、を備えた。

(もっと読む)

半導体装置

【課題】半導体装置の大きさを大きくすることなく、増幅率の向上と、高耐圧化を図ることを課題とする。

【解決手段】基板上にドレイン部,ゲート部およびソース部が形成され、ゲート部は、基板上に形成されたゲート絶縁膜と、その上に形成されたゲート電極とからなり、ドレイン部は、ゲート電極の一方の端部に隣接した位置に設け、基板内部の表面近傍に形成された低濃度ドレイン領域と、より表面近傍に形成された中間濃度ドレイン領域と、基板の上の高濃度ドレイン領域とからなり、ソース部は、ゲート電極の他方の端部に隣接した位置に設け、基板内部の表面近傍に形成された低濃度ソース領域と、より表面近傍に形成された中間濃度ソース領域と、基板上の高濃度ソース領域とからなり、高濃度ソース領域は、ゲート電極の上方であって基板表面に平行な方向に延長されたアーム部を備え、アーム部の端部近傍の位置にコンタクト部を有する電極配線部を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

トランジスタ、半導体装置及びトランジスタの製造方法

【課題】トランジスタ素子内の電界を十分に緩和する。

【解決手段】表面に凸部12Aを有する半導体基板12と、凸部12Aの側壁部を構成し、凸部12Aの麓から頂上に向かって傾斜する傾斜部12Cと、凸部12Aの頂上にゲート絶縁膜14を介して形成されたゲート電極16と、凸部12Aの頂上で、ゲート電極16及び前記ゲート絶縁膜14の両側壁に形成されたサイドウォール18と、低濃度領域20A,22A及び高濃度領域20B,22Bをそれぞれ含むソース20及びドレイン22と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧性の維持と低オン抵抗化との両立が可能なLDMOSトランジスタを提供する。

【解決手段】半導体装置は、第1導電型のドリフト拡散領域10と、第2導電型のボディ拡散領域2と、第1導電型のソース拡散領域6と、ドリフト拡散領域10の上部に形成されたトレンチ内に埋め込まれ、ボディ拡散領域2とは離間した位置に形成された絶縁膜14と、ドリフト拡散領域10の上部に形成され、絶縁膜14から見てソース拡散領域6と逆の方向に隣接する第1導電型のドレイン拡散領域7と、ボディ拡散領域2上からドリフト拡散領域10上を越えて絶縁膜14上にまで形成されたゲート電極5とを備えている。また、ドリフト拡散領域10は、基板内部領域11と、基板内部領域11よりも高濃度の第1導電型不純物を含む表面領域12とを有している。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

高ゲルマニウム濃度のSiGeストレッサの形成方法

【課題】SiGeストレッサの形成方法と集積回路のトランジスタ構造を提供する。

【解決手段】SiGeストレッサを形成する方法であって、前記方法は、ソース領域とドレイン領域間にチャネルを有する半導体基板上のソース領域とドレイン領域の少なくとも1つに第1SiGe層を堆積するステップ、及び前記第1SiGe層の上部を酸化層に変換し、前記第1SiGe層の底部を第2SiGe層に変換するステップを含み、前記第2SiGe層は、前記第1SiGe層より高いGe濃度を有する方法。

(もっと読む)

低温炭素及び/又は分子炭素注入された歪み薄膜上の隆起型ソース/ドレインの形成

半導体構造のチャネル領域に引張応力を増大する方法が開示される。この方法は、1つ以上の低温炭素又は分子炭素イオン注入ステップを実行することを含み、炭素イオンを半導体構造中に注入して、チャネル領域の両側に歪み層を生成する。次に、隆起型ソース/ドレイン領域が歪み層上に形成され、続いて隆起型ソース/ドレイン領域をドープするためにイオン注入ステップが用いられる。ミリ秒アニールステップは、歪み層及び隆起型ソース/ドレイン領域を活性化する。歪み層は半導体構造のチャネル領域中のキャリア移動度を増大させる。一方、隆起型ソース/ドレイン領域は、隆起型ソース/ドレイン領域にその後ドーパントイオンを注入することによって引き起こされる、歪み層中のひずみの低減を最小化する。 (もっと読む)

半導体装置の製造方法

【課題】消費電力の少ない半導体装置の製造方法を提供する。

【解決手段】ゲート電極13の多結晶シリコン領域と、ゲート電極13下のチャネル領域11Cを挟んで配置された一対の単結晶シリコン領域11S,11Dとが形成されたシリコン基板11に対して、単結晶シリコン領域11S,11D上に単結晶のSiGe混晶層領域14A,14Bを成長させ、且つ多結晶シリコン領域13上に多結晶のSiGe混晶層領域14Cを成長させる工程と、Clを含むガスを用いて、一対の単結晶シリコン領域11S,11D上に成長したSiGe混晶層領域14A,14Bの表面側の一部を取り除くと共に、多結晶シリコン領域13上に成長したSiGe混晶層領域14Cを取り除く工程と、一対の単結晶シリコン領域上のSiGe混晶層領域14A,14B上に単結晶のシリコン層15A,15Bを成長させる工程と、シリコン層15A,15Bをシリサイド化する工程と、を有する。

(もっと読む)

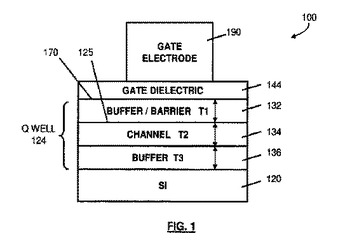

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】Si系基板上に結晶性の良いSi系結晶またはGe系結晶をエピタキシャル成長させることのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、水素ガス雰囲気中において、圧力が第1の圧力であり、温度が第1の温度である条件下で、シリコン窒化物からなる部材を備えたSi系基板の前記部材に覆われていない領域の自然酸化膜および付着したシリコン窒化物を除去する工程と、水素ガス雰囲気中において、圧力を前記第1の圧力に保持したまま、温度を前記第1の温度から第2の温度に下げる工程と、水素ガス雰囲気中において、温度を前記第2の温度に保持したまま、圧力を前記第1の圧力から第2の圧力に下げる工程と、圧力を前記第2の圧力に下げた後、水素ガス、およびSiおよびGeのうちの少なくともいずれか1つを含む前駆体ガス雰囲気中において、前記Si系基板の表面にSiおよびGeのうちの少なくともいずれか1つを含む結晶をエピタキシャル成長させる工程と、を含む。

(もっと読む)

チャネル領域への減少させられたオフセットを有する埋め込みSi/Ge材質を伴うトランジスタ

【解決手段】

非長方形形状を有していてよいキャビティに基いて歪誘起半導体合金を形成することができ、二酸化シリコン材質のような適切な保護層を設けることによって、非長方形形状は対応する高温処理の間にも維持され得る。その結果、歪誘起半導体材質の横方向のオフセットを小さくすることができる一方、キャビティエッチングプロセスの間に対応するオフセットスペーサの十分な厚みをもたらすことができるので、ゲート電極完全性を維持することができる。例えば、pチャネルトランジスタは六角形形状を伴うシリコン/ゲルマニウム合金を有することができ、それにより全体的な歪転移効率を顕著に高めることができる。

(もっと読む)

半導体装置

【課題】浅い不純物領域を有する半導体装置を提供する。

【解決手段】チャネル形成領域を含む半導体ならびにチャネル形成領域の上のフローティングゲート762およびコントロールゲート763によるゲート電極部752,753を含む半導体装置であって、ゲート電極部752,753の一方の側の半導体には、フローティングゲート762とオーバーラップする第1の不純物領域755が形成されており、フローティングゲート762の他方の側の半導体には、レーザドーピング処理により、深さが0.1μm以下で、且つフローティングゲート762とオーバーラップが無い第2の不純物領域757、758が形成されており、チャネル形成領域の長さは0.3μm以下である。

(もっと読む)

半導体装置

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になる第1の導電層6の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】

深さ方向の圧縮応力を印加して、NMOSトランジスタの性能を向上した半導体装置を提供する。

【解決手段】

CMOS型半導体装置用シリコン基板のNMOSトランジスタ領域、PMOSトランジスタ領域上方に多結晶シリコンのゲート電極を形成し、ゲート電極側壁上に第1サイドウォールスペーサを形成し、NMOSトランジスタ領域、PMOSトランジスタ領域に選択的にイオン注入を行ない、第1サイドウォールスペーサに整合した低抵抗ソース/ドレイン領域を形成する際、NMOSトランジスタ領域においてはゲート電極の上部をアモルファス化し、少なくともNMOSトランジスタ領域において第1サイドウォールスペーサを実質的に除去し、ゲート電極を覆ってキャップ膜を形成し、低抵抗ソース/ドレイン領域の活性化を行うと共にアモルファス化されたゲート電極の再結晶化を行う熱処理を行ない、キャップ膜を異方性エッチングして第2サイドウォールスペーサに加工する。

(もっと読む)

半導体装置の製造方法

【課題】歪み技術を利用した性能のよい半導体装置を低コストで製造する。

【解決手段】シリコン基板10上のnMOS形成領域12a及びpMOS形成領域12bにそれぞれゲート電極15a,15bを形成し、pMOS形成領域12bを覆い、フォトレジストマスク18を形成して、イオン注入によりnMOSのソース/ドレイン領域17aを形成するとともに、ゲート電極15aをアモルファス化し、フォトレジストマスク18を除去した後に、シリコン基板10上に、ゲート電極15a,15bを覆うように、引っ張り歪みを有するキャップ膜19を形成し、nMOS形成領域12aを覆うようにフォトレジストマスク20を形成し、pMOS形成領域12bのキャップ膜19に不純物をイオン注入し、フォトレジストマスク20を除去した後に、アニール処理を行い、nMOSのゲート電極15a下のチャネルに対し、チャネル深さ方向の圧縮歪みを加える。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

チャンネルに対して設計されたひずみを与えるストレッサー

【課題】チャネルに対して設計されたひずみを与えるストレッサー及びその形成方法を提供すること。

【解決手段】半導体基板が、異なる不純物濃度を有する異なる部分を有するヘテロエピタキシャル・シリコン含有物質で埋め込まれたリセスを備える。歪まされた膜が、リセスされたソース/ドレイン領域を、傾斜してボトム−アップで埋め込むことができる。膜は、所定の濃度のひずみを引き起こす不純物でリセス側壁をラインし、より低い濃度の不純物でリセスの残りの部分を埋め込む。後者の場合では、側壁ライナーは先細りになりえる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】超短チャネル長化でき、Si層厚一定によって閾値を変化させずにON電流を増加でき、さらにバックゲートにより閾値も動的に変更できる縦型トランジスタ構造を備えた半導体装置および半導体装置の製造方法を提供することを目的とする。

【解決手段】基板2上に、中心軸Mが基板2面と垂直方向に形成されてなる筒型の基柱3と、基柱3の上部と下部に、中心軸Mを中心とする同心形状に形成された第1導電型からなるソース・ドレイン拡散層4a,4bと、ソース・ドレイン拡散層4a,4bに挟まれた基柱3の中間部に形成された第1導電型からなるボディ層と、基柱3の側面にゲート絶縁膜6を介して形成されたフロントゲート電極7とを備えたことを特徴とする。また、第2導電型からなるバックゲート電極8が、基柱3の内側に上部から下部まで貫通する柱状に形成されてなることとする。

(もっと読む)

1 - 20 / 46

[ Back to top ]