Fターム[5F140BK19]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン領域形成後の処理 (2,202)

Fターム[5F140BK19]の下位に属するFターム

Fターム[5F140BK19]に分類される特許

1 - 20 / 41

半導体装置の製造方法

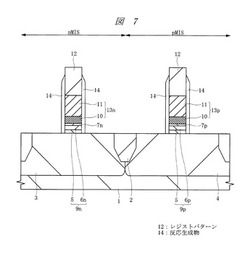

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体デバイスおよび半導体デバイスの製造方法

【課題】被処理体の所定領域に注入された、N型領域を形成する元素のイオンを、アニール処理の前後において被処理体の内部に維持し、所望のキャリア濃度のN型領域を形成することを可能とする、半導体デバイスの製造方法を提供する。

【解決手段】減圧雰囲気とした真空チャンバ内に、シリコンからなる被処理体101を配して、該真空チャンバ内に導入した、N型領域106Nを形成する元素Xを含むガスをプラズマ励起し、励起された該元素Xのイオンを、被処理体101の所定領域に注入する前工程と、該元素Xが注入された被処理体101をアニール処理する後工程と、を含み、該前工程と該後工程との間に、該真空チャンバ内に導入した酸素元素を含むガスをプラズマ励起し、励起された該酸素元素のラジカルに、該被処理体101の所定領域を曝露する工程を、さらに備えてなることを特徴とする半導体デバイスの製造方法。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

シリコンカーバイドから半導体構造体を製造する方法並びにシリコンカーバイド半導体

【課題】正確、均一かつ再現可能な構造化を可能にする、シリコンカーバイドから半導体構造を製造する方法を提供すること

【解決手段】上記の課題は、ポリシリコン層を基板上に被着するステップと、マスキングの構造を、前記ポリシリコン層内に移し、トレンチとインプランテーション領域との間に、ポリシリコンから成るスペーサーを設け、マスキングを除去し、基板を熱によって酸化させ、SIO2HTO層を析出し、インプランテーション領域をインプランテーションし、酸化物層を開放し、スペーサーを除去し、残余酸化物カバー並びに完全な酸化物を除去することを特徴とする方法

(もっと読む)

半導体装置の製造方法

【課題】バラツキの小さな高特性、高信頼性の半導体装置の製造方法を提供する。

【解決手段】ゲート電極の側壁に窒化膜サイドウォールを形成し、ウエットエッチングにより、ソース・ドレイン形成予定領域上のゲート酸化膜を除去することにより、窒化膜サイドウォール下方にアンダーカットが入るが、ゲート電極下方にはアンダーカットは入らない。これにより、ソース・ドレインのシート抵抗ばらつき増大を抑制し、また、シリコン基板にダメージを導入してしまうこともないため、接合リーク、しきい値ばらつき等の不具合を引き起こすことがない。

(もっと読む)

半導体装置の製造方法

【課題】不純物拡散領域の抵抗値のばらつきを抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体層にドーパント不純物を添加し、0.1秒〜10秒の活性化熱処理を行う。次いで、半導体層にイオン注入を行い、半導体層のドーパント不純物が添加された領域をアモルファス化する。次いで、0.1ミリ秒〜100ミリ秒の活性化熱処理を行い、アモルファス化した半導体層を再結晶化することにより、半導体層にドーパント不純物の拡散領域を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧性の維持と低オン抵抗化との両立が可能なLDMOSトランジスタを提供する。

【解決手段】半導体装置は、第1導電型のドリフト拡散領域10と、第2導電型のボディ拡散領域2と、第1導電型のソース拡散領域6と、ドリフト拡散領域10の上部に形成されたトレンチ内に埋め込まれ、ボディ拡散領域2とは離間した位置に形成された絶縁膜14と、ドリフト拡散領域10の上部に形成され、絶縁膜14から見てソース拡散領域6と逆の方向に隣接する第1導電型のドレイン拡散領域7と、ボディ拡散領域2上からドリフト拡散領域10上を越えて絶縁膜14上にまで形成されたゲート電極5とを備えている。また、ドリフト拡散領域10は、基板内部領域11と、基板内部領域11よりも高濃度の第1導電型不純物を含む表面領域12とを有している。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】特性を十分に向上することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、SiC膜11を形成する工程と、このSiC膜11の表面にSiを供給した状態で、このSiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。このようにすれば、Siを供給した状態でSiC膜11を熱処理することにより、SiC膜11をエネルギ的に安定な表面状態に再構成させることができる。その結果、一周期が100nm以上のファセットが得られ、ファセットの平坦部分の長さを従来に比べて長くすることができる。したがって、界面準位の密度を減少することによりキャリアの移動度を向上することができ、半導体装置の特性を十分に向上することができる。

(もっと読む)

自己整合損傷層を有するデバイス構造体の形成方法

【解決課題】 自己整合損傷層を有するデバイス構造体の形成方法を提供すること。

【解決手段】デバイス構造体は、基板の半導体材料内部に画定された第1導電型の第1及び第2ドープ領域を有する。逆の導電型の第3ドープ領域が、横方向に第1ドープ領域を第2ドープ領域から分離する。ゲート構造部が基板の上表面に配置され、第3ドープ領域と垂直方向で重なる関係を有する。第1結晶損傷層は基板の半導体材料の内部に画定される。第1結晶損傷層は、基板の半導体材料によって取り囲まれた第1の複数のボイドを有する。第1ドープ領域は、第1結晶損傷層と基板の上表面との垂直方向の間に配置される。第1結晶損傷層は横方向に第3ドープ領域内には延びない。

(もっと読む)

半導体装置の製造方法

【課題】逆短チャネル効果を抑制し、かつトランジスタのしきい値電圧を低下させることが可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置の製造方法は、窒素が上面内に注入されたp型の半導体領域2を有する下地1を準備し、この下地1上にゲート絶縁膜5およびゲート電極6をこの順で積層して形成する。次に、ゲート電極6をマスクとして、p型の一対のポケット注入領域7および当該ポケット注入領域7の外方にn型の一対のソース・ドレイン領域10を下地1の上面内に形成する。次に、下地1上を被覆してゲート絶縁膜5下の下地1に応力を印加する応力膜11を積層する。次に、下地1に熱処理を行い前記ソース・ドレイン領域10を活性化した後、積層した応力膜11を除去する。

(もっと読む)

半導体装置の製造方法

【課題】デバイスの性能や信頼性を低下させることなく、注入した不純物を熱処理することができる半導体装置の製造方法を提供する。

【解決手段】下地層であるpGaN層103に形成された注入領域104’上に、GaNのバンドギャップエネルギーよりも小さいバンドギャップエネルギーを有する物質よりなる光吸収膜T1を形成し、この状態で基板101上面から赤外光や赤色光など、pGaN層103のバンドギャップエネルギーよりも小さいエネルギーの所定光を用いてアニールを行う。pGaN層103と比較して光吸収膜T1の方がアニールで使用される光の吸収係数が大きいため、光吸収膜T1直下もしくは近傍の領域(注入領域104’)を選択的に熱処理することが可能となる。

(もっと読む)

マスク無しの選択的なボロン添加されたエピタキシャル成長

【課題】p型MOSFET領域とn型MOSFET領域とで、選択的にシリコン・ゲルマニウム層を形成する。

【解決手段】シリコン層のpウェル上に第1導電層が形成され、シリコン層のnウェル上に第2導電層が形成される。pウェルおよびnウェルの両方にフッ素イオンが注入される。pウェルおよびnウェルの両方が水酸化アンモニウムおよび過酸化物に晒される。シリコン層上にボロン添加されたシリコン・ゲルマニウム層をエピタキシャル成長させる。

(もっと読む)

半導体装置の製造方法

【課題】レジスト膜をアッシングにより除去する際に、イオン注入による変質層のポッピングを防止できるとともに、半導体基板の酸化や掘れを抑制できる半導体装置の製造方法を提供する。

【解決手段】表面に変質層が形成されたレジスト膜を有する半導体基板を、処理チャンバ内に搬入するステップと、半導体基板を加熱するとともに、処理チャンバ内に不活性ガスを導入して処理チャンバ内の圧力を上げるステップと、次いで、処理チャンバ内に酸素ガスを導入し、酸素ガスのプラズマによってレジスト膜をアッシングするステップとを有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、光吸収膜を利用して実行する新たな製造方法を提供する。

【解決手段】基板上に光吸収膜を堆積し、前記光吸収膜を加工して、第1の膜厚の前記光吸収膜で覆われた第1領域と、前記第1の膜厚よりも薄い第2の膜厚の前記光吸収膜で覆われた第2領域と、前記第2の膜厚よりも薄い第3の膜厚の前記光吸収膜で覆われた第3領域とを形成し、前記基板に光を照射することにより、前記基板をアニールすることを特徴とする半導体装置の製造方法。

(もっと読む)

動的表面アニール処理のための吸収層

【課題】複数のデバイスを含む基板に対し、電磁放射線によるアニール中に基板の表面全体に一様な加熱を実施する方法を提供する。

【解決手段】基板300上にアモルファス炭素を含む層312を堆積させるステップと、その後、該層312を少なくとも約300℃の温度に加熱するのに十分な条件下で該基板300を約600nm〜約1000nmの波長を1つ以上もつ電磁放射線にさらすステップと、を含む前記方法が提供される。任意に、前記アモルファス炭素を含む層312は、窒素、ホウ素、リン、フッ素、及びそれらの組合わせからなる群より選ばれたドーパントを更に含んでいる。一態様においては、前記アモルファス炭素を含む層312は、反射防止コーティングと、電磁放射線を吸収し且つ基板300の最上面をアニールする吸収層である。一態様においては、基板300はレーザアニールプロセスにおいて電磁放射線にさらされる。

(もっと読む)

半導体装置の製造方法

【課題】 接合深さに起因する特性のバラツキを抑制可能な、極浅不純物拡散領域を有する半導体装置の製造方法を提供する。

【解決手段】 半導体基板面11にゲート酸化膜12、ゲート電極13、保護絶縁膜14を順次形成した後、不純物注入を行い、極浅不純物拡散領域18を形成後、極浅不純物拡散領域18上に、半導体基板11の不純物拡散係数以上の不純物拡散係数を有する半導体材料膜21を成膜する。その後、アニール処理を行って、前記極浅不純物拡散領域を活性化して極浅接合を形成する。

(もっと読む)

処理装置、トランジスタ製造方法

【課題】SiC中のSi欠損を発生させずにSiC基板の不純物層をアニールする技術を提供する。

【解決手段】本発明の処理装置10は、搬送室11と、高温熱処理室12と、前処理装置13を有している。処理対象物70は前処理装置13内の加熱装置22により加熱され、SiC基板71表面に形成された有機膜74は焼成され、SiC基板71表面には炭素皮膜76が形成される。炭素皮膜76が形成されたSiC基板71は高温熱処理装置12のアニール室40内において高温に加熱され、アニールされる。SiC基板71表面には炭素皮膜76が配置されているから、SiC基板71からのSiの欠損が生じない状態で不純物層をアニールすることが可能である。

(もっと読む)

1 - 20 / 41

[ Back to top ]