Fターム[5F140BK29]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400) | PVD (795)

Fターム[5F140BK29]に分類される特許

1 - 20 / 795

半導体装置の製造方法

化合物半導体装置及びその製造方法

電界効果トランジスタ

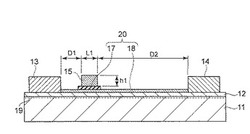

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

保護素子、半導体装置及び半導体装置の製造方法

【課題】ヘテロ接合を利用した新規な保護素子を提供すること。

【解決手段】 半導体装置10の保護部36は、配線下層11Bと、配線下層11Bとは異なるバンドギャップを有する配線上層13を有している。配線上層13は、第1部位41と中間部位43と第2部位45を含んでいる。配線上層13と配線下層11Bの接合面に形成される2次元電子ガス層が、第1部位41と中間部位43の間で分離されており、第2部位45と中間部位43の間で分離されている。第1部位41と配線下層11Bの接合面に形成される2次元電子ガスが、ドレイン電極21に電気的に接続されている。第2部位45と配線下層11Bの接合面に形成される2次元電子ガスが、ソース電極28に電気的に接続されている。中間部位43と配線下層11Bの接合面に形成される2次元電子ガスが、ゲート電極25に電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】オン時における電流の迅速な立ち上がりを実現し、複雑な工程を経ることなく、n型HEMTとモノリシックにインバータを構成可能な半導体装置を得る。

【解決手段】第1の極性の電荷(ホール)供給層22aと、電荷供給層22aの上方に形成されており、凹部22baを有する第2の極性の電荷(ホール)走行層22bと、電荷走行層22bの上方で凹部22baに形成されたゲート電極29とを含むp型GaNトランジスタを備える。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ドレイン−ソース間のリーク電流が少なく、かつ、ノーマリーオフの半導体装置を提供する。

【解決手段】基板11の上に形成された不純物元素を含む第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層16と、第2の半導体層16の上に形成された第3の半導体層17と、第3の半導体層17の上に形成されたゲート電極21、ソース電極22及びドレイン電極23と、を有し、第2の半導体層16において、ゲート電極21の直下には、第1の半導体層13と接し、第1の半導体層13に含まれる不純物元素が拡散している不純物拡散領域15が形成されており、不純物元素は、不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

グラフェンを含む電極構造体及び電界効果トランジスタ

【課題】グラフェンを含む電極構造体及び電界効果トランジスタを提供する。

【解決手段】半導体層上のグラフェンと、グラフェン上の電極メタルと、を備え、該グラフェンは、半導体層と直接的に接触し、電極メタルは、グラフェンと直接的に接触する電極構造体である。半導体層は、シリコン、ゲルマニウム、シリコン・ゲルマニウム、III−V族半導体、及びII−VI族半導体を含むグループから選択された一つで形成される。グラフェンは、単層または二層のグラフェンで形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 寄生ダイオードの逆回復時間を短縮でき、スイッチング損失の低減が図れるLDMOSトランジスタを低コストで提供する。

【解決手段】 LDMOSトランジスタT1が、p型半導体基板1内にp型ボディ領域2とp型埋め込み拡散領域3とn型ドリフト領域6を、ボディ領域2内にn型ソースコンタクト領域4とp型ボディコンタクト領域5を、ドリフト領域6内にn型ドレインコンタクト領域7を、ソースコンタクト領域7とドリフト領域6間のボディ領域2の上方にゲート絶縁膜8を、ゲート絶縁膜8上にゲート電極9を夫々備えて形成され、ドリフト領域6とボディ領域2は相互に接触し、埋め込み拡散領域3が、ボディ領域2の底面と接触するボディ領域2よりも深い位置に、半導体基板1の表面に平行な方向に、少なくともボディ領域2からドレインコンタクト領域7のボディ領域2から最も離間した遠方端の下方まで延在している。

(もっと読む)

1 - 20 / 795

[ Back to top ]