Fターム[5F140BK33]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極の形成 (2,400) | 熱処理 (1,281)

Fターム[5F140BK33]の下位に属するFターム

シリサイド化 (1,222)

Fターム[5F140BK33]に分類される特許

1 - 20 / 59

化合物半導体装置及びその製造方法

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

化合物半導体装置の製造方法、基板評価装置及び基板評価方法

【課題】化合物半導体層を形成する前の基板の状態で非接触のスクリーニングを行うことで、事前に化合物半導体層の不良発生を認識してこれを防止することができ、歩留まりの向上及び製造コストの削減を可能とする信頼性の高い化合物半導体装置を得る。

【解決手段】偏光レーザ12によりSiC基板1の基板面に偏光レーザ光を照射し、検出部13によりSiC基板1からの発光を検出し、表示部14によりSiC基板1の発光強度の面内分布を得て、SiC基板1の窒素混入量を評価した後、SiC基板1の上方に化合物半導体積層構造2を形成する。

(もっと読む)

半導体装置

【課題】ノーマリオフで動作するとともに、高い耐圧と低いオン抵抗を具備した半導体装置を提供すること。

【解決手段】 半導体装置1では、ドレイン電極21が第1ヘテロ接合面32に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ソース電極29が第1ヘテロ接合面32に形成される2次元電子ガス層から電気的に絶縁可能に構成されているとともに第2ヘテロ接合面34に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ゲート部28が第2ヘテロ接合面34に対向しており、導通電極25が第1ヘテロ接合面32及び第2ヘテロ接合面34に形成される2次元電子ガス層の双方に対して電気的に接続可能に構成されている。第1ヘテロ接合面32に形成される2次元電子ガス層の電子濃度は、第2ヘテロ接合面34に形成される2次元電子ガス層の電子濃度よりも濃い。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】GaとSiとの反応を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、Si基板1と、Si基板1の表面に形成されたSi酸化層3と、Si酸化層3上に形成され、Si酸化層3の一部を露出する核形成層2と、Si酸化層3及び核形成層2上に形成された化合物半導体積層構造9と、が設けられている。

(もっと読む)

電界効果トランジスタ

【課題】高耐圧性をより確実に実現することができる電界効果トランジスタを提供すること。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成されたキャリア走行層と、前記キャリア走行層上に形成され、前記キャリア走行層とは反対の導電型を有し、前記キャリア走行層内部に到る深さまで形成されたリセス部によって分離したキャリア供給層と、前記分離した各キャリア供給層上に前記リセス部を挟んで形成されたソース電極およびドレイン電極と、前記分離した各キャリア供給層上にわたって前記リセス部内における前記キャリア走行層の表面を覆うように形成されたゲート絶縁膜と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極と、を備え、前記リセス部の前記キャリア供給層上面からの深さが、前記キャリア供給層の層厚より大きく200nm以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接するトランジスタ間において、各々のゲート電極の電圧変化の影響が相互に及ばないようにする。

【解決手段】基板100内の素子分離領域220で囲まれた活性領域と、活性領域内に形成された埋め込みゲート電極410a、410bと、埋め込みゲート電極410a、410bの間に設けられ、かつ埋め込みゲート電極410a、410bの底部の深さまで形成された拡散層領域320を有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

半導体装置、半導体装置の製造方法、および試験装置

【課題】ゲートリーク電流が少なく、かつ電流コラプスが抑えられた半導体装置の提供。

【解決手段】第1の態様においては、窒化物系半導体で形成された半導体層110と、半導体層上に開口を有して設けられ、タンタル酸窒化物を含む第1絶縁膜120と、第1絶縁膜の開口において半導体層上に積層された第2絶縁膜130と、第2絶縁膜上に設けられたゲート電極140と、を備える半導体装置を提供する。ここで、第2絶縁膜は、第1絶縁膜より絶縁性が高い絶縁膜により構成される。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ピンチオフ特性を維持しながら動作効率を向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板11と、基板11上方に形成された電子走行層12と、電子走行層12上方に形成された電子供給層13と、電子供給層13上方に形成されたソース電極15s及びドレイン電極15dと、電子供給層13上方で、ソース電極15s及びドレイン電極15dの間に形成された第1のゲート電極15g−1及び第2のゲート電極15g−2と、が設けられている。ゲート電極15g−1の仕事関数は、第2のゲート電極15g−2の仕事関数よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】チャネル領域に歪みを加える領域内の格子位置に存在する炭素量を多くすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板のうちゲート電極5両側にエクステンション領域7s、7d、ポケット領域8s、8dを形成し、ゲート電極5側面にサイドウォール9を形成し、半導体基板1のうちサイドウォール9、ゲート電極5から露出した領域をエッチングして凹部1s、1dを形成し、凹部1s、1d内に第3不純物を含む半導体層11s,11dを形成し、第1熱処理により第3不純物を活性化してゲート電極5の両側方にソース/ドレイン領域11s,11dを形成し、半導体層11s,11d内に炭素を有する第4不純物をイオン注入して半導体層11s,11dをアモルファス領域13s,13dとなし、第2熱処理によりアモルファス領域13s,13d内結晶の格子位置での炭素の結合性を高めてゲート電極5の両側方に歪発生領域14s,14dを形成する工程を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜を有する窒化物半導体を低コストで製造する。

【解決手段】基板10の上方に形成された半導体層22,23,24と、前記半導体層の一部を酸化することにより形成された絶縁膜30と、前記絶縁膜上に形成された電極41と、を有し、前記絶縁膜は、酸化ガリウムを含むもの、または、酸化ガリウム及び酸化インジウムを含むものにより形成されているものであることを特徴とする半導体装置。

(もっと読む)

電界効果型トランジスター

【課題】ダイヤモンドFETにおいて、ドレイン電流特性を改善すること。

【解決手段】ダイヤモンド結晶層1の上に、高濃度ホウ素ドープダイヤモンド薄膜層102を成長する(図1(a))。次に、ソース電極およびドレイン電極として、Ti層131A、131B、Au層132A、132Bを順に蒸着する(図1(b))。次に、400℃でアニールを行いTiをダイヤモンドと反応させて、TiC層133A、133Bを形成する(図1(c))。最後に、ゲート部にAl2O3膜141を形成し、その上にAlゲート電極42を蒸着する(図1(d))。作製したダイヤモンドFETのドレイン電流特性は、ゲート電圧−3Vにおける最大ドレイン電流密度が600mA/mmとなり、従来技術による場合の約6倍に増加した。温度依存性に関しては、従来技術では室温から150℃付近でドレイン電流密度は急激に減少したが、本発明では900℃まで安定して動作した。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート絶縁膜における電荷トラップを大幅に低減し、信頼性の高い化合物半導体装置を実現する。

【解決手段】化合物半導体層2と、化合物半導体層2上でゲート絶縁膜6を介して形成されたゲート電極7とを備えており、ゲート絶縁膜6は、SixNyを絶縁材料として含有しており、SixNyは、0.638≦x/y≦0.863であり、水素終端基濃度が2×1022/cm3以上5×1022/cm3以下の範囲内の値とされたものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】絶縁膜上に保護膜を形成した構造において、絶縁耐圧の低下を防ぐ。

【解決手段】基板上に形成された第1の半導体層と、前記第1の半導体層上に形成された第2の半導体層と、前記第2の半導体層上に形成されたソース電極及びドレイン電極と、前記第2の半導体層上に形成された絶縁膜と、前記絶縁膜上に形成されたゲート電極と、前記絶縁膜を覆うように形成された保護膜と、を有し、前記保護膜は、熱CVD、熱ALD、真空蒸着のいずれかにより形成されたものであることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体デバイス、その製造方法及び集積回路

【課題】電極領域の抵抗を従来よりも一段と低減させることができる半導体デバイス、その製造方法及び集積回路を提供する。

【解決手段】III−V族化合物半導体層4上にニッケル層17を形成し、RTA処理により加熱することで、ニッケルIII−V族合金(Ni-InxGa1-xAsyP1-y合金)からなるソース領域5及びドレイン領域6が形成される。これにより、MOSFET1では、III−V族化合物半導体層4に対して単に不純物をインプラテーションで注入して形成された従来のソース領域及びドレイン領域の寄生抵抗に比べて、ソース領域5及びドレイン領域6の寄生抵抗を一段と低減させることができる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】チャネル移動度と閾値電圧とのトレードオフの関係を打破し、チャネル移動度を向上させ、かつ、閾値電圧の低下を抑えた炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】この発明に係る炭化珪素半導体装置1aの製造方法は、炭化珪素エピタキシャル層6を有する炭化珪素基板2の炭化珪素エピタキシャル層6上に、リンをドープした多結晶珪素膜18を形成する工程と、多結晶珪素膜18を熱酸化してゲート絶縁膜12を形成する工程と、を備えた。

(もっと読む)

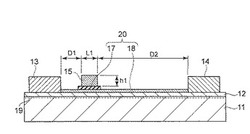

ノーマリオフ型GaN系電界効果トランジスタ

【課題】ゲート耐電圧が高くかつオン抵抗が低減されたノーマリオフ型GaN系FETを提供する。

【解決手段】ノーマリオフ型GaN系FETは、第1種GaN系半導体からなるチャネル層4と、このチャネル層上で互いに隔てて設けられた第2種GaN系半導体からなる一対の電子供給層5と、これら電子供給層の間でチャネル層を覆うゲート絶縁膜7と、チャネル層にオーミックコンタクトしているソース電極およびドレイン電極と、ゲート絶縁膜上に形成されたゲート電極とを備え、ゲート絶縁膜はチャネル層上に順次堆積された第1と第2の絶縁層を含み、第1絶縁層7aはSiの酸化物、窒化物および酸窒化物のいずれかからなりかつ5nm以下の厚さを有し、第2絶縁層7bは第1絶縁層に比べて大きなε×Ecを有し、ここでεは誘電率を表し、Ecは絶縁破壊電界を表している。

(もっと読む)

1 - 20 / 59

[ Back to top ]