Fターム[5F140BK39]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | ソース・ドレイン電極形成後の処理 (1,157) | エッチング (743)

Fターム[5F140BK39]に分類される特許

1 - 20 / 743

半導体装置およびその製造方法

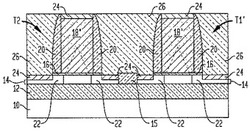

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置の製造方法

【課題】縦型トランジスタのソース又はドレイン用の拡散層を形成するにあたって形成されるシリコン膜に表面凹凸を発生させない半導体装置の製造方法を提供する。

【解決手段】複数の半導体ピラーを形成する工程と、隣り合う前記半導体ピラーで挟まれた溝の側面を覆うように絶縁膜を形成する工程と、前記絶縁膜の前記溝の底部に近い領域に側面開口を形成する工程と、前記溝の内部を覆うようにシリコン膜からなる被覆膜を形成する工程と、前記被覆膜上に前記半導体ピラー内へ拡散させる不純物で構成された不純物層を形成する工程と、前記不純物を、前記側面開口を塞ぐように形成されている前記被覆膜を通して前記半導体ピラー内に熱拡散させてソース又はドレイン用の拡散層を形成する工程と、を含む。前記被覆膜の成膜温度を510℃より高く度550℃未満の範囲とすることにより、非晶質状態のシリコン膜を形成する。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの特性のばらつきを低減するために有利な技術を提供する。

【解決手段】MOSトランジスタを含む半導体装置の製造方法は、半導体基板の上に形成された第1絶縁膜の上にゲート電極材料層を形成する工程と、前記ゲート電極材料層の上にエッチングマスクを形成する工程と、前記ゲート電極材料層をパターニングすることによりゲート電極を形成する工程と、前記ゲート電極が形成された前記半導体基板の上に第2絶縁膜を形成する工程とを含み、前記ゲート電極を形成する工程では、前記ゲート電極材料層がパターニングされるとともに、少なくとも、前記ゲート電極の側面の下部と、前記第1絶縁膜のうち前記側面に隣接する部分とを保護する保護膜が形成され、前記第2絶縁膜を形成する工程では、前記保護膜を覆うように前記第2絶縁膜が形成される。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】ノーマリオフ型のHEMT構造を有し、かつ優れたデバイス特性を有する窒化物半導体装置およびその製造方法を提供する。

【解決手段】窒化物半導体装置は、窒化物半導体からなる電子走行層3と、電子走行層3に積層され、電子走行層3とはAl組成が異なり、Alを含む窒化物半導体からなる電子供給層4と、電子供給層4と電子走行層3との界面に連続する界面を有し、電子走行層3上に形成された酸化膜11と、酸化膜11を挟んで電子走行層3に対向するゲート電極8とを含む。

(もっと読む)

半導体装置の製造方法

【課題】レジストパターンの下地層への悪影響を及ぼすことなくスカムを最適に除去する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上に酸化膜5cを形成し、前記酸化膜5c上にフォトレジスト8を塗布し、前記フォトレジスト8を露光し、露光された前記フォトレジスト8を現像することにより前記フォトレジス8トに開口部8aを形成し、前記フォトレジスト8をマスクとして、前記酸化膜5cを酸素プラズマ処理し、前記酸素プラズマ処理の後、前記酸化膜5cと前記フォトレジスト8に希釈フッ酸を供給し、前記希釈フッ酸を供給する工程の後、前記フォトレジスト8をマスクとして前記酸化膜5cを通して記半導体基板1に一導電型不純物をイオン注入する工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体装置の製造方法

【課題】寄生抵抗が低く、接合リーク電流が抑制されたトランジスタを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】実施形態にかかる半導体装置の製造方法は、シリコン基板中のチャネル領域上にゲート絶縁膜を介してゲート電極を形成し、シリコン基板に所望の不純物を注入することにより、チャネル方向に沿ってチャネル領域を挟むようにシリコン基板中にソース領域とドレイン領域とを形成し、ソース領域及びドレイン領域の表面をアモルファス化することにより、それぞれの表面に不純物を含むアモルファス領域を形成し、アモルファス領域の上にニッケル膜を形成し、マイクロ波を照射して、アモルファス領域とニッケル膜とを反応させてニッケルシリサイド膜を形成しつつ、アモルファス領域を固相成長させてアモルファス領域に含まれる不純物を活性化し、未反応のニッケル膜を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体基板製品の製造方法、これに用いられる薄膜除去液

【課題】白金(Pt)化合物の薄膜を、他の部材を過度に酸化・腐食することなしに除去する半導体基板製品の製造方法、これに用いられる薄膜除去液を提供する。

【解決手段】白金化合物の薄膜を有する半導体基板を準備する工程と、薄膜除去液を準備する工程と、前記半導体基板に前記薄膜除去液を適用して前記白金化合物の薄膜を除去する工程とを含む半導体基板製品の製造方法であって、前記薄膜除去液が、ハロゲン分子、ハロゲンイオン、及び水を組み合わせて含む半導体基板製品の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

1 - 20 / 743

[ Back to top ]